Académique Documents

Professionnel Documents

Culture Documents

Devoir de Synthèse N°1 - Génie Électrique - Bac Technique (2011-2012) MR Raouafi Abdallah

Transféré par

Fethi BenmassoudeTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Devoir de Synthèse N°1 - Génie Électrique - Bac Technique (2011-2012) MR Raouafi Abdallah

Transféré par

Fethi BenmassoudeDroits d'auteur :

Formats disponibles

19

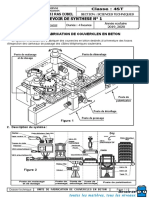

Devoir de synthèse N°1 Prof : Mr Raouafi Abdallah

Nom & Prénom : ……………………….…………………..…………………

Lycée Feriana

Note:

Classe : ………………… G: ……. N°: ………

20

B- PARTIE GENIE ELECTRIQUE :

I. Etude de la commande du moteur Mt:(7.5 points)

En se référant au dossier technique page (3/6) :

1. Déterminer le GRAFCET PC puis traduire en GRAFCET codé automate AEG.

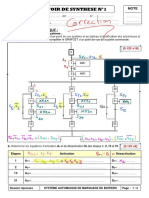

GRAFCET PC GRAFCET codé AEG

1 pt 1 pt

00 ……………… 0 ………………

…..

………………….. …..

…………………..

11 ………….… …….….. 1 ………….… …….…..

…………… ……………

…… …….. …… ……..

2

2 ……………… 2 ………………

…… ……

….. …..

…… ……

….. …………… ….. I5

……..

33 VR ..…….. 3 ………… …..…..

…………… ……………

…….. ……..

2. Traduire le GRAFCET codé automate en un programme écrit en liste

d’instructions (IL) relatives à l’automate AEG_020.

Cir Instructions Cir Instructions Cir Instructions Cir Instructions

1 1 : AM 128 ……………….. ……………….. ………………..

2 : …………….. ……………….. ……………….. ………………..

3 : AM 128 ……………….. 25 : ………….. ………………..

4 : RLM 128 ……………….. ……………….. ………………..

3 5 : …………….. ……………….. ……………….. ………………..

6 : …………….. ……………….. ……………….. ………………..

7 : …………….. ……………….. 29 : SLM 10 ………………..

8 : …………….. ……………….. ……………….. 41: = Q5

9 : AM 30 ……………….. ……………….. 16 ………………..

…………..…….. 21 : RLM 30 12 32 : AM 40

4.5 pt

…………..…….. ………….…….. …………….…..

DOSSIER PEDAGOGIQUE 2011-2012 Page 5/8

3. Donner le programme relatif au GRAFCET codé API en langage LD (M20 et M40).

Activation étapes Désactivation étapes Sorties 1 pt

Activation étapes

Activation étapes

Désactivation étapes

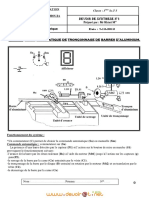

II. Etude et réalisation d’un additionneur BCD:(6.5 points)

Soit le montage représenté par le schéma ci-après, on applique à l’entrée du circuit les

nombres BCD [A]=[a4a3a2a1] et [B]=[b4b3b2b1] et on relève à la sortie le nombre

[S’]=[S’4S’3S’2S’1]. Dans cette solution, le circuit de détection d’erreur est représenté par

un comparateur de deux nombres Y et Z de cinq bits.

b4 b3 b2 b1 a4 a3 a2 a1

C4 0 - Complet – N°1 ) a0

(aAd C0 = 0

74 HC 283

a0 S4 S3 a0S2 S1

+5v

a0 Z a0

Y Comparateur

a0 a0

X

( Ad - Complet – N°2 )

Circuit de détection d’erreur C’0 = 0

1 74 HC 283

C’4

S’4 S’3 S’2 S’1

1. On prendre le circuit additionneur binaire 74HC283, ce dernier capable d’exécuter

l’addition en binaire des deux nombres A et B à 4 bits. a

0

a. Compléter la table de vérité corresponde à un additionneur élémentaire à 1 bit.

0.75 pt

H.A : Half Adder : demi-additionneur.

a b S1 R1 a0

0 0 S2 S1 a

…. …. S

0 1 H.A H.A b

…. …. R2 a0 R1

1 0 a0

…. …. Re

Rs ≥1

1 1 …. ….

b. Tirer les équations de S1 et R1 en fonction de a et b.

…………...………………………………………………………………………………

0.5 pt

c. Déduire l’équation de S2 et R2 en fonction de a, b et Re.

……….……………………………………..……………………………………………

0.5 pt

DOSSIER PEDAGOGIQUE 2011-2012 Page 6/8

d. Exprimer alors S et Rs en fonction de a, b et Re.

………………….…………………………….………………….………………………

0.75 pt

2. Pourquoi Y est maintenu à (9)10 ?

………………………………………………………..…………………………………………

0.5 pt

3. Expliquer le principe de fonctionnement de ce comparateur :

………………………………………………………..…………………………………………

0.5 pt

4. Déduire le rôle du circuit de détection d’erreur et l’additionneur N°2 ?

………………………………………………………..…………………………………………

0.5 pt

5. Donner une autre solution de circuit de détection d’erreur :

……………………………………………………….…………………………………………

0.5 pt

6. Quelles sont toutes les valeurs de [S’] en fonction de [S] et X ?

………………………………………………………..…………………………………………

0.5 pt

7. Déterminer [S]max et [S’]max:

………………………………………………………………………………………..…………

0.5 pt

8. On vient d’introduire aux entrées les deux nombres [A]=(9)10 et [B]=(7)10.

Déterminer les entrées et les sorties corresponds du circuit précédent :

[A] = […………….] ; [B] = […………….] ; [S] = […….…...….] et C4=…...

[Y] = [………….....….] ; [Z] = [……………...….] et X=…...

[S’] = […….……...….] et C’4=…... 1 pt

III. Etude de l’unité de comptage:(6 points)

En se référant au dossier technique page (4/6):

1. Mettre une croix dans la case correspondante :

1 pt

Le circuit intégré 4510 est un circuit :

Binaire BCD hexadécimal

Compteur seul Décompteur seul Compteur/décompteur

L’entrée CI est une entrée de :

Blocage Chargement Forçage à zéro

L’entrée de chargement PL :

Activée à niveau bas (0 Logique) Activée à niveau haut (1 Logique)

Dépend du signal d’horloge Ne dépend pas du signal d’horloge

chargement synchrone chargement asynchrone

L’entrée MR :

Activée à niveau bas (0 Logique) Activée à niveau haut (1 Logique)

Dépend du signal d’horloge Ne dépend pas du signal d’horloge

Remise à 0 synchrone Remise à 0 asynchrone

2. Compléter attentivement le tableau suivant : 0.5 pt

Mot binaire Mot binaire

Etats des entrées Mot décimal

( P3 P2 P1 P0 ) ( Q3 Q2 Q1 Q0 )

MR=1 et PL=0 ………………… ……………

0101

MR=0 et PL=1 ………………… ……………

DOSSIER PEDAGOGIQUE 2011-2012 Page 7/8

3. Compléter le chronogramme ci-dessous en mode décompteur pour des entrées de

chargement parallèle P3P2P1P0=0100 et lorsque initialement Q3Q2Q1Q0=0010.

PL 1 pt

t

Q0

t

Q1

t

Q2

t

Q3

t

4. Le lot de 30 biscuits formés est éjecté dans le four à une température élevée pour cuire

les biscuits. En utilisant le circuit intégré 4510 pour réaliser le comptage de ces lots

(compteur modulo 30). On note la possibilité de remettre le compteur manuellement à 0.

a. Déterminer les nombres des bascules et des circuits intégrés à utiliser: 0.5 pt

……………………………………………………………………………..………………..……

……………………………………..…………………………..………………….……...………

0.5 pt

b. Déterminer l’équation de RAZaut :……………………….……………….…………….….…

c. Déduire l’équation de RAZ :……………………….…………………….…………….….…

0.25 pt

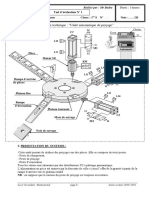

d. Compléter le schéma de câblage suivant en utilisant l’entrée MR pour la RAZ,

et préciser le circuit unité CU et le circuit dizaine CD.

2.25 pt

BON TRAVAIL

4510 4510

4 6 4 6

P0 Q0 P0 Q0

12 11 12 11

P1 Q1 P1 Q1

13 14 13 14

P2 Q2 P2 Q2

Horloge 3 2 3 2

P3 Q3 P3 Q3

15 RAZaut

CLK 15 &

CLK

5 7 5 7 RAZ

CI CO CI CO ≥1

10 10

U/ D U/ D RAZ man

1 1

PL PL

9 ……….…. 9 ……….….

MR MR R

+VCC

DOSSIER PEDAGOGIQUE 2011-2012 Page 8/8

Vous aimerez peut-être aussi

- Devoir de Synthèse N°1 - Génie Électrique Four de Traitement - Bac Technique (2015-2016) MR Abdallah RaouafiDocument4 pagesDevoir de Synthèse N°1 - Génie Électrique Four de Traitement - Bac Technique (2015-2016) MR Abdallah RaouafiFethi BenmassoudePas encore d'évaluation

- Devoir de Synthèse N°1 2015 2016 (MR Baazaoui Abderraouf)Document5 pagesDevoir de Synthèse N°1 2015 2016 (MR Baazaoui Abderraouf)Ahlem Rmida Ben HmidaPas encore d'évaluation

- 02 - Système Automatique de Marquage de Boîtiers (DR)Document4 pages02 - Système Automatique de Marquage de Boîtiers (DR)FM HELSENKI0% (2)

- Devoir de Synthèse N°1 2011 2012 (Abdallah Raouafi)Document5 pagesDevoir de Synthèse N°1 2011 2012 (Abdallah Raouafi)Piere EbrahimPas encore d'évaluation

- Partie Genie Electrique: Nom: ... Prénom: . . N°: . . 4STDocument4 pagesPartie Genie Electrique: Nom: ... Prénom: . . N°: . . 4STHakim SaidiPas encore d'évaluation

- Série 1 L. CombinatoireDocument10 pagesSérie 1 L. CombinatoireAbassiPas encore d'évaluation

- Devoir À RendreDocument2 pagesDevoir À RendreElias AzoumPas encore d'évaluation

- Activites Microcontroleur 16f84aDocument8 pagesActivites Microcontroleur 16f84aHichem HamdiPas encore d'évaluation

- Cours Lycée Pilote - Technologie Le GRAFCET - 2ème Sciences (2014-2015) MR Rafik Ben AmorDocument10 pagesCours Lycée Pilote - Technologie Le GRAFCET - 2ème Sciences (2014-2015) MR Rafik Ben AmorHana KhemissiPas encore d'évaluation

- Serie MCCDocument7 pagesSerie MCCrzougarzougaPas encore d'évaluation

- Devoir de Synthèse N°1 2012 2013 (Dhahri Salah)Document6 pagesDevoir de Synthèse N°1 2012 2013 (Dhahri Salah)Youssef CherniPas encore d'évaluation

- Devoir de Synthèse N°1 - Génie Électrique - 3ème Technique (2012-2013) MR KhiariDocument5 pagesDevoir de Synthèse N°1 - Génie Électrique - 3ème Technique (2012-2013) MR KhiariAbidi NawresPas encore d'évaluation

- Devoir de Synthèse N°1 - Génie Électrique Tri de Boitiers - Bac Technique (2014-2015) MR YagoubiDocument8 pagesDevoir de Synthèse N°1 - Génie Électrique Tri de Boitiers - Bac Technique (2014-2015) MR YagoubiFethi BenmassoudePas encore d'évaluation

- DC1 4T Dpe 17 CorrectionDocument4 pagesDC1 4T Dpe 17 Correctiontakecoin767Pas encore d'évaluation

- Auto - 1 - 2023 OkDocument8 pagesAuto - 1 - 2023 OkfjosephfabricePas encore d'évaluation

- Devoir de Synthèse N°1 - Technologie - 3ème Technique (2010-2011) MR Abdallah RaouafiDocument4 pagesDevoir de Synthèse N°1 - Technologie - 3ème Technique (2010-2011) MR Abdallah RaouafiOthman TmarPas encore d'évaluation

- Fin de Formation - Synthése ESA 2022 (TEST3) - 1Document6 pagesFin de Formation - Synthése ESA 2022 (TEST3) - 1otmane touilPas encore d'évaluation

- Série N - 6 Ali 2015 FinaleDocument14 pagesSérie N - 6 Ali 2015 FinaleHichem HamdiPas encore d'évaluation

- Serie1 Combinatoire 2022 2023Document13 pagesSerie1 Combinatoire 2022 2023Fares BouzidiPas encore d'évaluation

- Devoir de Synthèse N°3 - Technologie - 2ème Sciences (2012-2013) MR Abdallah RaouafiDocument4 pagesDevoir de Synthèse N°3 - Technologie - 2ème Sciences (2012-2013) MR Abdallah RaouafiFadi WeslatiPas encore d'évaluation

- 1ère Année Secondaire 0708 - Devoir de Synthése N°3Document5 pages1ère Année Secondaire 0708 - Devoir de Synthése N°3Kamel TayahiPas encore d'évaluation

- Devoir Syn FullDocument10 pagesDevoir Syn FullMouad Memni0% (1)

- TD Microcontroleur 2Document25 pagesTD Microcontroleur 2Ismael GhaziPas encore d'évaluation

- Devoir de Controle N°3: - Génie ÉlectriqueDocument4 pagesDevoir de Controle N°3: - Génie ÉlectriqueQuincaillerie Ben MansourPas encore d'évaluation

- Devoir de Synthèse N°3 - Génie Électrique Système Cadreuse Automatique - Bac Technique (2010-2011) MR Raouafi Abdallah PDFDocument4 pagesDevoir de Synthèse N°3 - Génie Électrique Système Cadreuse Automatique - Bac Technique (2010-2011) MR Raouafi Abdallah PDFFedi Berjeb0% (1)

- Devoir de Contrôle N°1 - Génie Mécanique - Conditionnement de Parfum - 3ème Technique (2016-2017) MR MezniDocument7 pagesDevoir de Contrôle N°1 - Génie Mécanique - Conditionnement de Parfum - 3ème Technique (2016-2017) MR MezniŚą ŅăPas encore d'évaluation

- Cours - Génie Électrique Microcontrôleur 16f84a - Bac Technique (2012-2013) MR AïssaDocument11 pagesCours - Génie Électrique Microcontrôleur 16f84a - Bac Technique (2012-2013) MR AïssaRaja Tě JazziriPas encore d'évaluation

- Devoir de Synthèse N°3 - Technologie Antenne Parabolique - 1ère AS (2010-2011) MR BAAZAOUI RaoufDocument6 pagesDevoir de Synthèse N°3 - Technologie Antenne Parabolique - 1ère AS (2010-2011) MR BAAZAOUI RaoufChihab GhlalaPas encore d'évaluation

- Devoir de Synthèse N°2 - Ligne Automatisee de Production de Pains - Bac Technique (2019-2020) MR Ben Aouicha MohamedDocument10 pagesDevoir de Synthèse N°2 - Ligne Automatisee de Production de Pains - Bac Technique (2019-2020) MR Ben Aouicha MohamedKhalil BkekriPas encore d'évaluation

- Automates Programmables Industriels (A.P.I)Document26 pagesAutomates Programmables Industriels (A.P.I)Hayet BechedliPas encore d'évaluation

- Dessin TechnoDocument3 pagesDessin TechnoGabriel ThibouPas encore d'évaluation

- Etude D'un Système PluritechniqueDocument13 pagesEtude D'un Système PluritechniqueScofieldPas encore d'évaluation

- Devoir de Contrôle N°1 - Technologie - 1ère AS (2009-2010) 2 PDFDocument3 pagesDevoir de Contrôle N°1 - Technologie - 1ère AS (2009-2010) 2 PDFأبوأحمد الجزيريPas encore d'évaluation

- 3-Devoir de Controle N1-2AS-2021Document5 pages3-Devoir de Controle N1-2AS-2021Rasmi BaananouPas encore d'évaluation

- Conditionnement Du Signal Unité ATC 1STE Bouchaib MAHBAB PDFDocument10 pagesConditionnement Du Signal Unité ATC 1STE Bouchaib MAHBAB PDFELmokhtar HamrouniPas encore d'évaluation

- 2-Devoir de Controle N1-2AS-2021Document7 pages2-Devoir de Controle N1-2AS-2021amri mohamedPas encore d'évaluation

- C - Présentation - Correction - PDF Microcontroleur (2020 - 8 - 10)Document8 pagesC - Présentation - Correction - PDF Microcontroleur (2020 - 8 - 10)WaSsIM100% (1)

- 1-Circuit Intégré: 74XX83:: Document Constructeur Des Circuits Intégrés Utilisés Dans Carte de CommandeDocument3 pages1-Circuit Intégré: 74XX83:: Document Constructeur Des Circuits Intégrés Utilisés Dans Carte de CommandeHakim SaidiPas encore d'évaluation

- 2 MCC 1 PDFDocument10 pages2 MCC 1 PDFمفتاح الدينPas encore d'évaluation

- TD N°6 Min PDFDocument2 pagesTD N°6 Min PDFSanda OumarouPas encore d'évaluation

- Travaux Dirigés Automatisme Electronique NumériqueDocument7 pagesTravaux Dirigés Automatisme Electronique Numériqueeyimambou100% (1)

- Chap 3 Les CompteursDocument10 pagesChap 3 Les CompteursAhmed BelhadjPas encore d'évaluation

- Devoir de Synthese N°3: Disciplines TechniquesDocument4 pagesDevoir de Synthese N°3: Disciplines TechniquesJUSDOVIC EDJOZOMBIPas encore d'évaluation

- DEVOIR-DE-CONTRÖLE-N2-Caisse Enregistreuse-Système de Numération - 2AS-LYCEE-BIR-LAHMAR-AZZABI-MOEZ-2022-2023 PDFDocument3 pagesDEVOIR-DE-CONTRÖLE-N2-Caisse Enregistreuse-Système de Numération - 2AS-LYCEE-BIR-LAHMAR-AZZABI-MOEZ-2022-2023 PDFChokri MAKTOUFPas encore d'évaluation

- Correction DS1 Bac 2021 2022Document4 pagesCorrection DS1 Bac 2021 2022Kadri MongiPas encore d'évaluation

- Devoir de Contrôle N°1 - Génie Électrique - Bac Technique (2010-2011) MR Abdallah Raouafi PDFDocument4 pagesDevoir de Contrôle N°1 - Génie Électrique - Bac Technique (2010-2011) MR Abdallah Raouafi PDFWassim Ben Mechlia50% (2)

- Devoir de Synthèse N°1 - Technologie CHAINE D'EMBALLAGE DES FEUILLES DE PAPIER - Bac Technique (2012-2013) MR Hadjkacem AbdelkarimDocument11 pagesDevoir de Synthèse N°1 - Technologie CHAINE D'EMBALLAGE DES FEUILLES DE PAPIER - Bac Technique (2012-2013) MR Hadjkacem Abdelkarimيس المباركيPas encore d'évaluation

- ATC ExercicesDocument42 pagesATC ExerciceskhamissbenzPas encore d'évaluation

- 8c5lh-Unite Automatique de PDFDocument3 pages8c5lh-Unite Automatique de PDFl mPas encore d'évaluation

- A22-Opérations D'arithmétique Binaire - v19 - 2Document6 pagesA22-Opérations D'arithmétique Binaire - v19 - 2Rafik Ben AmorPas encore d'évaluation

- CorrectionDevoirReplissageDesBarils1AS PDFDocument2 pagesCorrectionDevoirReplissageDesBarils1AS PDFisrael melchisedechPas encore d'évaluation

- TD-Dispositif D AblocageDocument1 pageTD-Dispositif D AblocageMama Samba SALLPas encore d'évaluation

- Devoir de Synthèse N°2 2009 2010 (Baouicha)Document10 pagesDevoir de Synthèse N°2 2009 2010 (Baouicha)halim otmanePas encore d'évaluation

- Application 2Document8 pagesApplication 2Foued RjibaPas encore d'évaluation

- dcn1 2020 3t2 Pince CorrectionDocument4 pagesdcn1 2020 3t2 Pince CorrectionGuiliassPas encore d'évaluation

- DPmecaniqueDocument4 pagesDPmecaniquelou louPas encore d'évaluation

- Bac - 2019-DR - Corrigé1 (Mec)Document8 pagesBac - 2019-DR - Corrigé1 (Mec)Wagih MrassiPas encore d'évaluation

- Fonction Processeur Moto-Réducteur MP+ Tapis Roulant Patins de Serrage Vérin C2 Moteur MT+système Vis-ÉcrouDocument4 pagesFonction Processeur Moto-Réducteur MP+ Tapis Roulant Patins de Serrage Vérin C2 Moteur MT+système Vis-Écroumohamed1101Pas encore d'évaluation

- ECE 2006 Controle PDFDocument5 pagesECE 2006 Controle PDFbaydiPas encore d'évaluation

- Exercice N°1Document2 pagesExercice N°1Fethi BenmassoudePas encore d'évaluation

- TH6 2 Aid Act4Document4 pagesTH6 2 Aid Act4Fethi BenmassoudePas encore d'évaluation

- Programmation en MikroC PRODocument5 pagesProgrammation en MikroC PROFethi BenmassoudePas encore d'évaluation

- TH6 1 EvalDocument2 pagesTH6 1 EvalFethi BenmassoudePas encore d'évaluation

- Sérien°8 MPP-3tech PDFDocument10 pagesSérien°8 MPP-3tech PDFTarak BenslimanePas encore d'évaluation

- Résumé Elec BacDocument29 pagesRésumé Elec BacFethi BenmassoudePas encore d'évaluation

- Eval 2Document2 pagesEval 2Fethi BenmassoudePas encore d'évaluation

- Devoir Synthese 1-Bac - DTDocument4 pagesDevoir Synthese 1-Bac - DTFethi BenmassoudePas encore d'évaluation

- DT1 2020 Mechanical R2018Document7 pagesDT1 2020 Mechanical R2018Fethi BenmassoudePas encore d'évaluation

- DR Dc2Document2 pagesDR Dc2Fethi BenmassoudePas encore d'évaluation

- DR2 2020 Mechanical R2018Document11 pagesDR2 2020 Mechanical R2018Fethi BenmassoudePas encore d'évaluation

- DS.2 Benarous (2) - ConvertiDocument16 pagesDS.2 Benarous (2) - ConvertiFethi BenmassoudePas encore d'évaluation

- 4ST 2017 DRE Système Moteur Dautomobileggg-ConvertiDocument6 pages4ST 2017 DRE Système Moteur Dautomobileggg-ConvertiFethi BenmassoudePas encore d'évaluation

- Devoir de Synthèse N°3 - Génie Électrique - 3ème Technique (2014-2015) MR Raouafi AbdallahDocument4 pagesDevoir de Synthèse N°3 - Génie Électrique - 3ème Technique (2014-2015) MR Raouafi AbdallahAbdelhakim Ebdelli100% (3)

- Devoir de Synthèse N°1 2019 2020 (MR Ben Aouicha)Document10 pagesDevoir de Synthèse N°1 2019 2020 (MR Ben Aouicha)Piere EbrahimPas encore d'évaluation

- Devoir de Contrôle N°1 - Génie Électrique LECTEUR DE GLYCEMIE - Bac Technique (2015-2016) MR Lazhar KHELILDocument7 pagesDevoir de Contrôle N°1 - Génie Électrique LECTEUR DE GLYCEMIE - Bac Technique (2015-2016) MR Lazhar KHELILeya meftahPas encore d'évaluation

- Devoir de Revision N°1Document5 pagesDevoir de Revision N°1Fethi BenmassoudePas encore d'évaluation

- Devoir Synthese 1-Bac - deDocument5 pagesDevoir Synthese 1-Bac - deFethi BenmassoudePas encore d'évaluation

- Devoir de Revision N°1Document5 pagesDevoir de Revision N°1Fethi BenmassoudePas encore d'évaluation

- Devoir de Revision N°1Document5 pagesDevoir de Revision N°1Fethi BenmassoudePas encore d'évaluation

- dc1-3SCTec Enonce Corrige PDFDocument8 pagesdc1-3SCTec Enonce Corrige PDFFethi BenmassoudePas encore d'évaluation

- Devoir de Synthèse N°1 - Génie Électrique Tri de Boitiers - Bac Technique (2014-2015) MR YagoubiDocument8 pagesDevoir de Synthèse N°1 - Génie Électrique Tri de Boitiers - Bac Technique (2014-2015) MR YagoubiFethi BenmassoudePas encore d'évaluation

- 4.cours FH 2014 2015Document131 pages4.cours FH 2014 2015elkhadimiPas encore d'évaluation

- DSFFFCDocument6 pagesDSFFFClyydiazebouchiPas encore d'évaluation

- Reseaux Sans Fil - Ok PDFDocument382 pagesReseaux Sans Fil - Ok PDFbonhomie BopePas encore d'évaluation

- Cdma, Ofdm, Mc-CdmaDocument4 pagesCdma, Ofdm, Mc-Cdmafelly mutuakashalaPas encore d'évaluation

- Installation Et Maintenance D'une BTSDocument16 pagesInstallation Et Maintenance D'une BTSMac Koumba100% (5)

- TD2 - Cryptographie - CopieDocument4 pagesTD2 - Cryptographie - CopieBenmimoun WeejdyPas encore d'évaluation

- TD2 Scan 2023Document2 pagesTD2 Scan 2023Fares SerdoukPas encore d'évaluation

- DS Ing3 BlancDocument5 pagesDS Ing3 BlancEssayh WadiePas encore d'évaluation

- RX-FM-ECF1 v3Document3 pagesRX-FM-ECF1 v3AudionPas encore d'évaluation

- Ant Quagui VHFDocument4 pagesAnt Quagui VHFWil NelsonPas encore d'évaluation

- 03 Conception Filtres SelectionDocument5 pages03 Conception Filtres SelectionJerson AngelPas encore d'évaluation

- Applications Du FiltrageDocument38 pagesApplications Du FiltrageN'GOLO MAMADOU KONEPas encore d'évaluation

- Filtres NumériquesDocument7 pagesFiltres NumériquesBenchabane AbderrahimPas encore d'évaluation

- Couche Physique ReseauDocument88 pagesCouche Physique ReseauAhmedSerrarPas encore d'évaluation

- Gestion Des Ressources Radio Dans Les Systèmes 2G Et 3GDocument2 pagesGestion Des Ressources Radio Dans Les Systèmes 2G Et 3Gπίστη πίστη0% (1)

- Armee Française TTA150 Titre16 Materiel TransmissionDocument46 pagesArmee Française TTA150 Titre16 Materiel TransmissionUncle Joffe90% (10)

- Circuit RLC Serie en Regime Sinusoidal Force Cours 1 1 PDFDocument7 pagesCircuit RLC Serie en Regime Sinusoidal Force Cours 1 1 PDFFaridaPas encore d'évaluation

- NTCL01Document34 pagesNTCL01Dang JinlongPas encore d'évaluation

- Seance 5Document18 pagesSeance 5Did you know THATPas encore d'évaluation

- Antenne DipôleDocument12 pagesAntenne DipôleMimi NourPas encore d'évaluation

- Circuit AnalogiqueDocument55 pagesCircuit AnalogiqueFerdinand SEMEPas encore d'évaluation

- tp4 2009Document10 pagestp4 2009Karim LamouchiPas encore d'évaluation

- Deploiement Du Reseau LTE - FIKRI Hajar - 2219Document98 pagesDeploiement Du Reseau LTE - FIKRI Hajar - 2219khaleesi Em100% (2)

- Physique Appliquée - Le Bruit ÉlectriqueDocument29 pagesPhysique Appliquée - Le Bruit ÉlectriqueelectroparleurPas encore d'évaluation

- Antenne Cornet Pyramidal PDFDocument8 pagesAntenne Cornet Pyramidal PDFMalik Sami100% (1)

- CorrectionTD2INFO by ExoSupDocument38 pagesCorrectionTD2INFO by ExoSupBoukhems HamzaPas encore d'évaluation

- Guide D'installation Et D'utilisation SAGEM LINK F - Ed5 PDFDocument145 pagesGuide D'installation Et D'utilisation SAGEM LINK F - Ed5 PDFFenitriniaina Sy Finiavana RazafyPas encore d'évaluation

- Modulation de Fréquence 1 PDFDocument22 pagesModulation de Fréquence 1 PDFTunENSTABPas encore d'évaluation

- Bts Crsa Cna Et CanDocument16 pagesBts Crsa Cna Et CanAFAF100% (1)

- 05 Le Cable CoaxDocument8 pages05 Le Cable CoaxRoberly Fiston BlbPas encore d'évaluation