Académique Documents

Professionnel Documents

Culture Documents

TD 1

Transféré par

Sabri MahmoudTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TD 1

Transféré par

Sabri MahmoudDroits d'auteur :

Formats disponibles

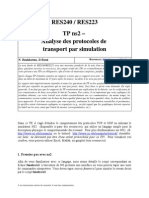

TD ARCHITECTURE

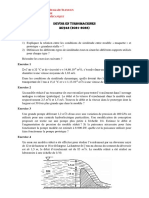

Exercice 1

Voici un premier schéma

d'un pipeline à 3 étages.

L'unité de temps est la

pico-seconde (ps) qui

vaut 10-12 seconde. Quelle

est la durée minimale du

cycle d'horloge ? Quel est

le débit maximal de ce

pipeline, en Gops (Giga-

opérations par seconde) ?

Quelle est dans ce cas la

latence, c'est-à-dire la

durée d'exécution d'une

instruction ?

Mêmes questions pour le

schéma ci-contre (les

durées de traitement des

trois circuits

combinatoires sont

différentes).

Mêmes questions en multipliant par deux le nombre d'étages du pipeline initial. Quel est le

débit qu'on ne dépassera jamais en augmentant encore la profondeur du pipeline ?

Exercice 2

On suppose qu'on a découpé les circuits combinatoires qui composent une instruction en six

blocs A à F de durées respectives 80, 60, 30, 50, 70 et 10 ps ; ces blocs doivent être exécutés

l'un après l'autre dans cet ordre, après quoi on charge un registre au prochain front d'horloge.

La durée de chargement d'un registre est de 20 ps.

1. Insérer un seul registre intermédiaire fournit un pipeline de profondeur 2. Où faut-il

insérer ce registre pour obtenir un débit maximal ? Calculer alors la durée du cycle

d'horloge, le débit et la latence.

2. Mêmes questions en insérant deux registres intermédiaires (pipeline de profondeur 3).

3. Quel est le pipeline de profondeur optimale ? Fournir une description et une analyse

des performances comme précédemment.

4. Echanger les durées de B et C et traiter à nouveau la question précédente.

Exercice 1 : corrigé

Question Durée du cycle Débit (en Gops) Latence

1 120 ps 1000 / 120 = 8.33 3 * 120 = 360 ps

2 170 ps 1000 / 170 = 5.88 3 * 170 = 510 ps

3 70 ps 1000 / 70 = 14.29 6 * 70 = 420 ps

Avec un temps de chargement des registres de 20 ps, la durée d'un cycle sera toujours

supérieure à 20 ps, et le débit inférieur à 50 Gops.

Exercice 2 : corrigé

1. Le meilleur partage est { A B } { C D E F } : le premier bloc de tâches a une durée de

140 ps et le second dure 160 ps. En plaçant C dans le premier bloc on obtiendrait des

durées de 170 et 130 ps, ce qui est moins bon : il faut minimiser la durée maximale. Ce

pipeline peut fonctionner avec un cycle de 180 ps, un débit de 1000 / 180 = 5.55 Gops

et une latence de 2 * 180 = 360 ps.

2. Le meilleur partage est { A } { B C } { D E F } ; les durées respectives sont 80 ps,

90 ps et 130 ps. En plaçant D dans le second bloc, celui-ci aurait une durée de 140 ps,

ce qui est moins bon. Ce pipeline peut fonctionner avec un cycle de 150 ps, un débit de

1000 / 150 = 6.66 Gops et une latence de 3 * 150 = 450 ps.

3. Puisque le circuit le plus lent est A qui dure 80 ps, le meilleur partage est celui dont

tous les blocs ont une durée inférieure ou égale à 80 ps. Il faut aussi minimiser la

profondeur du pipeline, c'est-à-dire le nombre d'étapes (qui est le même que le nombre

de registres du circuit). D'où le découpage : { A } { B } { C D } { E F }. Ce pipeline de

profondeur 4 peut fonctionner avec un cycle de 100 ps, un débit de 10 Gops et une

latence de 4 * 100 = 400 ps.

4. Cette fois il faut un pipeline de profondeur 5 : { A } { B } { C } { D } { E F }. Ce

pipeline a le même cycle et le même débit que le précédent, mais la latence passe à

500 ps.

Vous aimerez peut-être aussi

- Série2 2021Document2 pagesSérie2 2021CAMPUS TIZI OUZOUPas encore d'évaluation

- TD3 MicroprocesseurDocument2 pagesTD3 Microprocesseurالقرآن الكريمPas encore d'évaluation

- TD3 Igmp1 2019-2020Document4 pagesTD3 Igmp1 2019-2020Chaimae Ben hadouPas encore d'évaluation

- NSY104 TD Pipeline C-2 PDFDocument2 pagesNSY104 TD Pipeline C-2 PDFAnonymous gGnr6a8iyWPas encore d'évaluation

- TD3 2006Document8 pagesTD3 2006Hassan ChehouaniPas encore d'évaluation

- Ex 1Document6 pagesEx 1henry michelPas encore d'évaluation

- Sujet de Terminale PDFDocument6 pagesSujet de Terminale PDFJe suis Je suisPas encore d'évaluation

- Section N°8Document9 pagesSection N°8youssouf ahmedbabaPas encore d'évaluation

- 21010-td1 Mecaflu 1314Document6 pages21010-td1 Mecaflu 1314Maryem KhadraouyPas encore d'évaluation

- Fini DeversoirsDocument10 pagesFini DeversoirskawterPas encore d'évaluation

- TD4 2007Document6 pagesTD4 2007Hassan ChehouaniPas encore d'évaluation

- TD Serie2 CExosFinDocument9 pagesTD Serie2 CExosFinHoussemTunisinoPas encore d'évaluation

- Controle Continu2 IPST 22-01-2009 CorrigeDocument6 pagesControle Continu2 IPST 22-01-2009 CorrigeYoussef ElalaouiPas encore d'évaluation

- R Seaux Sans Fil Et R Seaux Mobile Chapitre TD3Document12 pagesR Seaux Sans Fil Et R Seaux Mobile Chapitre TD3Pape mbaye DiawPas encore d'évaluation

- Devoir 2021-2022Document2 pagesDevoir 2021-2022Djamel channel قناة جمالPas encore d'évaluation

- RES240 TP ns2Document5 pagesRES240 TP ns2asoubreadPas encore d'évaluation

- Turbulence TD-1Document2 pagesTurbulence TD-1yosri50% (2)

- TD N°4 MDFDocument6 pagesTD N°4 MDFimade zidanePas encore d'évaluation

- Nnales de La Faculté Des Sciences de Oulouse: C C D E M GDocument146 pagesNnales de La Faculté Des Sciences de Oulouse: C C D E M GAymen BouroubaPas encore d'évaluation

- Conception Boucle Recirculation Eau Chaude Partie2 PDFDocument6 pagesConception Boucle Recirculation Eau Chaude Partie2 PDFJean-François GourdePas encore d'évaluation

- TD Mips (1076)Document2 pagesTD Mips (1076)Sabri Mahmoud100% (1)

- Tdscheduling2020 2021Document3 pagesTdscheduling2020 2021Atashi Tsunagu (“Albedo”)Pas encore d'évaluation

- TD2 2022-2023 Isa1 Igm1Document4 pagesTD2 2022-2023 Isa1 Igm1Chaimae Ben hadou100% (1)

- N17-Manuel DTS 2016Document10 pagesN17-Manuel DTS 2016Mariam ZouhairPas encore d'évaluation

- Serie N°1Document2 pagesSerie N°1Dahi Mohamed100% (1)

- TD 2eme ANNEE ELECTROMECANIQUE (ENSEIGNANT YAHIAOUI KHEMISSI)Document16 pagesTD 2eme ANNEE ELECTROMECANIQUE (ENSEIGNANT YAHIAOUI KHEMISSI)Abdellatif MohamedPas encore d'évaluation

- 07 Bernouilli Generalise TDDocument5 pages07 Bernouilli Generalise TDsabbanrachidPas encore d'évaluation

- Correction Examen Rachid 2010Document4 pagesCorrection Examen Rachid 2010Youssef Skalli40% (5)

- Saé Réseaux:: Appartement 43Document6 pagesSaé Réseaux:: Appartement 43taouf95100Pas encore d'évaluation

- TD4 Meca Fluid Sigma 2023Document6 pagesTD4 Meca Fluid Sigma 2023YvesPas encore d'évaluation

- Correction TD2RLDocument3 pagesCorrection TD2RLAchraf Mabrouk40% (5)

- (TTD Échangeurs) PDFDocument6 pages(TTD Échangeurs) PDFNghapPas encore d'évaluation

- Mécanique Des Fluides: Exercice IDocument12 pagesMécanique Des Fluides: Exercice IKhaled Ben AyedPas encore d'évaluation

- Annales HydrauliqueDocument12 pagesAnnales HydrauliqueAnonymous M0tjyWPas encore d'évaluation

- HU0205 CorrigeDocument6 pagesHU0205 CorrigeTouré IsmailaPas encore d'évaluation

- FLE2RapportEssaisGrD2b1 2Document12 pagesFLE2RapportEssaisGrD2b1 2mxmgPas encore d'évaluation

- TD 2 Méc - Fluide - 2021 (GBI1)Document5 pagesTD 2 Méc - Fluide - 2021 (GBI1)Soumia AOBADPas encore d'évaluation

- T.D 1 Machines Hydrauliques Thermiques LEEP3 2022 2023Document6 pagesT.D 1 Machines Hydrauliques Thermiques LEEP3 2022 2023Petrovich sagloire Owabira ngomaPas encore d'évaluation

- TD8 Chap6 Pertes de ChargeDocument3 pagesTD8 Chap6 Pertes de Chargewassim Aj100% (1)

- TD3 AvecsolutionDocument12 pagesTD3 Avecsolutionr7klridmrPas encore d'évaluation

- TP 04Document7 pagesTP 04kawterPas encore d'évaluation

- TD MFH 2021Document6 pagesTD MFH 2021touhami.nouhailaPas encore d'évaluation

- Poulie Courroie DimensionnementDocument24 pagesPoulie Courroie DimensionnementmidiquentinPas encore d'évaluation

- TDL DynProc PDFDocument10 pagesTDL DynProc PDFDiogo Rosembergh da Silva NobregaPas encore d'évaluation

- Sujet Ingénierie de Réservoir 1 1ère Session 2019 CorrigéDocument6 pagesSujet Ingénierie de Réservoir 1 1ère Session 2019 CorrigéHarisPas encore d'évaluation

- TD1 FDRDocument3 pagesTD1 FDRbaklouti lindaPas encore d'évaluation

- CHAPITRE V-ForageDocument11 pagesCHAPITRE V-ForageZakaria Ghrissi alouiPas encore d'évaluation

- TP4 - Coup de BélierDocument7 pagesTP4 - Coup de BélierAhmed MediouniPas encore d'évaluation

- TD FluideDocument2 pagesTD FluideMbarek Orabi100% (2)

- Correction TDs 3 4Document2 pagesCorrection TDs 3 4Hela MloukaPas encore d'évaluation

- Fini DéversoirsDocument10 pagesFini DéversoirsNoussaiba BenhallouPas encore d'évaluation

- TD3 AvecSolutionDocument12 pagesTD3 AvecSolutionkhlifiPas encore d'évaluation

- TD MFH 2021Document5 pagesTD MFH 2021Ayoub tahiriPas encore d'évaluation

- SERIE I Pompes GMS III Exo 2019-ConvertiDocument8 pagesSERIE I Pompes GMS III Exo 2019-ConvertiMarouf OussamaPas encore d'évaluation

- TD5 2020Document5 pagesTD5 2020Hassan Chehouani100% (1)

- Exercices Corrigés Réseaux Sans FilDocument2 pagesExercices Corrigés Réseaux Sans FilAtashi Tsunagu (“Albedo”)89% (19)

- Muf131212 PDFDocument6 pagesMuf131212 PDFmarwenPas encore d'évaluation

- TD Mips (1076)Document2 pagesTD Mips (1076)Sabri Mahmoud100% (1)

- TD3 TSDocument3 pagesTD3 TSSabri MahmoudPas encore d'évaluation

- TD 3: Transformée en Z Exercice 1:: 1 Ère Année IA Enseignante: Imen MEZGHANIDocument2 pagesTD 3: Transformée en Z Exercice 1:: 1 Ère Année IA Enseignante: Imen MEZGHANISabri MahmoudPas encore d'évaluation

- TD 5730Document2 pagesTD 5730Sabri MahmoudPas encore d'évaluation

- S5 MPI AnalyseFourier!2014!Examen1Correction!20140110145452 PDFDocument3 pagesS5 MPI AnalyseFourier!2014!Examen1Correction!20140110145452 PDFLoraine TounaPas encore d'évaluation

- WWW - Cours Gratuit - Com Id 1277Document84 pagesWWW - Cours Gratuit - Com Id 1277Sabri MahmoudPas encore d'évaluation

- Correction Ds Math FourrierDocument4 pagesCorrection Ds Math FourrierSabri MahmoudPas encore d'évaluation

- Ds Math FourrierDocument1 pageDs Math FourrierSabri MahmoudPas encore d'évaluation

- Ds Math FourrierDocument1 pageDs Math FourrierSabri MahmoudPas encore d'évaluation

- Correction Serie1 Transformée de Fourier-1-8Document8 pagesCorrection Serie1 Transformée de Fourier-1-8Sabri MahmoudPas encore d'évaluation

- Chapitre 1 Transformée de FourierDocument12 pagesChapitre 1 Transformée de FourierSabri MahmoudPas encore d'évaluation

- 204 - Modélisation Et Simulation Des Flux Logistiques 1 - 1ere PartieDocument16 pages204 - Modélisation Et Simulation Des Flux Logistiques 1 - 1ere PartiePascal KouamanPas encore d'évaluation

- Statistiques AutomatiséesDocument6 pagesStatistiques AutomatiséesReda KeraghelPas encore d'évaluation

- Architecture CoucheDocument54 pagesArchitecture CoucheSimo BaL'Pas encore d'évaluation

- S1 - Partie II - Emplois Du Temps 2022-2023Document10 pagesS1 - Partie II - Emplois Du Temps 2022-2023Hassib YounesPas encore d'évaluation

- Asnières-sur-Seine, Au Cours Des Siècles PDFDocument31 pagesAsnières-sur-Seine, Au Cours Des Siècles PDFtraorePas encore d'évaluation

- Rapport de StageDocument54 pagesRapport de Stagelch étudePas encore d'évaluation

- TD Meth NumDocument7 pagesTD Meth NumYrdnay ZafindraisahaPas encore d'évaluation

- Auto-Formation Mastercam Solids 2018Document118 pagesAuto-Formation Mastercam Solids 2018Anis Ziani100% (1)

- Annale Maths Extrait PDFDocument12 pagesAnnale Maths Extrait PDFFranck DossehPas encore d'évaluation

- Zeghdoud BadraDocument56 pagesZeghdoud BadraToufik YemniPas encore d'évaluation

- B td1 Robot ChargesDocument12 pagesB td1 Robot ChargesMounir BoutaghanePas encore d'évaluation

- TD3 - Amélioration BDDocument2 pagesTD3 - Amélioration BDImane LamdainePas encore d'évaluation

- Directive NIS2, Guide de Conformité - Ebook YogoshaDocument40 pagesDirective NIS2, Guide de Conformité - Ebook YogoshaMondher GamPas encore d'évaluation

- HE2B ESI BrochureDocument4 pagesHE2B ESI BrochureFranky AbdiasPas encore d'évaluation

- Gas Cisco 560Document18 pagesGas Cisco 560fatima-ezzahraPas encore d'évaluation

- ALL Commandes CCNA SecurityDocument10 pagesALL Commandes CCNA SecurityYassine AGPas encore d'évaluation

- Fc8000 ManuelDocument186 pagesFc8000 ManuelRenaudLacorPas encore d'évaluation

- Masters Ti, PNT, Mec Initiation À Matlab M. AfifiDocument30 pagesMasters Ti, PNT, Mec Initiation À Matlab M. AfifiMohcine RaPas encore d'évaluation

- Elektor N°406 - Avril 2012Document88 pagesElektor N°406 - Avril 2012bruno vinnacPas encore d'évaluation

- PAGE2 - INFO - Le Réseau Informatique Au CollègeDocument2 pagesPAGE2 - INFO - Le Réseau Informatique Au CollègequartierPas encore d'évaluation

- Mat 265 V2Document251 pagesMat 265 V2othmane.karamat.1Pas encore d'évaluation

- Handout1 7sDocument25 pagesHandout1 7sBakary DiassyPas encore d'évaluation

- Systèmes D'exploitation: Buts de Cet EnseignementDocument54 pagesSystèmes D'exploitation: Buts de Cet EnseignementSouad Najoua LagmiriPas encore d'évaluation

- Tutoriel Détaillé WinolsDocument26 pagesTutoriel Détaillé Winolscomneuf auto100% (3)

- Identité Numérique: Mohamed CAMARA Eddie Cherifa Aurélien TAUPINDocument11 pagesIdentité Numérique: Mohamed CAMARA Eddie Cherifa Aurélien TAUPINapi-315027569Pas encore d'évaluation

- Architecture de Microservices Pilotée Par APIAPIDocument59 pagesArchitecture de Microservices Pilotée Par APIAPIcarklounPas encore d'évaluation

- 4.corrigé TD3 PILE & FILEDocument13 pages4.corrigé TD3 PILE & FILEKaoutar BaghazPas encore d'évaluation

- Chapitre 3 - Les Entrées-SortiesDocument18 pagesChapitre 3 - Les Entrées-SortiesChaima BelhediPas encore d'évaluation

- 2.5 Mise en Place D - Un Réseau LocalDocument34 pages2.5 Mise en Place D - Un Réseau LocalMame Samba NDIAYEPas encore d'évaluation

- Travaux Pratiques Numéro 2Document5 pagesTravaux Pratiques Numéro 2MbrrrPas encore d'évaluation

- Apprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationD'EverandApprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationPas encore d'évaluation

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- L'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.D'EverandL'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.Évaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- Dark Python : Apprenez à créer vos outils de hacking.D'EverandDark Python : Apprenez à créer vos outils de hacking.Évaluation : 3 sur 5 étoiles3/5 (1)

- Technologie automobile: Les Grands Articles d'UniversalisD'EverandTechnologie automobile: Les Grands Articles d'UniversalisPas encore d'évaluation

- Le guide du hacker : le guide simplifié du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandLe guide du hacker : le guide simplifié du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 5 sur 5 étoiles5/5 (2)

- Conception & Modélisation CAO: Le guide ultime du débutantD'EverandConception & Modélisation CAO: Le guide ultime du débutantPas encore d'évaluation

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- Hacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandHacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- Le Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsD'EverandLe Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsÉvaluation : 4 sur 5 étoiles4/5 (2)

- Dans l'esprit des grand investisseurs: Un voyage à la découverte de la psychologie utilisée par les plus grands investisseurs de tous les temps à travers des analyses opérationnellD'EverandDans l'esprit des grand investisseurs: Un voyage à la découverte de la psychologie utilisée par les plus grands investisseurs de tous les temps à travers des analyses opérationnellÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- Le marketing d'affiliation en 4 étapes: Comment gagner de l'argent avec des affiliés en créant des systèmes commerciaux qui fonctionnentD'EverandLe marketing d'affiliation en 4 étapes: Comment gagner de l'argent avec des affiliés en créant des systèmes commerciaux qui fonctionnentPas encore d'évaluation

- Le money management facile à apprendre: Comment tirer profit des techniques et stratégies de gestion de l'argent pour améliorer l'activité de trading en ligneD'EverandLe money management facile à apprendre: Comment tirer profit des techniques et stratégies de gestion de l'argent pour améliorer l'activité de trading en ligneÉvaluation : 3 sur 5 étoiles3/5 (3)

- Le trading des bandes de bollinger facile à apprendre: Comment apprendre à utiliser les bandes de bollinger pour faire du commerce en ligne avec succèsD'EverandLe trading des bandes de bollinger facile à apprendre: Comment apprendre à utiliser les bandes de bollinger pour faire du commerce en ligne avec succèsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Gestion de projet : outils pour la vie quotidienneD'EverandGestion de projet : outils pour la vie quotidienneÉvaluation : 5 sur 5 étoiles5/5 (2)

- Explication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumD'EverandExplication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumPas encore d'évaluation

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Hacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersD'EverandHacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersPas encore d'évaluation

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation