Académique Documents

Professionnel Documents

Culture Documents

Chpitre 2 Mémoire

Transféré par

agrebaouiinsaf5Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Chpitre 2 Mémoire

Transféré par

agrebaouiinsaf5Droits d'auteur :

Formats disponibles

Les mémoires ISET Mahdia

I. Introduction

Historiquement, la mémoire a été réalisée selon plusieurs technologies,

commençant par les tubes à vide, passant par les tores magnétiques et maintenant

les mémoires à semi conducteurs, à base des bascules.

Dans toutes ces technologies, on cherchait à mémoriser l'information élémentaire

ou le bit, en lui attribuant une composante matérielle capable d’avoir deux états

stables. On parle toujours d’une cellule ou point mémoire.

II. La mémoire

La mémoire est un dispositif capable d’enregistrer des informations,

de les conserver aussi longtemps que nécessaire ou que possible, puis de les restituer

à la demande.

II.1. Organisation d’une mémoire

La mémoire peut être vue comme un ensemble de cellules ou cases contenant

chacune une information : une instruction ou une donnée. Chaque case mémoire est

repérée par un numéro d’ordre unique : son adresse.

Chaque donnée devient alors accessible grâce à son adresse.

Figure 1 : Organisation d’une mémoire

Architecture des ordinateurs 28

Les mémoires ISET Mahdia

Une case mémoire peut être lue ou écrite par le microprocesseur (cas des

mémoires vives) ou bien seulement lue (cas des mémoires mortes).

Avec une adresse de n bits il est possible de référencer au plus 2n cases mémoire.

Chaque case est remplie par un mot de données (sa longueur m est toujours

une puissance de 2). Le nombre de fils d’adresses d’un boîtier mémoire définit donc

le nombre de cases mémoire que comprend le boîtier. Le nombre de fils de données

définit la taille des données que l’on peut sauvegarder dans chaque case mémoire.

En plus du bus d’adresses et du bus de données, un boîtier mémoire comprend

une entrée de commande qui permet de définir le type d’action que l’on effectue avec

la mémoire (lecture/écriture) et une entrée de sélection qui permet de mettre

les entrées/sorties du boîtier en haute impédance.

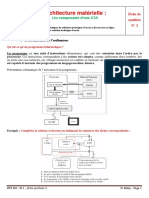

On peut schématiser un circuit mémoire par la figure suivante où l’on peut distinguer :

Les entrées d’adresses

Les entrées et les sorties de données

Les entrées de commandes :

• une entrée de sélection de lecture ou d’écriture (R/W)

• une entrée de sélection du circuit (CS)

Une opération de lecture ou d’écriture de la mémoire suit toujours le même cycle :

1. sélection de l’adresse

2. choix de l’opération à effectuer (R/W)

3. sélection de la mémoire (CS = 0)

4. lecture ou écriture la donnée

NB : Les E/S de données sont très souvent regroupées sur des bornes bidirectionnelles.

Architecture des ordinateurs 29

Les mémoires ISET Mahdia

II.2. Terminologie et définition

Le bit : c'est le plus petit élément d'information que l'on peut stocker dans

une mémoire, il constitue l’unité de base de l’information. Il est souvent appelé

point mémoire car il mémorise un bit d’information

Point mémoire : c’est un circuit à deux états stables, capable de stocker l’un des deux

chiffres binaires 1, 0 (digits).

L’octet, ou byte (en anglais) : correspond à un groupement de 8 bits

La cellule mémoire (case mémoire) : C'est la plus petite quantité d’information

adressable. Ces dernières années, la plupart des fabricants se sont mis d’accord

sur une cellule de 8 bits, c'est à dire octet.

Mot mémoire : pour accéder à la mémoire centrale, on doit lire ou écrire un ensemble

de bits de taille fixée à l’avance. Ce lot de bits à accéder soit lecture ou en écriture,

s’appelle mot mémoire. La mémoire centrale n’est donc qu’une suite de mots.

Chaque mot est identifié par un numéro unique appelé adresse.

II.3. Caractéristiques de la mémoire centrale

La capacité :

Dite aussi taille de la mémoire, c’est le nombre total de cellules qu'elle contient donc elle

correspond au nombre d’informations qu’elle peut contenir. Elle est généralement

exprimée en bits, en octets (bytes) ou en nombre de mots mémoire (words).

Compte tenu de l'adressage binaire, les capacités des mémoires s'expriment en

puissances de deux (ou en multiples de 210). Ce tableau explicite les unités utilisées.

Symbole Préfixe Décimal Binaire

1k (kilo) 103 210 = 1024

1M (méga) 106 220 = 1048576

1G (giga) 109 230 = 1073741824

1T (téra) 1012 240 = 1099511627776

1P (péta) 1015 250 = 1125899906842624

1E (exa) 1018 260 = 1152921504606846976

Tableau 1: Table des unités de mesure de la capacité

Architecture des ordinateurs 30

Les mémoires ISET Mahdia

Temps d’accès

C’est le temps qui sépare le début de l’opération d’accès et sa terminaison.

Dans la pratique et pour plusieurs types de mémoire centrale, le temps que demande

une opération de lecture peut être différent de celui d’une opération d’écriture.

Dans ce cas on compte le temps le plus long.

Cycle mémoire

C’est le temps minimal écoulant entre deux accès successifs à la mémoire.

Théoriquement, le cycle mémoire est égal au temps d’accès. Mais pratiquement

le premier est plus long que le deuxième, car le bon fonctionnement de la mémoire

nécessite quelques opérations de maintient et de stabilisation des signaux dans

le circuit.

Débit :

C’est le nombre d’informations (exprimé en bits) lues ou écrites par seconde.

Il est exprimé en fonction du cycle mémoire (CM) et de la taille du mot mémoire

(TMM) comme suit :

Volatilité

Elle caractérise la permanence des informations dans la mémoire centrale.

Une mémoire volatile perd son contenu lorsqu’on coupe le courant. Celle ci a donc

besoin d’un apport constant d’énergie électrique pour conserver ses informations.

La mémoire à base de transistors est volatile. On peut réaliser des mémoires non

volatiles avec les transistors moyennant un générateur de courant électrique (batterie).

Tel est le cas pour la mémoire CMOS qui contient les paramètres de configuration

de l’ordinateur. Il y a une autre catégorie de mémoire, à base de résistances

électriques, qui constitue une mémoire permanente. C’est le cas de la mémoire centrale

qui contient le bios.

II.4. Critères de choix d’une mémoire

Les principaux critères du choix de la mémoire utilisés sont : la capacité, la vitesse,

la consommation et le coût.

Architecture des ordinateurs 31

Les mémoires ISET Mahdia

III. Hiérarchie mémoire et classification

III.1. Notion de hiérarchie mémoire

Une mémoire idéale serait une mémoire de grande capacité, capable de stocker

un maximum d’informations et possédant un temps d’accès très faible afin de pouvoir

travailler rapidement sur ces informations. Mais il se trouve que les mémoires

de grande capacité sont souvent très lente et que les mémoires rapides sont très chères.

Et pourtant, la vitesse d’accès à la mémoire conditionne dans une large mesure

les performances d’un système. En effet, c’est là que se trouve le goulot d’étranglement

entre un microprocesseur capable de traiter des informations très rapidement

et une mémoire beaucoup plus lente (ex : processeur actuel à 3Ghz et mémoire à

400MHz). Or, on n’a jamais besoin de toutes les informations au même moment.

Afin d’obtenir le meilleur compromis coût-performance, on définie donc une

hiérarchie mémoire. On utilise des mémoires de faible capacité mais très rapide pour

stocker les informations dont le microprocesseur se sert le plus et on utilise des

mémoires de capacité importante mais beaucoup plus lente pour stocker les

informations dont le microprocesseur se sert le moins. Ainsi, plus on s’éloigne du

microprocesseur et plus la capacité et le temps d’accès des mémoires vont augmenter.

Figure 2 : Hiérarchie mémoire

Architecture des ordinateurs 32

Les mémoires ISET Mahdia

Les registres sont les éléments de mémoire les plus rapides. Ils sont situés au niveau

du processeur et servent au stockage des opérandes et des résultats intermédiaires.

La mémoire cache est une mémoire rapide de faible capacité destinée à accélérer

l’accès à la mémoire centrale en stockant les données les plus utilisées.

La mémoire principale est l’organe principal de rangement des informations.

Elle contient les programmes (instructions et données) et elle est plus lente que les deux

mémoires précédentes.

La mémoire d’appui sert de mémoire intermédiaire entre la mémoire centrale

et les mémoires de masse. Elle joue le même rôle que la mémoire cache.

La mémoire de masse est une mémoire périphérique de grande capacité utilisée pour

le stockage permanent ou la sauvegarde des informations. Elle utilise pour cela

des supports magnétiques (disque dur, ZIP) ou optiques (CDROM, DVDROM).

III.2. Classification des mémoires

Figure 3 : Les différents types de mémoire

Architecture des ordinateurs 33

Les mémoires ISET Mahdia

Il existe deux types de mémoire dans un système informatique :

La mémoire centrale : elle est très rapide, physiquement peu encombrante mais

coûteuse, c’est la mémoire « de travail » de l’ordinateur. Lorsqu’on parle

de mémoire, sans plus de précision, c’est généralement de ce type de mémoire

qu’il s’agit.

La mémoire de masse ou mémoire auxiliaire : elle est plus lente, assez encombrante

physiquement, mais meilleur marché, c’est la mémoire de « sauvegarde »

des informations.

IV. La mémoire centrale

Depuis le début des années 70, les mémoires à semi-conducteurs constituent

les éléments de base de toute mémoire centrale. L'évolution de la technologie a permis

de réaliser des mémoires intégrées qui constituent actuellement les meilleurs éléments

de la mémoire centrale au point de vue capacité et prix. Cette technologie utilise comme

matière de base le silicium et comme élément actif le transistor, on distingue deux types

de transistors:

les transistors bipolaires sont les plus rapides, on les trouve avec plusieurs variantes

dans les circuits les plus performants.

les transistors MOS (Metal Oxyde Semi-conducteur) moins rapides mais moins chers,

plus denses, c'est à dire offrant une intégration plus élevée. La technologie MOS a

donné lieu à un grand nombre de variantes comme le CMOS (Complementary

MOS) qui a l'avantage de consommer peu d'énergie.

La mémoire centrale est aussi appelée mémoire principale, elle contient

les instructions et les données, donc des programmes que l’on désire exécuter.

On distingue deux types principaux de mémoire centrale :

Les mémoires vives sont en général volatiles : elles perdent leurs informations en cas

de coupure d'alimentation. Certaines d'entre elles, ayant une faible consommation,

peuvent être rendues non volatiles par l'adjonction d'une batterie.

Les mémoires mortes sont non volatiles : leur contenu est écrit par le fabricant ou

l’utilisateur

Architecture des ordinateurs 34

Les mémoires ISET Mahdia

IV.1. Schéma fonctionnel de la mémoire centrale

Extérieurement, et en ne tenant compte que des signaux logiques, un bloc mémoire

peut être représenté comme sur la figure ci-dessous. Pour pouvoir identifier

individuellement chaque mot on utilise k lignes d'adresse. La taille maximale d'un bloc

mémoire est donc 2k mots, le premier mot se situant à l'adresse 0 et le dernier à

l'adresse 2k - 1. Une ligne de commande (R/W) indique si la mémoire est accédée en

écriture (l'information doit être mémorisée) ou en lecture (l'information doit être

restituée). Les accès en entrée et en sortie peuvent être confondus en un seul canal

bidirectionnel. La ligne de validation ou de sélection du bloc (CS) n’est autre que la

commande d’autorisation de la mémoire.

Figure 4 : Schéma de principe de la mémoire centrale

Dispositif d’adressage et de sélection : ce circuit permet de localiser un mot mémoire

étant donnée son adresse dans le registre d’adresses, puis d’effectuer l’opération

d’accès (en lecture ou en écriture) depuis ou vers le registre mot.

Registre d’adresses : le registre d’adresse qui appartient à l’unité centrale de

traitement, sert comme renseignement pour le dispositif de sélection et

d’adressage, pour localiser le mot à lire ou à écrire.

Registre mot : il doit contenir la valeur du mot à écrire dans la mémoire centrale

(MC) et ce avant une opération d’écriture. Il contiendra aussi la valeur du mot

après une opération de lecture.

Architecture des ordinateurs 35

Les mémoires ISET Mahdia

Lecture d’un mot mémoire : pour lire un mot mémoire, l’unité centrale de traitement

doit mémoriser l’adresse de ce mot dans le registre d’adresses, ensuite elle donne

l’ordre d’accès en lecture au dispositif de sélection et d’adressage (CS à 1 et R/W à

1). Celui-ci va faire sortir la valeur du mot considéré vers le registre mot.

Ecriture d’un mot mémoire : l’unité centrale de traitement va mémoriser l’adresse

du mot à écrire dans le registre d’adresses. En même temps, elle va passer la

valeur à écrire dans le registre mot. Elle donne ensuite un ordre d’écriture au

dispositif de sélection et d’adressage. Celui-ci va transférer la valeur du registre

mot vers le mot mémoire concernée.

Figure 5 : Chronogrammes de lecture/ écriture en mémoire

Remarque :

La taille du registre mot doit être identique à la taille du mot mémoire.

La taille du registre d’adresses détermine le nombre maximum de mots dans la

mémoire centrale.

Architecture des ordinateurs 36

Les mémoires ISET Mahdia

Application : Déterminer la taille minimale du registre d’adresses sachant que :

• La taille de la mémoire centrale est : TMC (bits)

• La taille d’un mot mémoire est : TMM (bits)

• Le nombre de mot mémoire est : N

IV.2. Organisation interne de la mémoire centrale

Le dispositif de sélection et d’adressage est conçu à base d’un décodeur.

Une adresse en entrée du décodeur n’active à sa sortie qu’une seule ligne à la fois.

Chaque ligne de sortie du décodeur nous permettra de sélectionner un mot mémoire.

La figure ci-dessous nous montre, comment réaliser une mémoire de quatre mots,

chacun de quatre bits. Ce raisonnement peut être applicable à n’importe quel bloc

mémoire indépendamment de sa taille.

Figure 6 : Organisation d'une mémoire de 4 mots de 4 bits chacun

Architecture des ordinateurs 37

Les mémoires ISET Mahdia

IV.3. Interfaçage microprocesseur/mémoire

Figure 7 : Interfaçage microprocesseur/mémoire

Figure 8 : Représentation condensée (plus pratique)

IV.4. Connexion de plusieurs boîtiers mémoire sur le bus

d’un microprocesseur

Les boitiers mémoire possèdent une broche notée CS : Chip Select. Lorsque cette

broche est active (état bas), le circuit peut être lu ou écrit. Lorsqu’elle est inactive (état

haut), le circuit est exclu du service : ses broches de données D0 `a D7 passent à l’état

de haute impédance : tout se passe comme si la mémoire était déconnectée du bus de

données du microprocesseur, d’où la possibilité de connecter plusieurs boitiers

mémoire sur un même bus : un seul signal CS doit être actif à un instant donné pour

éviter les conflits entre les différents boîtiers.

Architecture des ordinateurs 38

Les mémoires ISET Mahdia

Exemple : connexion de trois boitiers mémoire d’une capacité de 8 Ko chacun (13

lignes d’adresses) sur un bus d’adresse de 16 bits :

IV.5. Décodage d’adresses

Les trois bits A13, A14 et A15 utilisés précédemment fournissent 8 combinaisons,

de 000 à 111, d’où la possibilité de connecter jusqu’à 8 boitiers mémoires sur le bus.

La mémoire totale implantée devient donc de 8 × 8 Ko = 64 Ko : valeur maximale

possible avec 16 bits d’adresses. Pour cela, il faut utiliser un circuit de décodage

d’adresses, dans ce cas : un décodeur 3 vers 8.

Architecture des ordinateurs 39

Les mémoires ISET Mahdia

Table de vérité du décodeur d’adresses :

La cartographie (mapping) de la mémoire visible par le microprocesseur devient ainsi :

IV.6. Assemblage de blocs mémoires pour constituer la MC

Les techniques d'intégration ne permettent pas d'obtenir des boîtiers ayant des

capacités ou des formats suffisants pour toutes les applications. Il est alors nécessaire

d'associer plusieurs boîtiers pour augmenter la longueur des mots ou le nombre de

mots. L'association de plusieurs blocs peut permettre d'améliorer les performances

temporelles de la mémoire en faisant fonctionner plusieurs blocs en parallèle.

IV.6.1. Augmentation de la longueur des mots

La figure suivante montre qu'il est aisé d'associer deux boîtiers de 2k mots de n

bits pour obtenir un bloc de 2k mots de 2n bits. L'adressage doit être appliqué

simultanément aux deux circuits, l'un fournissant les n bits de bas poids et l'autre les n

bits de haut poids.

Architecture des ordinateurs 40

Les mémoires ISET Mahdia

IV.6.2. Augmentation du nombre de mots

La figure suivante montre la réalisation d'un bloc de 4 x 2k mots de n bits à l'aide

de 4 boîtiers de 2k x n bits. Il faut k+2 lignes d'adresses. Les k bits de bas poids de

l'adresse sont appliqués simultanément sur les 4 boîtiers. Les deux bits de haut poids

attaquent un décodeur à quatre sorties. Chacune de ces quatre lignes permet de

sélectionner un boîtier (entrée de validation du boîtier : CS). Un seul boîtier est alors

connecté aux lignes de sortie.

V. Différents types de mémoire

V.1. Les mémoires vives (RAM)

Une mémoire vive sert au stockage temporaire de données. Elle doit avoir un

temps de cycle très court pour ne pas ralentir le microprocesseur. Les mémoires vives

sont en général volatiles : elles perdent leurs informations en cas de coupure

d'alimentation. Certaines d'entre elles, ayant une faible consommation, peuvent être

rendues non volatiles par l'adjonction d'une batterie.

Architecture des ordinateurs 41

Les mémoires ISET Mahdia

Il existe deux grandes familles de mémoires RAM (Random Acces Memory :

mémoire à accès aléatoire) : les RAM statiques et les RAM dynamiques

V.1.1. Les RAM statiques

Le bit mémoire d'une RAM statique (SRAM) est composé d'une bascule. Chaque

bascule contient entre 4 et 6 transistors.

V.1.2. Les RAM dynamiques

Dans les RAM dynamiques (DRAM),

l'information est mémorisée sous la forme d'une

charge électrique stockée dans un condensateur

(capacité grille substrat d'un transistor MOS).

Avantages :

Cette technique permet une plus grande densité d'intégration, car un point

mémoire nécessite environ quatre fois moins de transistors que dans une mémoire

statique. Sa consommation s’en retrouve donc aussi très réduite.

Inconvénients :

La présence de courants de fuite dans le condensateur contribue à sa décharge.

Ainsi, l’information est perdue si on ne la régénère pas périodiquement (charge du

condensateur). Les RAM dynamiques doivent donc être rafraîchies régulièrement pour

entretenir la mémorisation : il s'agit de lire l'information et de la recharger. Ce

rafraîchissement indispensable a plusieurs conséquences :

• il complique la gestion des mémoires dynamiques car il faut tenir compte

des actions de rafraîchissement qui sont prioritaires.

• la durée de ces actions augmente le temps d'accès aux informations.

Architecture des ordinateurs 42

Les mémoires ISET Mahdia

D’autre part, la lecture de l’information est destructive. En effet, elle se fait par

décharge de la capacité du point mémoire lorsque celle-ci est chargée. Donc toute

lecture doit être suivie d’une réécriture.

V.1.3. Conclusions

En général les mémoires dynamiques, qui offrent une plus grande densité

d'information et un coût par bit plus faible, sont utilisées pour la mémoire centrale,

alors que les mémoires statiques, plus rapides, sont utilisées lorsque le facteur vitesse

est critique, notamment pour des mémoires de petite taille comme les caches

et les registres.

Voici un historique de quelques DRAM qui sont utilisées dans les PC :

• La DRAM (Dynamic RAM, RAM dynamique) : est le type de mémoire le plus

répandu, il s'agit d'une mémoire dont les transistors sont rangés dans une

matrice selon des lignes et des colonnes. Un transistor, couplé à un condensateur

donne l'information d'un bit.

Une barrette de mémoire DRAM de 256 Mo contiendra donc :

256 * 2^20 = 268 435 456 octets = 2 147 483 648 bits = 2 147 483 648 transistors.

• La DRAM FPM (Fast Page Mode, 1987) : elle permet d'accéder plus rapidement à

des données en introduisant la notion de page mémoire. (25 à 33 Mhz)

• La DRAM EDO (Extended Data Out, 1995) : Les composants de cette mémoire

permettent de conserver plus longtemps l'information, on peut donc ainsi

espacer les cycles de rafraîchissement. Elle apporte aussi la possibilité

d’anticiper sur le prochain cycle mémoire. (33 à 66 Mhz)

• La DRAM BEDO (Bursted EDO) : On n'adresse plus chaque unité de mémoire

individuellement lorsqu'il faut y lire ou y écrire des données. On se contente de

transmettre l'adresse de départ du processus de lecture/écriture et la longueur

du bloc de données (Burst). Ce procédé permet de gagner beaucoup de temps,

notamment avec les grands paquets de données tels qu'on en manipule avec les

applications modernes. (66 Mhz)

Architecture des ordinateurs 43

Les mémoires ISET Mahdia

• La Synchronous DRAM (SDRAM, 1997) : la mémoire SDRAM a pour particularité

de se synchroniser sur une horloge. Les mémoires FPM, EDO étaient des

mémoires asynchrones et elle induisaient des temps d'attentes lors de la

synchronisation. Elle se compose en interne de deux bancs de mémoire et des

données peuvent être lues alternativement sur l'un puis sur l'autre de ces bancs

grâce à un procédé d'entrelacement spécial. Le protocole d'attente devient donc

tout à fait inutile. Cela lui permet de supporter des fréquences plus élevées

qu’avant (100 Mhz).

• La DDR-I ou DDR-SDRAM (Double Data Rate Synchronous DRAM, 2000) :

elle permet de recevoir ou d'envoyer des données lors du front montant et du

front descendant de l’horloge. (133 à 200 MHz)

• DDR2-SDRAM : la mémoire DDR2 (ou DDR-II) permet d'atteindre des débits deux

fois plus élevés que la DDR à fréquence externe égale. On parle de QDR

(Quadruple Data Rate ou quad-pumped) pour désigner la méthode de lecture et

d'écriture utilisée. Elle utilise en effet deux canaux séparés pour la lecture et

pour l'écriture, si bien qu'elle est capable d'envoyer ou de recevoir deux fois plus

de données que la DDR.

La DDR2 possède également un plus grand nombre de connecteurs que la DDR

classique (240 pour la DDR2 contre 184 pour la DDR).

• DDR3-SDRAM : elle améliore les performances par rapport au DDR2, mais surtout

diminue la consommation électrique (de 40 %). Les barrettes DDR3 ont 240

connecteurs comme les DDR2 mais ne sont absolument pas compatibles.

Architecture des ordinateurs 44

Les mémoires ISET Mahdia

V.2. Les mémoires mortes (ROM)

Pour certaines applications, il est nécessaire de pouvoir conserver des informations

de façon permanente même lorsque l'alimentation électrique est interrompue. On

utilise alors des mémoires mortes ou mémoires à lecture seule (ROM : Read Only

Memory). Ces mémoires sont non volatiles. Ces mémoires, contrairement aux RAM, ne

peuvent être que lue. L’inscription en mémoire des données restent possible mais est

appelée programmation. Suivant le type de ROM, la méthode de programmation

changera. Il existe donc plusieurs types de ROM :

• ROM

• PROM

• EPROM

• EEPROM

• FLASH EPROM

V.2.1. LA ROM

Elle est programmée par le fabricant et son contenu ne peut plus être ni modifié,

ni effacé par l'utilisateur.

Structure :

Cette mémoire est composée d'une matrice dont la programmation s’effectue en

reliant les lignes aux colonnes par des diodes.

Avantages :

• Densité élevée

• Non volatile

• Mémoire rapide

Architecture des ordinateurs 45

Les mémoires ISET Mahdia

Inconvénients :

• Écriture impossible

• Modification impossible (toute erreur est fatale)

• Délai de fabrication (3 à 6 semaines)

• Obligation de grandes quantités en raison du coût élevé qu'entraîne la

production du masque et le processus de fabrication

V.2.2. La PROM

C’est une ROM programmable (Programmable ROM) qui peut être programmée

une seule fois par l'utilisateur.

La programmation est réalisée à partir d’un programmateur spécifique.

Structure :

Les liaisons à diodes de la ROM sont remplacées par des fusibles pouvant être

détruits ou des jonctions pouvant être court-circuitées.

Avantages :

• Identiquement à la ROM

• Claquage en quelques minutes

• Coût relativement faible

Inconvénients :

• Modification impossible (toute erreur est fatale).

V.2.3. L’EPROM ou UV-EPROM

Pour faciliter la mise au point d'un programme ou tout simplement permettre une

erreur de programmation, il est intéressant de pouvoir reprogrammer une PROM. La

technique de claquage utilisée dans celles-ci ne le permet évidemment pas. L'EPROM

(Erasable Programmable ROM) est une PROM qui peut être effacée.

Avantages :

• Reprogrammable et non Volatile

Inconvénients :

• Impossible de sélectionner une seule cellule à effacer

• Impossible d’effacer la mémoire in-situ.

• l’écriture est beaucoup plus lente que sur une RAM. (environ 1000x)

Architecture des ordinateurs 46

Les mémoires ISET Mahdia

V.2.4. L’EEPROM

L’EEPROM (Electically EPROM) est une mémoire programmable et effaçable

électriquement. Elle répond ainsi à l’inconvénient principal de l’EPROM et peut être

programmée in situ (en place).

Avantages :

• Comportement d'une RAM non Volatile.

• Programmation et effacement mot par mot possible.

Inconvénients :

• Très lente pour une utilisation en RAM.

• Coût de réalisation.

V.2.5. La FLASH EPROM

La mémoire Flash s'apparente à la technologie de l’EEPROM, programmable et

effaçable électriquement. Il existe deux technologies qui se différencient par

l’organisation de leurs réseaux mémoire : l’architecture NOR et NAND.

Flash NOR :

Structure : propose un assemblage des cellules élémentaires de mémorisation en

parallèle avec les lignes de sélection comme dans une EEPROM classique.

Programmation : Il autorise un adressage aléatoire qui permet de la programmer

octet par octet.

Avantages :

• Comportement d'une RAM non Volatile

• Programmation et effacement mot par mot possible

• Temps d’accès faible

Inconvénients :

Architecture des ordinateurs 47

Les mémoires ISET Mahdia

• Lenteur de l’écriture/ lecture par paquet

• Coût

Flash NOR :

Structure :

Il propose un assemblage en série de ces mêmes cellules avec les lignes de sélection.

Programmation :

Accès séquentiel aux données et permettra seulement une programmation par

secteur comme sur un disque dur.

Avantages :

• Comportement d'une RAM non Volatile.

• Forte densité d’intégration

• Coût réduit.

• Rapidité de l’écriture/lecture par paquet

• Consommation réduite

Inconvénients :

• Ecriture/lecture par octet impossible.

• Interface E/S indirecte

D’un point de vue pratique, la différence majeure entre NOR et NAND tient à leurs

interfaces, la structure NAND autorise une implantation plus dense grâce à une taille

de cellule approximativement 40 % plus petite que la structure NOR.

La Flash EPROM a connu un essor très important ces dernières années avec

le boom de la téléphonie portable et des appareils multimédia (PDA, appareil photo

numérique, lecteur MP3, etc.).

V.3. Formats de barrettes de mémoire vive

Il existe de nombreux types de mémoires vives. Celles-ci se présentent toutes sous

la forme de barrettes de mémoire enfichables sur la carte-mère.

Les premières mémoires se présentaient sous la forme de puces appelées DIP

(Dual Inline Package). Désormais les mémoires se trouvent généralement sous la forme

Architecture des ordinateurs 48

Les mémoires ISET Mahdia

de barrettes, c'est-à-dire

dire des cartes enfichables dans des connecteurs prévus à cet effet.

On distingue habituellement trois types de barrettes de RAM :

les barrettes au format SIMM (Single Inline Memory Module) : il s'agit de circuits

imprimés dont une des faces possède des puces de mémoire.

Il existe deux types de barrettes SIMM, selon le nombre de connecteurs :

• Les barrettes SIMM à 30 connecteurs (dont les dimensions sont 89x13mm) sont des

mémoires 8 bits qui équipaient les premières générations de PC (286, 386).

• Les barrettes SIMM à 72 connecteurs (dont les dimensions sont 108x25mm) sont des

mémoires capables de gérer 32 bits de données simultanément. Ces mémoires

équipent des PC allant du 386DX aux premiers Pentium.

Sur ces derniers le processeur travaille avec un bus de données d'une largeur de 64 bits,

c'est la raison pour laquelle il faut absolument équiper ces ordinateurs de deux

barrettes SIMM. Il n'est pas possible d'installer des barrettes 30

3 broches sur des

emplacements à 72 connecteurs dans la mesure où un détrompeur (encoche au centre

des connecteurs) en empêche l'enfichage.

les barrettes au format DIMM (Dual Inline Memory Module) sont des mémoires 64

bits, ce qui explique pourquoi il n'est

n'est pas nécessaire de les apparier. Les barrettes

DIMM possèdent des puces de mémoire de part et d'autre du circuit imprimé et ont

également 84 connecteurs de chaque côté, ce qui les dote d'un total de 168 broches. En

plus de leurs dimensions plus grandes que

que les barrettes SIMM (130x25mm) ces

barrettes possèdent un second détrompeur pour éviter la confusion.

Architecture des ordinateurs 49

Les mémoires ISET Mahdia

Il peut être intéressant de noter que les connecteurs DIMM ont été améliorés afin

de faciliter leur insertion grâce à des leviers situés de part et d'autre du connecteur.

Il existe en outre des modules de plus petite taille, appelés SO DIMM (Small Outline

DIMM), destinés aux ordinateurs portables. Les barrettes SO DIMM comportent

uniquement 144 broches pour les mémoires 64 bits et 77 pour les mémoires 32 bits.

les barrettes au format RIMM (Rambus Inline Memory Module, appelées

également RD-RAM ou DRD-RAM) sont des mémoires 64 bits développée par

la société Rambus, possèdant 184 broches. Ces barrettes possèdent deux encoches de

repérage (détrompeurs), évitant tout risque de confusion avec les modules précédents.

Compte tenu de leur vitesse de transfert élevée, les barrettes RIMM possèdent un film

thermique chargé d'améliorer la dissipation de la chaleur.

Comme dans le cas des DIMM, il existe des modules de plus petite taille, appelés SO

RIMM (Small Outline RIMM), destinés aux ordinateurs portables. Les barrettes SO

RIMM comportent uniquement 160 broches.

VI. Mémoire cache

La mémoire cache (également appelée antémémoire ou mémoire tampon) est une

mémoire rapide permettant de réduire les délais d'attente des informations stockées en

mémoire vive. En effet, la mémoire centrale de l'ordinateur possède une vitesse bien

moins importante que le processeur. Il existe néanmoins des mémoires beaucoup plus

rapides, mais dont le coût est très élevé. La solution consiste donc à inclure ce type de

mémoire rapide à proximité du processeur et d'y stocker temporairement les

principales données devant être traitées par le processeur.

Figure 9 : Rôle de la mémoire cache

Architecture des ordinateurs 50

Les mémoires ISET Mahdia

Pour conclure, la mémoire cache a pour fonction d'accélérer les communications

entre un microprocesseur et un composant servant à stocker les données (RAM, disque

dur). Mais elle n'accélère pas la vitesse de la RAM ou du disque dur.

Lorsque le microprocesseur a besoin d'une donnée, il regarde si elle est disponible

dans la mémoire cache, si ce n'est pas le cas, il va la chercher dans l'unité de stockage et

en même temps la dépose dans la mémoire cache. Ainsi la prochaine fois qu'il aura

besoin de cette information, il y accédera directement par la mémoire cache et donc

plus rapidement.

Les ordinateurs récents possèdent plusieurs niveaux de mémoire cache :

Figure 10 : Différents niveaux de mémoire d'un microprocesseur

La mémoire cache de premier niveau (appelée L1 Cache, pour Level 1 Cache) est

directement intégrée dans le processeur. Elle se subdivise en deux :

• Le cache d'instructions, qui contient les instructions issues de la mémoire vive

puis décodées avant leurs arrivées.

• Le cache de données, qui contient des données issues de la mémoire vive

et les données récemment utilisées lors des opérations du processeur.

Les caches du premier niveau sont très rapides d'accès. Leur délai d'accès tend

à s'approcher de celui des registres internes aux processeurs.

La mémoire cache de second niveau (appelée L2 Cache, pour Level 2 Cache) sert

d'intermédiaire entre le cache L1 et la mémoire RAM. Il ne différencie pas données

et programmes, il est moins rapide que le cache L1, mais sa taille est plus

importante de 256 Ko à 2 Mo, voire plus. Ce cache a subit de nombreuses

Architecture des ordinateurs 51

Les mémoires ISET Mahdia

évolutions, et se retrouve aujourd'hui intégré dans le microprocesseur. Toutefois

s'il est intégré, il n'est pas imbriqué comme le cache L1. Cela veut dire que changer

la taille du cache L1 implique souvent une modification de l'architecture

du processeur, ce n'est pas le cas du cache L2. Ceci permet de proposer

des microprocesseurs disposant de différentes tailles de cache L2.

La mémoire cache de troisième niveau (appelée L3 Cache, pour Level 3 Cache)

ce type de cache est aujourd'hui courant sur des machines haut de gamme.

Jusqu'à présent, ce type de cache a toujours été composé de mémoire SRAM,

et implanté sur la carte mère. Sa taille varie de 1 Mo à 8 Mo (valeur généralement

constatée mais il n'y a pas de limitation technique).

Tous ces niveaux de cache permettent de réduire les temps de latence des différentes

mémoires lors du traitement et du transfert des informations. Pendant que

le processeur travaille, le contrôleur de cache de premier niveau peut s'interfacer avec

celui de second niveau pour faire des transferts d'informations sans bloquer

le processeur. De même, le cache de second niveau est interfacé avec celui

de la mémoire vive (cache de troisième niveau), pour permettre des transferts sans

bloquer le fonctionnement normal du processeur.

Architecture des ordinateurs 52

Vous aimerez peut-être aussi

- Bien débuter avec SQL: Exercices dans l'interface PhpMyAdmin et MySQLD'EverandBien débuter avec SQL: Exercices dans l'interface PhpMyAdmin et MySQLPas encore d'évaluation

- QCM Généralités InformatiquesDocument11 pagesQCM Généralités InformatiquesGhislaine REMONDO100% (1)

- Les 3 Jeunes Detectives (037) - Silence, On Tue ! - Alfred HitchcockDocument121 pagesLes 3 Jeunes Detectives (037) - Silence, On Tue ! - Alfred HitchcockEric LefrançaisPas encore d'évaluation

- Coefficient K, Devis Estimatif, Quantitatif Et PlanificationDocument21 pagesCoefficient K, Devis Estimatif, Quantitatif Et PlanificationMarco JoyPas encore d'évaluation

- Bus MémoiresDocument23 pagesBus Mémoiresramzi ayadiPas encore d'évaluation

- Les Composants DordinateurDocument11 pagesLes Composants DordinateurMamoudou DiengPas encore d'évaluation

- Attachement Du ChantierDocument10 pagesAttachement Du ChantierOussamaBahloul100% (1)

- Med 5an Cas Clinique1 GynecoDocument7 pagesMed 5an Cas Clinique1 GynecoIbtissem TissamPas encore d'évaluation

- Cours-Architectures Des Processeurs-Mr Nizar TOUJANIDocument115 pagesCours-Architectures Des Processeurs-Mr Nizar TOUJANIIbtihel MechleouiPas encore d'évaluation

- Les MémoiresDocument7 pagesLes Mémoiresmayssemzinoubi610Pas encore d'évaluation

- Les MémoireDocument27 pagesLes MémoireKouassi Francis KouamePas encore d'évaluation

- Chapitre II: Les Mémoires À Semi-ConducteurDocument15 pagesChapitre II: Les Mémoires À Semi-ConducteurKahel el hadj chikhPas encore d'évaluation

- Chapitre 2 - 2015 - 2016Document10 pagesChapitre 2 - 2015 - 2016bassemkallel0Pas encore d'évaluation

- La Mémoire CentraleDocument10 pagesLa Mémoire CentraleSafa DebishiPas encore d'évaluation

- Chap 3 MémoiresDocument14 pagesChap 3 MémoiresDarius StevesPas encore d'évaluation

- 2 Les Meemoires v19Document8 pages2 Les Meemoires v19Ettaoufik AbdelazizPas encore d'évaluation

- Cours Electronique Numérique PDFDocument12 pagesCours Electronique Numérique PDFImad EdinePas encore d'évaluation

- Arch Des OrdDocument6 pagesArch Des Ordmayssemzinoubi610Pas encore d'évaluation

- Notes de Cours (Mémoires)Document9 pagesNotes de Cours (Mémoires)Wajdi BelhajPas encore d'évaluation

- Chapitre 5 Les Fonctions MemoiresDocument5 pagesChapitre 5 Les Fonctions Memoiresadda chariPas encore d'évaluation

- Les Mémoires - 103612Document9 pagesLes Mémoires - 103612Sagesse TetyaPas encore d'évaluation

- CH 2Document11 pagesCH 2HIMA SAFIPas encore d'évaluation

- Architecture de Base ChapiDocument5 pagesArchitecture de Base ChapiMoTaALPas encore d'évaluation

- Chapitre2 Système A MicroprocesseurDocument11 pagesChapitre2 Système A MicroprocesseurÑar ĎjesPas encore d'évaluation

- Chapitre1 - Licence MicroprocesseurDocument19 pagesChapitre1 - Licence MicroprocesseurAbdallah RehabPas encore d'évaluation

- Operating Systems FundamentalsDocument172 pagesOperating Systems FundamentalsAbdel GansonrePas encore d'évaluation

- Aller 5 Memoire 1Document8 pagesAller 5 Memoire 1Slimen Mohamed SadokPas encore d'évaluation

- Architecture de BaseDocument7 pagesArchitecture de BaseDivin BoudzoumouPas encore d'évaluation

- Le Processeur: Souvent Implémenté Sur La Carte MèreDocument32 pagesLe Processeur: Souvent Implémenté Sur La Carte MèreBilelbhPas encore d'évaluation

- Ch7 MemoiresDocument52 pagesCh7 MemoiressinchicovichPas encore d'évaluation

- CHAPITRE 7 Architecture Des Mémoires Et Des ProcesseursDocument14 pagesCHAPITRE 7 Architecture Des Mémoires Et Des ProcesseursHappy lifePas encore d'évaluation

- Cours7 MemoiresDocument12 pagesCours7 MemoiresRoi du SilencePas encore d'évaluation

- Cours 4Document2 pagesCours 4Nidal LaatabPas encore d'évaluation

- 1architecture MaterielleDocument4 pages1architecture MateriellewikiamazPas encore d'évaluation

- InformatiqueDocument15 pagesInformatiqueDiakaridia CoulibalyPas encore d'évaluation

- Corrtd 1Document7 pagesCorrtd 1wafa wafaPas encore d'évaluation

- Chapitre 1-2Document37 pagesChapitre 1-2BadjoPas encore d'évaluation

- Informatique s2 Fini PDFDocument9 pagesInformatique s2 Fini PDFMstr Belkac100% (1)

- Chap1 DLXDocument10 pagesChap1 DLXmed100% (1)

- Archi OrdiDocument7 pagesArchi Ordia.rharrabPas encore d'évaluation

- Généralités Sur La MCDocument25 pagesGénéralités Sur La MCSaif Eddine khedhriPas encore d'évaluation

- Wa0011Document41 pagesWa0011Naima MekPas encore d'évaluation

- Memoires CompletDocument14 pagesMemoires CompletAiche MokhtarPas encore d'évaluation

- EEA L3 - ArchitectureDocument30 pagesEEA L3 - ArchitectureMoussa Amadou AlmoustaphaPas encore d'évaluation

- Hadji MemoiresDocument11 pagesHadji MemoiresSaber AbderrahmanePas encore d'évaluation

- Devoir 1Document6 pagesDevoir 1mima.20sabrinePas encore d'évaluation

- Ch2. Arch - OrdDocument32 pagesCh2. Arch - Ordmrrr karouiPas encore d'évaluation

- Composants Corrige tdn4Document2 pagesComposants Corrige tdn4Emma DjomoPas encore d'évaluation

- CHAPITRE IV Archi Syst. Programmés PDFDocument40 pagesCHAPITRE IV Archi Syst. Programmés PDFTimble PuteurPas encore d'évaluation

- CHAPITRE IV Archi Syst. ProgrammésDocument40 pagesCHAPITRE IV Archi Syst. ProgrammésTimble PuteurPas encore d'évaluation

- Cours 02 PDFDocument11 pagesCours 02 PDFRémi OuedraogoPas encore d'évaluation

- Corrigé Série de TD N° 3Document5 pagesCorrigé Série de TD N° 3Alaa MessaoudPas encore d'évaluation

- Cours Micro Controleur Architecture STSDocument7 pagesCours Micro Controleur Architecture STSMAHAMADOU TOUNGARAPas encore d'évaluation

- Ch03 Les MémoiresDocument5 pagesCh03 Les Mémoiresnesrine ninaPas encore d'évaluation

- RapportDocument36 pagesRapportMaryem BaihatPas encore d'évaluation

- ch7 Memoires PDFDocument9 pagesch7 Memoires PDFYoucef Br'sPas encore d'évaluation

- Cours-No-02 Calculateur Et InterfaçageDocument4 pagesCours-No-02 Calculateur Et Interfaçagestone freePas encore d'évaluation

- Cours 5 - Les MémoiresDocument4 pagesCours 5 - Les Mémoiresayad.abderahim89Pas encore d'évaluation

- Les Composants Dune STADocument8 pagesLes Composants Dune STAbourguibaPas encore d'évaluation

- Info CoursDocument32 pagesInfo Coursyosra laayouniPas encore d'évaluation

- Module 4 - Les MémoiresDocument12 pagesModule 4 - Les Mémoireskoffigbedji77Pas encore d'évaluation

- Seminaire Informatique Partie 2Document37 pagesSeminaire Informatique Partie 2r.rostagnoPas encore d'évaluation

- Compression d'images: Techniques efficaces pour l'optimisation des données visuellesD'EverandCompression d'images: Techniques efficaces pour l'optimisation des données visuellesPas encore d'évaluation

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasD'EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasPas encore d'évaluation

- Cahier de Poutres Bloc Administration 1Document8 pagesCahier de Poutres Bloc Administration 1Ourajim issamPas encore d'évaluation

- Corbin 1458816683Document1 pageCorbin 1458816683rodrigomichellPas encore d'évaluation

- VRAI - FAUX DEVOIR (Sujet)Document1 pageVRAI - FAUX DEVOIR (Sujet)karim sharifPas encore d'évaluation

- Video RO1Document39 pagesVideo RO1lovebooksPas encore d'évaluation

- Exo 18 Partitifs en LigneDocument1 pageExo 18 Partitifs en LigneMaria SousaPas encore d'évaluation

- Dégradations de ChausséeDocument13 pagesDégradations de Chaussée'Tarik Louati50% (2)

- Chapitre 4Document12 pagesChapitre 4zakariamaazouztradingPas encore d'évaluation

- Notice de La Commande Numerique DSP BRAXESDocument11 pagesNotice de La Commande Numerique DSP BRAXESHassan HassanPas encore d'évaluation

- Signalisation Routière - Verticale Et Horizontale - OrnikarDocument7 pagesSignalisation Routière - Verticale Et Horizontale - OrnikarTalloudPas encore d'évaluation

- Avp Loi 67.15 FRDocument9 pagesAvp Loi 67.15 FRSerge KohemunPas encore d'évaluation

- Protocole KINE PREOP Etude Pilote Sur La Préhabilitation Pulmonaire en Libéral Dans Le Cadre de La Chirurgie Thoracique Pulmonaire OncologiqueDocument103 pagesProtocole KINE PREOP Etude Pilote Sur La Préhabilitation Pulmonaire en Libéral Dans Le Cadre de La Chirurgie Thoracique Pulmonaire OncologiqueSelmaPas encore d'évaluation

- BrainstormingDocument4 pagesBrainstormingndeyadiop1203Pas encore d'évaluation

- Rapport RFIDDocument29 pagesRapport RFIDed-fer666Pas encore d'évaluation

- Plan Comptable Minimum NormaliséDocument32 pagesPlan Comptable Minimum NormaliséRené yvesPas encore d'évaluation

- Voyage de La Grèce PDFDocument539 pagesVoyage de La Grèce PDFspéculairePas encore d'évaluation

- 1901 Vierendeel. Stabilite Des Constructions. Tome III PDFDocument137 pages1901 Vierendeel. Stabilite Des Constructions. Tome III PDFmouradPas encore d'évaluation

- Cours de Absorption Des NutrimentsDocument67 pagesCours de Absorption Des NutrimentsHamidPas encore d'évaluation

- TMDDocument10 pagesTMDBANIPas encore d'évaluation

- Parler de La Nourriture Mars 2021 FinaleDocument19 pagesParler de La Nourriture Mars 2021 FinalepeterPas encore d'évaluation

- Introduction À La Science Des Matériaux Propriétés Générales Des MatériauxDocument27 pagesIntroduction À La Science Des Matériaux Propriétés Générales Des MatériauxDelphin Kandolo100% (1)

- 1-Rem Commande - PrédictiveDocument28 pages1-Rem Commande - PrédictiveLots of lovePas encore d'évaluation

- 1Document8 pages1Ladys Ruth Caballero PeluffoPas encore d'évaluation

- Revenu 1357Document28 pagesRevenu 1357concombre2607Pas encore d'évaluation

- 15 May 2013Document343 pages15 May 2013Download_Scribd_stufPas encore d'évaluation

- Mouvements Plans Cours 1 2Document8 pagesMouvements Plans Cours 1 2kenza.elkansouriPas encore d'évaluation

- Brand PriceDocument6 pagesBrand PriceBonnesAffairesConstantine100% (1)