Académique Documents

Professionnel Documents

Culture Documents

Cours Micro Controleur Architecture STS

Transféré par

MAHAMADOU TOUNGARATitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cours Micro Controleur Architecture STS

Transféré par

MAHAMADOU TOUNGARADroits d'auteur :

Formats disponibles

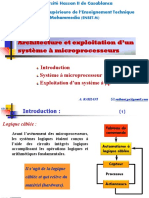

COURS ARCHITECTURE D’UN SYSTEME A MICROPROCESSEUR

On se propose d’exposer les principes de fonctionnement d'un système microprogrammé, ainsi

que les définitions de base ayant trait aux microprocesseurs et leur environnement. Le but étant

de se familiariser avec les termes utilisés.

Tous les concepts, termes et abréviations déterminés introduits dans ce chapitre sont

fondamentaux et devront être bien assimilés ; ils permettront de décrire d’une manière précise

les systèmes et les composants présentés.

1 ) ORGANISATION FONCTIONNELLE DU TRAITEMENT DES INFORMATIONS

2 )ORGANISATION STRUCTURELLE D’UN SYSTEME MICROPROGRAMME

Les structures matérielles des systèmes de traitement de l’information sont essentiellement

organisées autour du microprocesseur.

Le microprocesseur est un circuit intégré complexe caractérisé par une très grande intégration

et doté de facultés fonctionnelles d’interprétation et d’exécution des instructions d’un

programme.

Comme dans tout circuit intégré, la technologie de fabrication impose au microprocesseur des

caractéristiques de : - * temps de réponse,

Cours µC architecture STS.doc

COURS ARCHITECTURE D’UN SYSTEME A MICROPROCESSEUR

2

* consommation.

Actuellement, l’avenir du microprocesseur est préservé par l’arrivée de composants

extrêmement performants tels que les fameux Pentium III, AMD K6 3, Celeron, Athlon,…

pouvant fonctionner à des fréquences de l’ordre de 500MHz et en constante évolution.

Cependant, le microprocesseur ne peut

fonctionner sans un environnement minimal

comportant :

- une zone de mémoire vive pour les données et

résultats,

- une zone de mémoire morte pour les

programmes ou systèmes d’exploitation,

- une ou plusieurs interfaces pour les

périphériques.

Entre les différents ensembles, les liaisons fonctionnelles sont assurées par trois groupes de

conducteurs en parallèles appelés bus et ayant chacun une fonction spécifique.

• le bus de données : (Data bus), bus bidirectionnel qui assure le transfert des

informations entre le microprocesseur et son environnement et inversement ; son nombre de

lignes est égal à la capacité de traitement du microprocesseur : 8, 16, 32 ou 64 bits.

(Habituellement nommés D0 à D7 pour un bus 8 bits).

• Le bus d’adresse : (Adress bus), bus unidirectionnel qui permet la sélection du

destinataire des informations à traiter dans un espace mémoire ‘adressable’ qui peut avoir 2n

emplacements ; n étant le nombre de conducteurs du bus d’adresse, habituellement n = 16 (A0

à A15), pour un processeur 8 bits.

• Le bus de commande : (Control bus), bus constitué par quelques conducteurs qui

assurent la synchronisation des flux d’infos sur le bus de données et d’adresse.

Les fonctions du microprocesseur sont variées :

• organiser l’enchaînement des tâches précisées dans la mémoire programme,

• rythmer et synchroniser l’exécution des tâches,

• analyser le contenu du programme, sélectionner, gérer et commander les circuits

nécessaires à l’exécution de chaque tâche,

• prendre en compte les informations extérieures au système.

3 ) L’ENVIRONNEMENT DU MICROPROCESSEUR

3.1 ) Mémoire :

Un circuit intégré de type mémoire permet de stocker et de restituer une très grande quantité

d’informations correspondant à N mots de n bits.

Une mémoire est constituée par un assemblage de cellules mémoires. Dans chaque cellule, il

est possible d’écrire, de conserver et d’extraire un élément d’information.

Pour gérer cet ensemble de cellules mémoires, le circuit comprend également des sélecteurs

d’adresse, des amplificateurs, des commandes de modes de fonctionnement…

Il existe deux familles de mémoires :

Cours µC architecture STS.doc

COURS ARCHITECTURE D’UN SYSTEME A MICROPROCESSEUR

3

- les mémoires vives, RAM (Random Access Memory) : mémoires qui peuvent être lues

et écrites en permanence. Elle contient habituellement les données pendant le traitement d’un

programme. Elle est effacée en cas de coupure d’énergie,

-

- les mémoires mortes, ROM (Read Only Memory) : Avec ces mémoires, seule la

lecture est possible. Les données qu’elle contient sont enregistrées par le concepteur du

système. En fonction de leur construction, il existe différents types :

- PROM, Programmable ROM : ROM programmable,

- EPROM, Erasable PROM : PROM effaçable,

- EEPROM, Electric Erasable PROM : PROM effaçable électriquement.

3.2 ) Interface :

L’interfaçage est l’ensemble matériel qui permet de transférer les données entre le système de

traitement de l’information et les périphériques.

On distingue les interfaces série et les interfaces parallèles.

3.3 ) Périphériques :

Les périphériques sont les matériels extérieurs

aux systèmes informatiques. On y retrouve :

- tous les matériels qui servent à la

communication de l’homme avec le système

informatique : écran, clavier, souris…

- tous les systèmes de stockage des

informations : lecteur de disquettes et CDROM,

disque dur, lecteur de bandes magnétiques…

- tous les appareils qui servent à traduire les

données sur papier : imprimante à aiguilles, jet

ou bulles d’encre, laser…

- tous les appareils qui servent à acquérir des

informations extérieures : lecteur de cartes

magnétiques, scanner, appareil photo

numérique, carte d’acquisition son et vidéo…

Rappel : Capacité d'un circuit mémoire

La capacité mémoire caractérise le nombre de bits ou d'octets mémorisables par un circuit

mémoire. Elle est exprimée en clair :

64K x 8 = 512K, c’est un circuit qui mémorise 64K mots de 8bits (1 octet), sa capacité est donc

de 512K.

64K x 16 = 1024K, c’est un circuit qui mémorise 64K mots de 16bits, sa capacité est de 1024K

= 1Méga.

1K = 1024 ; 1Méga = 1024K.

Un circuit mémoire de 10 lignes d'adresse = 210 =1024 , de 8 lignes de données, ce circuit

mémoire 1K de mots binaires de 1octet, il a donc une capacité de 1024 x 8 = 8192 bits ou 8

Kbits ou 1024 octets ou 1koctet.

.

Cours µC architecture STS.doc

COURS ARCHITECTURE D’UN SYSTEME A MICROPROCESSEUR

4

4 ) LE DECODAGE D’ADRESSE

Le décodage d’adresse doit permettre de satisfaire l’échange entre le microprocesseur et ses

périphériques, ceci dans les meilleures conditions afin d’éviter les conflits. Ainsi, à une adresse

présentée par le microprocesseur, devra répondre un seul périphérique (RAM, P.I.A. ..etc.).

Principe de gestion des zones d’adresses :

Prenons l’exemple ci-contre

d’une mémoire RAM (4K*4)

situé dans l’espace mémoire

adressable.

On désire déterminer la plage

d’adresses utilisée par ce

périphérique ; le décodage

d’adresse étant réalisé par une

simple structure à portes

logiques.

a. Quel est le rôle de la broche R / W sur un circuit « Mémoire » ?

b. Quel est le rôle de la broche CS ?

c. De combien de bits est constituée la donnée stockée ?

d. De quelle capacité est cette mémoire ( en Kquartets puis Kbits puis Ko ) ?

e. Comment sélectionne-t-on l’adresse d’une donnée ?

Cours µC architecture STS.doc

COURS ARCHITECTURE D’UN SYSTEME A MICROPROCESSEUR

5

f. Quel doit être l’état du signal VMA (valid memory access) pour sélectionner cette

mémoire ?

g. Déterminer l’état des lignes A12 à A15 qui sélectionnent la mémoire .

h. Donner la plage d’adresse utilisée par cette mémoire.

Dans le cas où plusieurs périphériques seraient à adresser dans le même espace mémoire, il

convient d’utiliser une structure appropriée de manière à alléger la structure du décodage

d’adresses. Très souvent, un simple décodeur/démultiplexeur (3 vers 8 par exemple) suffit à

réaliser la fonction. Le décodage d’adresses est alors aussi simple à déterminer pour peu que

l’on dispose de la documentation constructeur du circuit logique utilisé.

Le schéma structurel proposé à la page suivante constitue la carte calculateur du système

technique : « Analyseur de Fraises-scies ».

Elle est composée d’un microprocesseur 8 bits (U1 : Motorola, 6809) autour duquel sont

organisés les périphériques suivants :

- U6 : Interface série programmable (ACIA 6850),

- U7, U9 : Interface programmable.

- U10 : Temporisateur programmable (Timer 6840),

- U14 : Mémoire EPROM 8k*8 (2764),

- U15 : Mémoire RAM 8k*8 (6264),

Ils sont tous intégrés dans l’espace mémoire adressable ($0000 à $FFFF) ; chacun ayant sa

plage définie par un circuit décodeur/démultiplexeur 3 vers 8.

Cours µC architecture STS.doc

COURS ARCHITECTURE D’UN SYSTEME A MICROPROCESSEUR

6

QUESTIONNAIRE

1. Identifier sur le schéma structurel et décrire le circuit utilisé pour le décodage d’adresses.

2. Proposer un schéma fonctionnel de l’organisation de la fonction « décodage d’adresses »

comprenant le bus d’adresses, le circuit caractérisé à la question 1. et les périphériques

gérés par le microprocesseur.

3. Quel doit être l ‘état des signaux E et Q (broche 34 et 35 de U1) pour permette la validation

du circuit U4 ?

4. Que est le rôle des broches CE ou CS et RS sur un circuit logique ?

5. Quel est le niveau logique présenté sur la sortie sélectionnée du circuit U4 ?

Justifier cet état.

6. Déterminer la capacité des circuits U14 et U15.

7. Donner l’équation logique de : CS2 (U9) , CS2 (U7) , CS2 (U6) , CS0 (U10) , CS1(U15) , CE (U14)

en fonction de A15, A14, A13.

8. Etablir, à partir du décodage d’adresses, l’occupation de l’espace mémoire par les circuits

U6, U7, U9, U10, U14, U15.

Circuit @ A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

U6 +

-

U7 +

-

U9 +

-

U10 +

-

U14 +

-

U15 +

-

Compléter le tableau ci-dessous :

Domaine d’adresses utilisées Sélection des registres internes

Composant Type Adresse la Adresse la Adresse la adresse la

Plus basse plus haute Plus basse plus haute

U6 6850

ACIA

U7

U9

U10

U14

U15

Cours µC architecture STS.doc

COURS ARCHITECTURE D’UN SYSTEME A MICROPROCESSEUR

7

Cours µC architecture STS.doc

Vous aimerez peut-être aussi

- Traitement de L'information PDFDocument6 pagesTraitement de L'information PDFFarid AfifiPas encore d'évaluation

- Chapitre 2 Systemes A Base de Microprocesseurs - C2I2S - S1Document29 pagesChapitre 2 Systemes A Base de Microprocesseurs - C2I2S - S1Karym ElhoussinePas encore d'évaluation

- Partie1 Introduction Cours PDocument15 pagesPartie1 Introduction Cours PKhadija HtPas encore d'évaluation

- Chapitre 1-2Document37 pagesChapitre 1-2BadjoPas encore d'évaluation

- CHAPITRE IV Archi Syst. Programmés PDFDocument40 pagesCHAPITRE IV Archi Syst. Programmés PDFTimble PuteurPas encore d'évaluation

- CHAPITRE IV Archi Syst. ProgrammésDocument40 pagesCHAPITRE IV Archi Syst. ProgrammésTimble PuteurPas encore d'évaluation

- chapitre1_licence MicroprocesseurDocument19 pageschapitre1_licence MicroprocesseurAbdallah RehabPas encore d'évaluation

- TD1 19corrDocument5 pagesTD1 19corrSaid ReganiPas encore d'évaluation

- Informatique IndustrielleDocument16 pagesInformatique IndustrielleNo RayaPas encore d'évaluation

- Architecture Des Ordinateurs Cours-1Document14 pagesArchitecture Des Ordinateurs Cours-1Louis KouassiPas encore d'évaluation

- IUGET ArchitectureMicroprocesseurDocument21 pagesIUGET ArchitectureMicroprocesseurFabrice FotsoPas encore d'évaluation

- Architecture Et Technologies Des Systemes InformatiquesDocument74 pagesArchitecture Et Technologies Des Systemes InformatiquesHamzaoui AnasPas encore d'évaluation

- Cours-Architectures Des Processeurs-Mr Nizar TOUJANIDocument115 pagesCours-Architectures Des Processeurs-Mr Nizar TOUJANIIbtihel MechleouiPas encore d'évaluation

- Cours No 01 Approche Des Systèmes A Microprocesseurs.Document4 pagesCours No 01 Approche Des Systèmes A Microprocesseurs.MAROUA TWALBIAPas encore d'évaluation

- Cours Microcontrôleur Microprocesseur 66 PDFDocument28 pagesCours Microcontrôleur Microprocesseur 66 PDFAbderrahim RiadPas encore d'évaluation

- CH 1Document20 pagesCH 1raghda amamiPas encore d'évaluation

- QCM Généralités InformatiquesDocument11 pagesQCM Généralités InformatiquesGhislaine REMONDO100% (1)

- Microprocesseur 6800 Chap1Document6 pagesMicroprocesseur 6800 Chap1Mountasser KhalPas encore d'évaluation

- Notes de Cours (chap1-IntroductionHistorique)Document4 pagesNotes de Cours (chap1-IntroductionHistorique)Wajdi BelhajPas encore d'évaluation

- Chap1 DLXDocument10 pagesChap1 DLXmed100% (1)

- Chapitre I Introduction Et RappelsDocument14 pagesChapitre I Introduction Et RappelsSanae BOUNOUAPas encore d'évaluation

- Chapitr 001Document5 pagesChapitr 001oussama bouguerraPas encore d'évaluation

- Cours 2Document8 pagesCours 2Achraf HouilaPas encore d'évaluation

- Architecture de BaseDocument7 pagesArchitecture de BaseDivin BoudzoumouPas encore d'évaluation

- Chaiptre 1 Systeme A MicroprocesseurDocument13 pagesChaiptre 1 Systeme A MicroprocesseurStive TagnePas encore d'évaluation

- CHAPITRE 7 Architecture Des Mémoires Et Des ProcesseursDocument14 pagesCHAPITRE 7 Architecture Des Mémoires Et Des ProcesseursHappy lifePas encore d'évaluation

- Corrtd 1Document7 pagesCorrtd 1wafa wafaPas encore d'évaluation

- hcs12 PDFDocument65 pageshcs12 PDFachraf_djyPas encore d'évaluation

- Info - Indus - Chap I - ARCHITECTURE DES SYSTEMES A MICROPROCESSEUR - ISGE - 2ADocument24 pagesInfo - Indus - Chap I - ARCHITECTURE DES SYSTEMES A MICROPROCESSEUR - ISGE - 2AThierry OuedraogoPas encore d'évaluation

- Systèmes MicroprogrammésDocument6 pagesSystèmes MicroprogrammésNasriMohsenPas encore d'évaluation

- Cours Microprocesseur Et MicrocontroleursimplDocument171 pagesCours Microprocesseur Et MicrocontroleursimplAbdou Super100% (1)

- Arch Des OrdDocument6 pagesArch Des Ordmayssemzinoubi610Pas encore d'évaluation

- Chapitre 5 Architecture Et Fonctionnement de Lordinateur PDFDocument25 pagesChapitre 5 Architecture Et Fonctionnement de Lordinateur PDFAlphonsePas encore d'évaluation

- Chapitre 1 CoursDocument17 pagesChapitre 1 CoursNouzha BoukoubaPas encore d'évaluation

- M - Microprocesseurs Et DSP-Chap2Document17 pagesM - Microprocesseurs Et DSP-Chap2MENANI ZineddinePas encore d'évaluation

- Chap 2Document5 pagesChap 2INESPas encore d'évaluation

- WWW - Cours Gratuit - Com Id 5297Document90 pagesWWW - Cours Gratuit - Com Id 5297Madjilem NayamPas encore d'évaluation

- Architecture de Base ChapiDocument5 pagesArchitecture de Base ChapiMoTaALPas encore d'évaluation

- Informatique-Introduction Unite CentraleDocument21 pagesInformatique-Introduction Unite CentraleAhmed SmailPas encore d'évaluation

- CHAPITRE 1 - GéneralitésDocument9 pagesCHAPITRE 1 - GéneralitésZERARKA Mohamed FawziPas encore d'évaluation

- Info TristanDocument14 pagesInfo TristanEulerPas encore d'évaluation

- Ec Gim334 - Dao - CaoDocument47 pagesEc Gim334 - Dao - CaoArmand EssPas encore d'évaluation

- TP 1 Info Indus07Document15 pagesTP 1 Info Indus07MOHAMED TAMZAITIPas encore d'évaluation

- Chapitre 1 - Généralités Sur Les Systèmes A Microprocesseur (2017-2018)Document7 pagesChapitre 1 - Généralités Sur Les Systèmes A Microprocesseur (2017-2018)Ali OuattaraPas encore d'évaluation

- Cours-Microproc 2018Document192 pagesCours-Microproc 2018Badr Eddine EL HAGAOUIPas encore d'évaluation

- Devoir N°2Document5 pagesDevoir N°2Khadija El AmouryPas encore d'évaluation

- Architecture Des Ordinateurs Etudiants - Partie I & IIDocument34 pagesArchitecture Des Ordinateurs Etudiants - Partie I & IIalphonsekama0Pas encore d'évaluation

- Leçon N°1: Presentation de L'Informatique Industrielle Et Des Systemes Micro-Programmes I - L'Informatique IndustrielleDocument120 pagesLeçon N°1: Presentation de L'Informatique Industrielle Et Des Systemes Micro-Programmes I - L'Informatique IndustrielleFulbert FissouPas encore d'évaluation

- Cours Microprocesseur ENSADocument138 pagesCours Microprocesseur ENSASheeya FilaliPas encore d'évaluation

- Microprocesseurs ATMEL Part1Document10 pagesMicroprocesseurs ATMEL Part1Mustapha ramziPas encore d'évaluation

- Cours Microcontrôleur Microprocesseur 23Document51 pagesCours Microcontrôleur Microprocesseur 23karima seghaierPas encore d'évaluation

- Examen ATODocument2 pagesExamen ATOAdos Agbidinoukoun100% (1)

- Composant Chapitre 03Document46 pagesComposant Chapitre 03Henri RayanPas encore d'évaluation

- Chapitre N°01Document14 pagesChapitre N°01Youssouf gairanPas encore d'évaluation

- InformatiqueDocument15 pagesInformatiqueDiakaridia CoulibalyPas encore d'évaluation

- Bien débuter avec SQL: Exercices dans l'interface PhpMyAdmin et MySQLD'EverandBien débuter avec SQL: Exercices dans l'interface PhpMyAdmin et MySQLPas encore d'évaluation

- Ingénierie Neuromorphique: La pratique consistant à utiliser des systèmes de circuits électriques analogiques pour imiter les structures neurobiologiques présentes dans le système nerveuxD'EverandIngénierie Neuromorphique: La pratique consistant à utiliser des systèmes de circuits électriques analogiques pour imiter les structures neurobiologiques présentes dans le système nerveuxPas encore d'évaluation

- Grille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesD'EverandGrille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesPas encore d'évaluation

- Machines de Jeux: Architecture des Consoles de Jeux VidéoD'EverandMachines de Jeux: Architecture des Consoles de Jeux VidéoÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Microprocesseurs Et MicrocontrolleursDocument250 pagesMicroprocesseurs Et MicrocontrolleursGuichi Omar100% (2)

- Automates Programmables Industriels (API)Document1 pageAutomates Programmables Industriels (API)Bonheur KambaPas encore d'évaluation

- LAA314 - 2016 - Chapitre 1Document28 pagesLAA314 - 2016 - Chapitre 1Akram BENACHOURPas encore d'évaluation

- CoursmicroreduitDocument87 pagesCoursmicroreduitapi-3826166100% (2)

- M07 - Utilisation D'un Micro-Ordinateur GE-REEDocument139 pagesM07 - Utilisation D'un Micro-Ordinateur GE-REEKesraoui HichemPas encore d'évaluation

- 2ème SI InformatiqueDocument240 pages2ème SI Informatiqueafrouk10% (1)

- Par 6 DiaposDocument75 pagesPar 6 DiaposNada DaPas encore d'évaluation

- Cours MicroprocessseursDocument55 pagesCours MicroprocessseursAyoub HmitouPas encore d'évaluation

- Cours E Les Systemes A MicroprocesseurDocument24 pagesCours E Les Systemes A MicroprocesseurAnasPas encore d'évaluation

- Architecture Du ProcesseurDocument5 pagesArchitecture Du ProcesseurLinda GachaPas encore d'évaluation

- Test QCMDocument5 pagesTest QCMFabrice Bernard100% (1)

- Travaux Dirigés 4 - TECHNOLOGIE Tle IMI - LTCDocument4 pagesTravaux Dirigés 4 - TECHNOLOGIE Tle IMI - LTCCyriaque NascimentoPas encore d'évaluation

- MicroProcesseurs Et ChipSetDocument44 pagesMicroProcesseurs Et ChipSetHachem Elyousfi0% (1)

- NSI 2019 2 OrdinateursDocument34 pagesNSI 2019 2 OrdinateursyaoPas encore d'évaluation

- Fascicule ArchitecturedesordinateursDocument6 pagesFascicule ArchitecturedesordinateurschatyasPas encore d'évaluation

- M07 - Utilisation Dun Micro OrdinateurDocument127 pagesM07 - Utilisation Dun Micro Ordinateurlahcen oubelaidPas encore d'évaluation

- COURSSSDocument36 pagesCOURSSSAbdelhadi EnnajihPas encore d'évaluation

- G2 Geologie Informatique GeneraleDocument93 pagesG2 Geologie Informatique GeneraleGuerschomPas encore d'évaluation

- Pi Ndeg73 InformatiqueDocument100 pagesPi Ndeg73 Informatiquemichel_r_91Pas encore d'évaluation

- Examen AO 2021 2022Document8 pagesExamen AO 2021 2022ghostninja745Pas encore d'évaluation

- Correction Examen AO 2021 2022Document4 pagesCorrection Examen AO 2021 2022ghostninja745Pas encore d'évaluation

- Cours 8086 2015-1Document105 pagesCours 8086 2015-1Dilane GhomsiPas encore d'évaluation

- 6 Structure Interne Des ProcesseursDocument10 pages6 Structure Interne Des ProcesseursNabila TouisiPas encore d'évaluation

- Cours 2 PP FRDocument22 pagesCours 2 PP FRNIKIEMA Francklin PowellPas encore d'évaluation

- Master-Parabole - Juin-2017-YounesDocument50 pagesMaster-Parabole - Juin-2017-YounesAmine EminePas encore d'évaluation

- Chapitre I SETDocument14 pagesChapitre I SETmaissaPas encore d'évaluation

- Architechture Matérielle D'un Systeme A MicroprocesseurDocument17 pagesArchitechture Matérielle D'un Systeme A MicroprocesseurSellé GueyePas encore d'évaluation

- CHAP2Document47 pagesCHAP2Boudiche SaebPas encore d'évaluation

- Cours Codesign Souhir 2102023Document22 pagesCours Codesign Souhir 2102023nassimarafa009Pas encore d'évaluation

- Architecture Des Systèmes Informatiques Parti1Document55 pagesArchitecture Des Systèmes Informatiques Parti1Pacome Chede100% (1)