Académique Documents

Professionnel Documents

Culture Documents

Ber51 06 07

Transféré par

Leroy Lionel SonfackTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Ber51 06 07

Transféré par

Leroy Lionel SonfackDroits d'auteur :

Formats disponibles

6 Bulletin des Energies Renouvelables N° 51 Bulletin des Energies Renouvelables N° 51 7

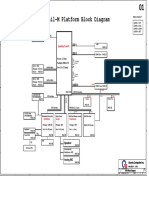

FPGA vs DSP appliqués aux convertisseurs de puissance eZdsp F2812

TMS320F2812 DSP

Spartan-3 XCS1000

FPGA

Clock 150 MHz 500 MHz

Peak MAC 150 M/s 3600 M/s

BEDDAR Antar, Maître de Recherche B RAM On Chip 18 kBytes 432+120 kBytes

Division Energies Solaire Photovoltaïque - CDER (Block+Distributed)

RAM On Borad 128 kBytes 1 MByte

E-mail : a.beddar@cder.dz

ROM On Board 256 kbits (EEPROM) 2Mbits (Flash

PROM)

Introduction Figure 3. Carte de développement

ADC (12 bit) 16(2 S & H) 5 (External)

XILINX SPARTAN 3E. General Purpose 56 173

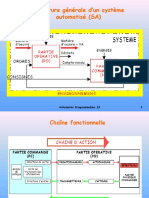

Les convertisseurs de puissance utilisés dans les systèmes I/O Software Code Composer (li- ISE Design Suite

d’énergies renouvelables permettent de transformer l’énergie Type des FPGA mited) (Free)

électrique d’une forme à une autre tout en contrôlant sa di- Les cartes FPGA sont classées en trois familles suivant la tech-

rection et ses caractéristiques. Le contrôle permet de garantir nologie de mémorisation suivant leurs technologies de pro- Price (US$) 325.00 189.00

une gestion efficace de l’échange de l’énergie électrique et de grammation. (2013)

ses caractéristiques (facteur de puissance, forme d’onde des Technologie de programmation par RAM : Les connexions

tensions et courants, taux de distorsion harmonique TDH...), sont des ensembles de transistors commandés, cette techno-

la fiabilité de fonctionnement (tolérance aux défauts et conti- logie permet une reconfiguration rapide des FPGA (Les fabri- Conclusion

nuité de service) et la précision du contrôle. cants sont XILINX et ALTERA). Les DSP et les FPGA peuvent exécuter des stratégies de

Technologie de programmation par EEPROM ou FLASH : Cette contrôle pour commander des convertisseurs de puissance.

technologie garde sa configuration mais un nombre limité de Particulièrement, le nombre réduit des S & Hs dans les DSP

Figure 2. Carte de développement eZdsp

Sun Grid

F2812 TMS320F2812 DSP

configuration avec une configuration plus lente. Les fabricants force la conversion A/D à être séquentielle, ce qui dégrade

DC/AC

DC/DC sont LATTICE et ACTEL. les performances. D’autre part, les FPGA peuvent effectuer

Type des DSPs toutes les conversions A/D en parallèle, réduisant ainsi l’im-

Technologie de programmation par anti-fusible : Les points de

Il est possible de distinguer deux familles des DSP selon la re- connexions sont du type ROM, c’est-à-dire que la modification pact de cette étape sur les performances globales. Ceci, com-

Source PV présentation des nombres qu’ils peuvent manipuler. du point est inversible. Le fabricant est ACTEL. biné à son haut degré de parallélisme et de configurabilité,

Les DSP à virgule flottante : sont plus souples et plus faciles permet aux FPGAs d’obtenir de meilleures performances en

à programmer que les DSP à virgule fixe. Les données mani-

Comparaison entre DSP ET FPGA termes de temps de traitement et d’utilisation des ressources

Partie Contrôle

Comme décrit dans les sections précédentes, les algorithmes matérielles. Cependant, les DSP nécessitent des temps de dé-

DSP/FPGA pulées sont représentés en utilisant une mantisse et un ex-

de contrôle dans les convertisseurs de puissance peuvent être veloppement plus courts, en particulier pour les techniques

posant: n = mantisse x 2 exposant. Un DSP à virgule flottante

implémentés sur différentes plates-formes numériques, les de contrôle avancées. Pour compenser cet inconvénient, le

Figure 1. Configuration d’un système d’énergie comme le TMS320C30 traite des nombres formés avec une

plus souvent basées sur DSP ou FPGAs. code HDL peut faire un usage intensif des bibliothèques de

renouvelable connecté au réseau mantisse de 24 bits et un exposant de 8 bits.

conception internes, exploitant ainsi des conceptions FPGA

Les DSP à virgule fixe : est un peu plus compliqué à program- plus rapides et plus complexes.

Les performances du contrôle dépendent essentiellement du mer qu’un DSP à virgule flottante. TRAITEMENT SEQUENTIEL TRAITEMENT PARALLEL

DSP FPGA

contenu algorithmique implémenté et les capacités de calcul

Les données sont représentées comme étant des entiers clas-

ARCHITECTURE FIGEE ARCHITECTURE

RECONFIGURABLE Références

et d’intégration de la plate-forme numérique (circuits pro-

siques. La représentation de ces nombres fractionnaires s’ap- 1. Hu, Haibing, et al. «Design considerations for DSP-controlled

grammables) utilisée ; pratiquement, on distingue deux types N0 N0 N1 Nn

puie sur la méthode du « complément à deux ». Dans un DSP 400 Hz shunt active power filter in an aircraft power system.»

de circuits programmables :

à virgule fixe comme le TMS320C25, les nombre sont codés IEEE Transactions on Industrial Electronics 59.9 (2011): 3624-

- Les circuits à base des processeurs, PIC (Programmable In- sur 16 bits [1].

terrupt Controler), DSP (Digital Signal Processor).

MULT

MULT MULT MULT 3634

- Les circuits intégrés directement programmables de type Les circuits intégrés programmables de type FPGA 2. Monmasson, Eric, Lahoucine Idkhajine, and Mohamed Wis-

FPGA (Field Programmable Gate Array). Un FPGA (Field-Programmable Gate Array) est un circuit inté-

ADD

sem Naouar. «FPGA-based controllers.» IEEE Industrial Elec-

gré composé d’un grand nombre d’éléments logiques reliés tronics Magazine 5.1 (2011): 14-26.

Les circuits à base des DSP

ADD

entre eux grâce à une matrice de routage programmable. Le 3. Detrey, Jérémie. Arithmétiques réelles sur FPGA : virgule

Un DSP (Digital Signal Processor), est un composant électro- dispositif est programmé en connectant les portes ensemble fixe, virgule flottante et système logarithmique. Diss. École

nique programmable. L’architecture de circuits à base DSP pour former des multiplicateurs, des registres, des addition- normale supérieure (Lyon), 2007.

Figure 4. Schéma comparatif pour le mode

étant déjà fixé par le constructeur, on ne peut que modifier neurs, etc. Cette structure permet aux FPGA d’émuler n’im-

d’exécution d’un DSP et d’un FPGA [3] 4.Texas Instruments, «TMS320F2812 eZdsp Start Kit (DSK)»,

le programme pour adapter le circuit à la commande souhai- porte quel circuit. La programmation de ces circuits s’effectue Available: http://www.ti.com/tool/tmdsezd2812.

tée du convertisseur de puissance. La programmation de ces généralement en langage VHDL (Very High Density Language). Le tableau 1 compare les capacités matérielles, les perfor- 5. Xilinx, Spartan “Spartan-3 FPGA Family Data Sheet” Dec. 4,

circuits s’effectue en langage assembleur où en langage C. Il L’utilisateur « construit » lui-même l’architecture de son mances de deux kits de démarrage basés sur chaque tech- 2009, Available: http://www.xilinx.com/support/documenta-

est bien adapté aux tâches intensives en mathématiques ex- composant en prévoyant les fonctions de commande et de nologie. Les deux cartes sont eZdsp F2812 de Spectrum Digi- tion/data_sheets/ds099.pdf

trêmement complexes, avec un traitement conditionnel [1]. contrôle souhaitées [2]. tal Inc. basé sur Texas Instruments TMS320F2812 DSP [4] et

XCS1000 basé sur Xilinx Spartan-3 FPGA [5].

Vous aimerez peut-être aussi

- CH 05 09Document8 pagesCH 05 09Frisco Elyah AndriantsialoPas encore d'évaluation

- Quanta ZM8 - R1aDocument39 pagesQuanta ZM8 - R1aYetawa GuaviarePas encore d'évaluation

- 3.Dsp Tmsf28335cpuDocument45 pages3.Dsp Tmsf28335cpuMassi Massy MassyPas encore d'évaluation

- U3363 Asus p5gc-mx 1333 QSGDocument38 pagesU3363 Asus p5gc-mx 1333 QSGEduardo Luis ApreaPas encore d'évaluation

- Quanta LI5 - DA0LI5MB6H0Document49 pagesQuanta LI5 - DA0LI5MB6H0Олександр СавчукPas encore d'évaluation

- Compte Rendu TP Archetecture Des Systèmes EmbarquésDocument19 pagesCompte Rendu TP Archetecture Des Systèmes EmbarquésKhawla KholitaPas encore d'évaluation

- Chapitre 3 Mise en Œuvre Des Microcontrôleurs AVR - CopieDocument18 pagesChapitre 3 Mise en Œuvre Des Microcontrôleurs AVR - Copiejulio KetchaPas encore d'évaluation

- DS Version 2 PDFDocument1 pageDS Version 2 PDFbaydiPas encore d'évaluation

- MPC8308RDBSCHDocument12 pagesMPC8308RDBSCHJorgeTaraPas encore d'évaluation

- A8V-VM: Quick Start GuideDocument37 pagesA8V-VM: Quick Start GuideCarmeloPas encore d'évaluation

- Aspire ES1-431 Quanta Z8AD Magellan BA-Z8AD-MB-DDocument32 pagesAspire ES1-431 Quanta Z8AD Magellan BA-Z8AD-MB-Daung kokoPas encore d'évaluation

- Quanta - Y0B - DA0Y0BMB6C0 - 0608 - HP Stream 13-c130nwDocument35 pagesQuanta - Y0B - DA0Y0BMB6C0 - 0608 - HP Stream 13-c130nwJivko IvanovPas encore d'évaluation

- ASRock B75M-DGS r2.0Document48 pagesASRock B75M-DGS r2.0Nguyễn Văn TặngPas encore d'évaluation

- 1-STM32 GPIO RegDocument59 pages1-STM32 GPIO RegSoumri IchrakPas encore d'évaluation

- Quanta U8C DA0U8CMB6B0 Braswell - Uma Rev 1A HP 15Document33 pagesQuanta U8C DA0U8CMB6B0 Braswell - Uma Rev 1A HP 15Rafael Roel Robles BaezPas encore d'évaluation

- Presentation Et Utilisation M5stack Esp32Document7 pagesPresentation Et Utilisation M5stack Esp32Rolando RandriampanomezantsoaPas encore d'évaluation

- Emmc Flyer FRDocument2 pagesEmmc Flyer FRAlbert GaubertPas encore d'évaluation

- Manual Xilinx DS610Document98 pagesManual Xilinx DS610mariannyPas encore d'évaluation

- Model Cours - CopieDocument9 pagesModel Cours - Copieabid alyaniPas encore d'évaluation

- Le Microprocesseur MSP430Document32 pagesLe Microprocesseur MSP430Tresor BrouPas encore d'évaluation

- U3353 m2n-Mx Se Plus QSGDocument38 pagesU3353 m2n-Mx Se Plus QSGjeriasePas encore d'évaluation

- A5198 - P5G41T-M LX - QSGDocument27 pagesA5198 - P5G41T-M LX - QSGCalvin KurniawanPas encore d'évaluation

- Quanta ZHX ZHXS Da0zhxmb6c0 Rev 1a (Acer Ao1-132)Document31 pagesQuanta ZHX ZHXS Da0zhxmb6c0 Rev 1a (Acer Ao1-132)Armand ChaPas encore d'évaluation

- Pic PDFDocument12 pagesPic PDFAntonio Saba100% (1)

- StageObs2020 01Document13 pagesStageObs2020 01ArmelPas encore d'évaluation

- Catalogue Cartes Meres Robotshop05012022Document16 pagesCatalogue Cartes Meres Robotshop05012022lewis kingPas encore d'évaluation

- DA0Y0AMBC60Document31 pagesDA0Y0AMBC60Germán Daniel RotondoPas encore d'évaluation

- DSASW00343875Document18 pagesDSASW00343875Rgt Rogert MikingaPas encore d'évaluation

- FaMillE x86Document21 pagesFaMillE x86bakicPas encore d'évaluation

- U5345 P7H55-ManualeDocument42 pagesU5345 P7H55-ManualelorycolPas encore d'évaluation

- STM32F103x8 STM32F103xB Microcontrôleur 32 Bits Basé Sur Arm® Avec 64 Ou 128 Ko Flash, USB, CAN, 7 Temporisateurs, 2 ADC, 9 Com. InterfacesDocument117 pagesSTM32F103x8 STM32F103xB Microcontrôleur 32 Bits Basé Sur Arm® Avec 64 Ou 128 Ko Flash, USB, CAN, 7 Temporisateurs, 2 ADC, 9 Com. InterfacesAbcp CorpPas encore d'évaluation

- U1721 k8n QSGDocument16 pagesU1721 k8n QSGSergio Diaz PereiraPas encore d'évaluation

- 2021 DSP Chapitre2Document150 pages2021 DSP Chapitre2Yassir LolPas encore d'évaluation

- U4555 - P5KPL-AM IN-ROEM-SI - QSG PDFDocument38 pagesU4555 - P5KPL-AM IN-ROEM-SI - QSG PDFiban7666Pas encore d'évaluation

- Intro Carte 2016Document40 pagesIntro Carte 2016massine.gana17Pas encore d'évaluation

- Quanta Y0BC DAY0BCMB6D0 R1A - 0721 - HP Stream 13 PDFDocument39 pagesQuanta Y0BC DAY0BCMB6D0 R1A - 0721 - HP Stream 13 PDFA.K.M. JAHIDUL IslamPas encore d'évaluation

- Chapitre 1Document4 pagesChapitre 1Fares ChetouhPas encore d'évaluation

- ch2 FPGADocument79 pagesch2 FPGAsaidfatani9Pas encore d'évaluation

- CoursDocument31 pagesCoursahmed fahssiPas encore d'évaluation

- HP Stream NoteBook 11 DA0Y0HMB6F0 Quanta Y0H Schematic DiagramDocument38 pagesHP Stream NoteBook 11 DA0Y0HMB6F0 Quanta Y0H Schematic DiagramЮрий ПокровскийPas encore d'évaluation

- DA0ZHKMB6C0 REV C SCHEMATIC Acer Aspire ES1-111 Aspire V3-112PDocument33 pagesDA0ZHKMB6C0 REV C SCHEMATIC Acer Aspire ES1-111 Aspire V3-112Ppian ismailPas encore d'évaluation

- DSP C6000: Architecture & Programmation C/ASMDocument50 pagesDSP C6000: Architecture & Programmation C/ASMMouhcine Zianee100% (3)

- Acer Aspire E3-112 V3-112 E11 Quanta ZHK DA0ZHKMB6C0 REV C Schematic DiagramDocument33 pagesAcer Aspire E3-112 V3-112 E11 Quanta ZHK DA0ZHKMB6C0 REV C Schematic Diagramirkham13Pas encore d'évaluation

- Quanta ZHK R3a 20140630 SchematicsDocument34 pagesQuanta ZHK R3a 20140630 SchematicsRamdas KamblePas encore d'évaluation

- AFPA - Bande passante - Puissance - Fréquence - ChiffrementDocument2 pagesAFPA - Bande passante - Puissance - Fréquence - Chiffrementtbd.frackowiakPas encore d'évaluation

- Cours VHDLDocument51 pagesCours VHDLCherry CandyPas encore d'évaluation

- Chapitre I STM32 Programmation GPIO ParDocument59 pagesChapitre I STM32 Programmation GPIO ParamaniPas encore d'évaluation

- M7996v1.1 - Parte 6Document8 pagesM7996v1.1 - Parte 6lakekosPas encore d'évaluation

- 2265-BD-001 RevP0Document4 pages2265-BD-001 RevP0Salvador Fayssal100% (1)

- ChipsetDocument9 pagesChipsetMouad_Madness_28Pas encore d'évaluation

- TR10 190Document12 pagesTR10 190andymustopaPas encore d'évaluation

- Quanta 0P9 Rev 1A SchematicDocument37 pagesQuanta 0P9 Rev 1A SchematicRafael Roel Robles BaezPas encore d'évaluation

- DR - MemoiresDocument3 pagesDR - Memoiresprof snPas encore d'évaluation

- Liste Des Prix QNAP NOVEMBRE 2023Document19 pagesListe Des Prix QNAP NOVEMBRE 2023ay.kadhiPas encore d'évaluation

- Chapitre 1 PDFDocument6 pagesChapitre 1 PDFHmz MessaoudPas encore d'évaluation

- Seance 1Document63 pagesSeance 1ensam casaPas encore d'évaluation

- Acer ES1-411 Quanta Z8A DA0Z8AMB4E0 RevE3A SchematicDocument34 pagesAcer ES1-411 Quanta Z8A DA0Z8AMB4E0 RevE3A SchematicBlade Bla BlaPas encore d'évaluation

- Architecture MicroprocesseurDocument35 pagesArchitecture MicroprocesseurImane el omariPas encore d'évaluation

- MethodeDocument7 pagesMethodeLeroy Lionel SonfackPas encore d'évaluation

- Ber44 08 10Document3 pagesBer44 08 10Leroy Lionel SonfackPas encore d'évaluation

- Bilan PuissDocument1 pageBilan PuissLeroy Lionel SonfackPas encore d'évaluation

- Questions de Cours Corrigés en Ordonnancement Des Processus (Systèmes D'exploitation 1) - Exercices en Réseaux InformatiquesDocument3 pagesQuestions de Cours Corrigés en Ordonnancement Des Processus (Systèmes D'exploitation 1) - Exercices en Réseaux InformatiquesLeroy Lionel SonfackPas encore d'évaluation

- CC - Anal - Num - ISR - 2024Document2 pagesCC - Anal - Num - ISR - 2024Leroy Lionel SonfackPas encore d'évaluation

- 2 HistogrammeDocument35 pages2 HistogrammeLeroy Lionel SonfackPas encore d'évaluation

- Bilan de Puissance-1Document2 pagesBilan de Puissance-1Leroy Lionel SonfackPas encore d'évaluation

- Fiche TD Reseaux 2019Document23 pagesFiche TD Reseaux 2019Leroy Lionel SonfackPas encore d'évaluation

- TD de Traitement Du Signal TD N 4 Signaux AléatoiresDocument11 pagesTD de Traitement Du Signal TD N 4 Signaux AléatoiresLeroy Lionel SonfackPas encore d'évaluation

- 2017 Exo2 SourceslumineusesDocument4 pages2017 Exo2 SourceslumineusesLeroy Lionel SonfackPas encore d'évaluation

- 3 Filtrage1Document25 pages3 Filtrage1Leroy Lionel SonfackPas encore d'évaluation

- 4 Filtrage2Document25 pages4 Filtrage2Leroy Lionel SonfackPas encore d'évaluation

- Cours Commande CH 1Document5 pagesCours Commande CH 1Leroy Lionel SonfackPas encore d'évaluation

- Cours Commande CH 2Document4 pagesCours Commande CH 2Leroy Lionel SonfackPas encore d'évaluation

- BTS 2022 - Informatique Industrielle Et AutomatismeDocument7 pagesBTS 2022 - Informatique Industrielle Et AutomatismeLeroy Lionel SonfackPas encore d'évaluation

- BTS 2021 - ElectrotechniqueDocument17 pagesBTS 2021 - ElectrotechniqueLeroy Lionel SonfackPas encore d'évaluation

- BTS 2021 - Informatique Industrielle Et AutomatismeDocument8 pagesBTS 2021 - Informatique Industrielle Et AutomatismeLeroy Lionel SonfackPas encore d'évaluation

- Chapitre 2 PDFDocument24 pagesChapitre 2 PDFHadjerBenzelmatPas encore d'évaluation

- 1 - TD1 - Decoupe de ProfilesDocument3 pages1 - TD1 - Decoupe de ProfilesLeroy Lionel SonfackPas encore d'évaluation

- Les API - DecryptedDocument67 pagesLes API - DecryptedLeroy Lionel SonfackPas encore d'évaluation

- Guidedepriseenmainde Proces SimDocument284 pagesGuidedepriseenmainde Proces SimLeroy Lionel SonfackPas encore d'évaluation

- VIB Booklet F PDFDocument36 pagesVIB Booklet F PDFMustafa MoussaouiPas encore d'évaluation

- Papier PDFDocument23 pagesPapier PDF147896azPas encore d'évaluation

- Maintenance Preventive Des Ven - Hafid BOUSRHIRI - 4238Document89 pagesMaintenance Preventive Des Ven - Hafid BOUSRHIRI - 4238Leroy Lionel SonfackPas encore d'évaluation

- Notion Élémentaire de TopographieDocument18 pagesNotion Élémentaire de TopographieFatima BouchfarPas encore d'évaluation

- Notion Élémentaire de TopographieDocument18 pagesNotion Élémentaire de TopographieFatima BouchfarPas encore d'évaluation

- TP TopographieDocument30 pagesTP TopographieNizar Axel Braham100% (2)

- Sans Titre 2Document6 pagesSans Titre 2Leroy Lionel SonfackPas encore d'évaluation

- Electroméc ElectromécaniqueDocument6 pagesElectroméc ElectromécaniqueDjẹlli MẹđjadiPas encore d'évaluation

- OBS Introduction1Document14 pagesOBS Introduction1Leroy Lionel SonfackPas encore d'évaluation

- Loucos Lisboa FlautaDocument1 pageLoucos Lisboa FlautaPedro MartinsPas encore d'évaluation

- Relatifs Simples Et Pronoms Compléments RévisionsDocument5 pagesRelatifs Simples Et Pronoms Compléments RévisionsAgatha Bez FontanaPas encore d'évaluation

- Le Conditionnel ExercicesDocument2 pagesLe Conditionnel ExercicesFAYE RokhayaPas encore d'évaluation

- Chapitre 21 Fpga+VhdlDocument99 pagesChapitre 21 Fpga+VhdlnourPas encore d'évaluation

- Signaux Et SystemessDocument124 pagesSignaux Et SystemessAriston DecorPas encore d'évaluation

- Chiffrement Par Transposition Ou Permutation Master SCDocument2 pagesChiffrement Par Transposition Ou Permutation Master SCيوسف مرزوق100% (1)

- TP2 Dev Web MidounDocument28 pagesTP2 Dev Web MidounKenza SanaaPas encore d'évaluation

- Dévoilement Des Mensonges de Karim ZenticiDocument14 pagesDévoilement Des Mensonges de Karim ZenticiAqidatoulMouwahidine33% (3)

- Les Pays Et Les Nationalites Exercice Grammatical Feuille Dexercices 43031Document2 pagesLes Pays Et Les Nationalites Exercice Grammatical Feuille Dexercices 43031fanny de los angeles martinez calero0% (1)

- Méthode de FeynamDocument1 pageMéthode de FeynamPatrick KituluPas encore d'évaluation

- Olympiade ORTHOGRAPHE Fin CE2Document1 pageOlympiade ORTHOGRAPHE Fin CE2Ella SiehiPas encore d'évaluation

- Cours Sig AllaouiDocument23 pagesCours Sig Allaouimy ingrPas encore d'évaluation

- JLH A Exercices Resolus Chapitres 1 10Document21 pagesJLH A Exercices Resolus Chapitres 1 10Abdelghani AninichPas encore d'évaluation

- Anthologie FrançaisDocument18 pagesAnthologie Françaisenzolouis70Pas encore d'évaluation

- Cosquin, Emmanuel: Contes populaires de Lorraine : Comparés avec les contes des autres provinces de France et des pays étrangers, et précédés d'un essai sur l'origine et la propagation des contes populaires européens.Document746 pagesCosquin, Emmanuel: Contes populaires de Lorraine : Comparés avec les contes des autres provinces de France et des pays étrangers, et précédés d'un essai sur l'origine et la propagation des contes populaires européens.samecz100% (1)

- Travail de Recherche Les Lumières Séance N°2 Et Séance N°3 Olympe de Gouges 2022-2023Document5 pagesTravail de Recherche Les Lumières Séance N°2 Et Séance N°3 Olympe de Gouges 2022-2023Lalie dmgPas encore d'évaluation

- 3e Me Progre S Et Re Ves Scientifiques Brevet Blanc Partie2Document3 pages3e Me Progre S Et Re Ves Scientifiques Brevet Blanc Partie2moumouPas encore d'évaluation

- Z-Library - WikipédiaDocument4 pagesZ-Library - WikipédiaruchelPas encore d'évaluation

- Utiliser Le Mode MSDocument7 pagesUtiliser Le Mode MSsaad1807Pas encore d'évaluation

- DAGRON, Gilbert, Naissance D - Une CapitaleDocument36 pagesDAGRON, Gilbert, Naissance D - Une CapitaleBurlan IonPas encore d'évaluation

- 2012 Rachik Hassan, Anthropologie Des Plus ProchesDocument151 pages2012 Rachik Hassan, Anthropologie Des Plus ProchesSammouni MohamedPas encore d'évaluation

- ExtraitDocument8 pagesExtraitWiki ThiagoPas encore d'évaluation

- Memo Pratique de L'orthographeDocument62 pagesMemo Pratique de L'orthographemechkad100% (4)

- Cours 01 La Classe de LangueDocument5 pagesCours 01 La Classe de LangueZinaHadiaPas encore d'évaluation

- Demonologie Amorth SatanDocument32 pagesDemonologie Amorth SatanFrançois MendyPas encore d'évaluation

- Allocation de Mémoire en Java: Une Approche Simplifiée Pour La Gestion Des RessourcesDocument3 pagesAllocation de Mémoire en Java: Une Approche Simplifiée Pour La Gestion Des Ressourcesscg.fbarguiPas encore d'évaluation

- Exercices AlgoDocument15 pagesExercices AlgoMelchisedek MeignanPas encore d'évaluation

- Les 10 Noms D'Allah Et Leur Utilisation Qui Attirent La Richesse, La Prospérité eDocument4 pagesLes 10 Noms D'Allah Et Leur Utilisation Qui Attirent La Richesse, La Prospérité eIdrissa MeitePas encore d'évaluation

- Cartes - Jeu Circuit Des MotsDocument16 pagesCartes - Jeu Circuit Des Motsfleur2609Pas encore d'évaluation

- Mulan - Reflection For Solo Piano PDFDocument3 pagesMulan - Reflection For Solo Piano PDFSean ChoPas encore d'évaluation