Académique Documents

Professionnel Documents

Culture Documents

Corrige TD 1 PDF

Transféré par

anasTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Corrige TD 1 PDF

Transféré par

anasDroits d'auteur :

Formats disponibles

Etablissement : ISET-Charguia Département : Technologies de l’Informatique

Matière : Architecture des ordinateurs Année Universitaire : 2012- 2013 (Semestre2)

Corrigé TD n° 1 : Les mémoires

Exercice 1 :

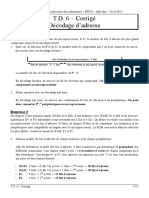

Soit la mémoire représentée par le schéma suivant :

1) La mémoire comporte 11 broches d’adresses :

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10

0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1

Un bit a 2 états 0 ou 1. On peut distinguer 211 adresses. On peut donc adresser 211= 2048

mots mémoire.

2) La taille du mot mémoire correspond au nombre de fils de données, ici 8 fils. Il s’agit de

mots de 8 bits.

3) Capacité de cette mémoire :

On désigne par NbMM : Nombre de mots mémoire

TMM : Taille du mot mémoire

NbMM * TMM = 211 * 23 = 214 bits = 16 Kbits = 2 Ko

4) De quel type de mémoire s’agit-il ? Justifiez.

La présence des broches d’adresse indique que c’est une mémoire à accès directe.

La broche WE indique qu’il est possible d’écrire en mémoire.

Il s’agit donc d’une RAM

Exercice 2 :

Taille de la MC TMC = 64Kbytes. Taille du bus de données TBD = 8 bits.

1) Taille d’un mot mémoire :

TMM = TBD = 8 bits

2) Nombre de mots adressables

NbM = TMC / TMM = (26*210*23) / 23 = 216 mots

3) Ta taille minimale d’un bus d’adresses

Corrigé TD 1 : Les mémoires 1

NbM <= 2TBA or NbM = 216 TBA minimal = 16 bits.

4) Plus grand nombre décimal pouvant être sauvegardé dans un mot mémoire

Un mot mémoire a une taille de 8 bits le plus grand nombre pouvant être sauvegardé est

(11111111)2 = 255

Exercice 3 :

Soit une mémoire ayant les caractéristiques suivantes :

- Le plus grand nombre hexadécimal pouvant être placé dans un mot mémoire est « FFFF »

- La capacité mémoire est de 256 Méga bits

1) Nombre d’entrées de données de cette mémoire

Le plus grand nombre hexadécimal pouvant être placé est FFFF = (1111 1111 1111 1111)2

écrit sur 16 bits, donc, cette mémoire possède 16 entrées.

2) Nombre de bits réservés à l’adressage

NbMM = taille mémoire / taille mot mémoire = (28 *220)/24 = 224.

NbM <= 2bits adressage = 224 24 bits d’adressage

Adresse du dernier mot mémoire : 224 -1 ou (FFFFFF)16

3) La mémoire est extensible jusqu’à 1 Giga bits.

a. Nombre total des mots mémoire après l’extension de cette dernière.

NbMM = Taille mémoire après extension / taille mot mémoire

= 230 / 24 = 226

b. Nombre de bits réservés à l’adressage (après extension)

NbM <= 2bits adressage = 226 26 bits d’adressage

c. Plage d’adresses de cette mémoire après extension :

Plage d’adresses de toute la mémoire : 0 226 -1 : 0 3FFFFFF

Plage d’adresses de la mémoire ajoutée : 224 226 -1: (1000000)16 (3FFFFFF)16

Exercice 4 :

Un microprocesseur a un bus d’adresse de 20 bits et un bus de données de 8 bits.

(00000) 16

ROM

(03FFF)16

(0A000)16

DRAM

(0BFFF)16

Corrigé TD 1 : Les mémoires 2

1) Espace adressable du processeur.

20 bits d’adresse 220 adresses possibles espace adressable : 220 mots

La figure suivante illustre la mémoire d’un système formée par une ROM et une DRAM.

La ROM est située entre les adresses 0x00000 et 0x03FFF

La DRAM est située entre les adresses 0xA0000 et 0x0BFFF.

2) Nombre de bits permettant d’adresser la ROM :

Plage d’adresses : 0x00000 à 0x03FFF (03FFF)16 – (00000)16 = (3FFF)16

= (11 1111 1111 1111)2

= 214 -1

14 bits permettent d’adresser la mémoire.

3) Capacité de la ROM

Comme les adresses des mots mémoire de la ROM varient de 0 à 214 -1, la ROM comprend

214 mots mémoire

Capacité ROM = Nombre de mots mémoire * taille mot mémoire

= 214 * 8 = 217 bits = 128 Kbits = 16 Ko.

4) Quelle est la capacité de la RAM

Nombre de mots mémoire de la RAM :

(0BFFF)16 – (0A000)16 +1 =(1FFF)16 +1 = (1 1111 1111 1111)2 +1 = 213

Taille RAM = Nombre mots mémoire * taille mot mémoire

= 213 * 8 = 216 bits = 64 Kbits= 8 Ko

5) Le cycle mémoire de la DRAM est de 320 ns. Débit de cette DRAM.

Débit = Taille mot mémoire / cycle mémoire = 8/ (320* 10-9) = 25 *106 bit /s

= 25 MégaBits /s

Corrigé TD 1 : Les mémoires 3

Vous aimerez peut-être aussi

- Corrigé Type - TD Gestion de La Mémoire 1 PDFDocument5 pagesCorrigé Type - TD Gestion de La Mémoire 1 PDFKAOUTHER HABIB40% (5)

- Mémentos LMD. Théorie Des Organisations by Sophie Landrieux-KartochianDocument162 pagesMémentos LMD. Théorie Des Organisations by Sophie Landrieux-KartochianSarah B0% (1)

- Solution Examen LAT315 2017Document3 pagesSolution Examen LAT315 2017Babi Ben80% (5)

- Corrigé Devoir N°1Document3 pagesCorrigé Devoir N°1Colmain Nassiri100% (1)

- TD - N°2 - EN - Systèmes À MicroprocesseurDocument7 pagesTD - N°2 - EN - Systèmes À MicroprocesseurTimble Puteur100% (2)

- Jeu D'instructions Du 8086Document75 pagesJeu D'instructions Du 8086Aya Ab100% (1)

- Chapitre3 Programmation en Assembleur 8086 PDFDocument100 pagesChapitre3 Programmation en Assembleur 8086 PDFReda Tadjeddine100% (6)

- TD Microprocesseur 8085Document1 pageTD Microprocesseur 8085nourelhouda71100% (3)

- TD6 Correction PDFDocument4 pagesTD6 Correction PDFMed ArefPas encore d'évaluation

- Corr SN Exam Algo2 SMI3 1516Document4 pagesCorr SN Exam Algo2 SMI3 1516anas0% (1)

- Anatomie Clinique, (WWW - LivreBooks.Eu) PDFDocument378 pagesAnatomie Clinique, (WWW - LivreBooks.Eu) PDFBenAbdallah Hédi86% (7)

- TD 2Document7 pagesTD 2paroles dela6T100% (3)

- TD1 Mémoires 2021Document3 pagesTD1 Mémoires 2021Younesse El100% (2)

- TD Les MémoireDocument4 pagesTD Les Mémoirefers100% (5)

- TD 05 CorrigeeeDocument6 pagesTD 05 CorrigeeeNadhir Mehellou100% (2)

- TD 05 CorrigeDocument6 pagesTD 05 CorrigeAnonymous Wpl47Bwu4Pas encore d'évaluation

- TD3 Mémoire CorrDocument37 pagesTD3 Mémoire CorrNadia Ben NjimaPas encore d'évaluation

- TD CH 3 Architecture Des Ordinateurs 2Document1 pageTD CH 3 Architecture Des Ordinateurs 2Pape Moussa DiopPas encore d'évaluation

- TD 1 Les Mémoires: 1. Partie ThéoriqueDocument2 pagesTD 1 Les Mémoires: 1. Partie ThéoriqueAla DorbozPas encore d'évaluation

- TD4Document1 pageTD4Mounira Tarhouni100% (1)

- TD#3Document2 pagesTD#3Marouane TaibiniPas encore d'évaluation

- Corrigé TD 154Document3 pagesCorrigé TD 154MBADJOUN Daniel100% (1)

- Adressage MemoireDocument10 pagesAdressage MemoireLibre HamataPas encore d'évaluation

- Solution Fiche de TD4 P2 AO USTO 2022-2023 BEKDocument3 pagesSolution Fiche de TD4 P2 AO USTO 2022-2023 BEKKandjeré djida silace SilacePas encore d'évaluation

- TD°2: Mémoiré: Exercice 1Document2 pagesTD°2: Mémoiré: Exercice 1Mouna Ben Mohamed100% (5)

- TD2 CorrigeDocument3 pagesTD2 CorrigeMouna Ben Mohamed100% (1)

- TD 06 CorrigeDocument12 pagesTD 06 CorrigeOmar KhayyamPas encore d'évaluation

- TD1 CorrectionDocument4 pagesTD1 CorrectionMouna Ben Mohamed78% (9)

- Corrigé Série de TD N° 3Document5 pagesCorrigé Série de TD N° 3Alaa MessaoudPas encore d'évaluation

- TD N 2Document4 pagesTD N 2Cesar Malki100% (1)

- C - Memoire Corrigés - CopieDocument5 pagesC - Memoire Corrigés - CopieBrady C'est DieuPas encore d'évaluation

- TD2 MemoireDocument2 pagesTD2 MemoireMouna Ben MohamedPas encore d'évaluation

- CorrigéExamen 2020-2021Document3 pagesCorrigéExamen 2020-2021Moujahed GassoumiPas encore d'évaluation

- TD - N°2 - EN - Systèmes À Microprocesseur PDFDocument7 pagesTD - N°2 - EN - Systèmes À Microprocesseur PDFTimble Puteur100% (1)

- Exercices de RivisionDocument10 pagesExercices de RivisionOnsPas encore d'évaluation

- Corrigé Du TD1Document3 pagesCorrigé Du TD1youssef BohaPas encore d'évaluation

- Examen Final ASO CorrigeDocument3 pagesExamen Final ASO CorrigeHamdi Ata100% (2)

- 1-Modes D'adressage: S ° J ' P I 8086Document4 pages1-Modes D'adressage: S ° J ' P I 8086Sara Benseba67% (3)

- TD2 CorrigeDocument3 pagesTD2 CorrigeAbderrahmane SmaaliPas encore d'évaluation

- Correction TD N°3 CN RegistresDocument4 pagesCorrection TD N°3 CN RegistresKhalil Frikha100% (1)

- Exam 2017Document2 pagesExam 2017Mohamed Hmamouch100% (2)

- Le Microprocesseur 8086Document31 pagesLe Microprocesseur 8086Imed Abdesslem100% (1)

- Série AssembleurDocument3 pagesSérie AssembleurSoufiane Aggour100% (1)

- Microprocesseur-8086 Exercices ResolusDocument8 pagesMicroprocesseur-8086 Exercices Resolusyounes ghenam100% (4)

- Les Mémoires PDFDocument11 pagesLes Mémoires PDFBazizi Wardia50% (2)

- TD1 - Circuit ProgrammablebisDocument4 pagesTD1 - Circuit ProgrammablebisMouhcine Zianee100% (2)

- TP 1 - Programmation Assembleur Avec EMU8086Document3 pagesTP 1 - Programmation Assembleur Avec EMU8086Mounir Kh100% (6)

- Exercices Corrigés Assembleur8086Document2 pagesExercices Corrigés Assembleur8086Anonyme100% (3)

- Série 3Document8 pagesSérie 3Blidi AymenPas encore d'évaluation

- TD Architecture Des Ordinateurs PDFDocument17 pagesTD Architecture Des Ordinateurs PDFAhmedBoukadPas encore d'évaluation

- Série de TD N° 3: Nommez Les Composants D'ordinateur SuivantsDocument4 pagesSérie de TD N° 3: Nommez Les Composants D'ordinateur SuivantsAlaa MessaoudPas encore d'évaluation

- Les Mémoires CachesDocument46 pagesLes Mémoires Cacheshi123Pas encore d'évaluation

- Guide Moto6809Document23 pagesGuide Moto6809fatima zahra benmeriemePas encore d'évaluation

- TD-Fragmentation IP Reponses AttenduesDocument2 pagesTD-Fragmentation IP Reponses AttenduesAyman BahloulPas encore d'évaluation

- Exercices Assembleur M1 ELT ER Serie 2 Avec CorrigéDocument5 pagesExercices Assembleur M1 ELT ER Serie 2 Avec CorrigéAmir Na DzPas encore d'évaluation

- Gestion de La Memoire CorrectionDocument3 pagesGestion de La Memoire CorrectionOthmane Serraj100% (2)

- Architecture Du Microprocesseur 6809 de MotorolaDocument14 pagesArchitecture Du Microprocesseur 6809 de MotorolaPhylipe Rodrigez100% (1)

- TD 4 SolutionDocument3 pagesTD 4 SolutionEttaoufik AbdelazizPas encore d'évaluation

- MemoireDocument14 pagesMemoireSarra BounenniPas encore d'évaluation

- Fiche de TD4 AO USTO 2022 2023 BEKKOUCHEDocument8 pagesFiche de TD4 AO USTO 2022 2023 BEKKOUCHEsup.contactPas encore d'évaluation

- TD 2 Mémoires-1Document3 pagesTD 2 Mémoires-1القرآن الكريمPas encore d'évaluation

- TD ArchiDocument2 pagesTD Archinznnznz sghshPas encore d'évaluation

- TD1 Mémoires 2022Document3 pagesTD1 Mémoires 2022Soufiane AbdelouahabPas encore d'évaluation

- Progc 2Document329 pagesProgc 2Abdallah AitouakrimPas encore d'évaluation

- Archi td9Document2 pagesArchi td9Abdallah GrimaPas encore d'évaluation

- Chap 4-Allocation Dynamique PDFDocument11 pagesChap 4-Allocation Dynamique PDFanasPas encore d'évaluation

- Chap 3-Les PointeursDocument15 pagesChap 3-Les PointeursblaiidPas encore d'évaluation

- Cours4 LestableauxetlespilesDocument11 pagesCours4 LestableauxetlespilesanasPas encore d'évaluation

- Chap 1-Language C, Concepts de BaseDocument34 pagesChap 1-Language C, Concepts de BaseblaiidPas encore d'évaluation

- Chap 2 - Les Tableaux PDFDocument19 pagesChap 2 - Les Tableaux PDFanasPas encore d'évaluation

- Archi Memento MIPS-nupDocument3 pagesArchi Memento MIPS-nupJo JoPas encore d'évaluation

- Exam Algo 02 SMI3 1617Document2 pagesExam Algo 02 SMI3 1617anasPas encore d'évaluation

- Exam Algo 02 SR SMI3 1617Document2 pagesExam Algo 02 SR SMI3 1617anasPas encore d'évaluation

- Exam Algo 02 SR SMI3 1718Document2 pagesExam Algo 02 SR SMI3 1718anas100% (1)

- Exam SN Algo2 SMI3 1516Document2 pagesExam SN Algo2 SMI3 1516anasPas encore d'évaluation

- Exam Algo 02 SMI3 SN 1718Document2 pagesExam Algo 02 SMI3 SN 1718anas100% (1)

- Exam SR RO SMI5 1718Document1 pageExam SR RO SMI5 1718anas100% (1)

- ExamenSN2015 16Document2 pagesExamenSN2015 16anasPas encore d'évaluation

- Excorr SN RO SMI5 1617Document5 pagesExcorr SN RO SMI5 1617anasPas encore d'évaluation

- Exam SN Algo2 SMI3 1415Document2 pagesExam SN Algo2 SMI3 1415anasPas encore d'évaluation

- Corr Exam SR Algo2 SMI3 1415Document4 pagesCorr Exam SR Algo2 SMI3 1415anasPas encore d'évaluation

- Session de RattrapageDocument2 pagesSession de Rattrapageanas100% (1)

- FichierDocument4 pagesFichieranasPas encore d'évaluation

- Exam SR RO SMI5 1617Document2 pagesExam SR RO SMI5 1617anasPas encore d'évaluation

- Exercices MarcosDocument5 pagesExercices MarcosanasPas encore d'évaluation

- Cours4 LestableauxetlespilesDocument11 pagesCours4 LestableauxetlespilesanasPas encore d'évaluation

- Progc 2Document329 pagesProgc 2Abdallah AitouakrimPas encore d'évaluation

- Correction tp3 PDFDocument7 pagesCorrection tp3 PDFanasPas encore d'évaluation

- Séries - BD - TP - 2019 - 2020Document11 pagesSéries - BD - TP - 2019 - 2020anas50% (2)

- Chap 3-Les PointeursDocument15 pagesChap 3-Les PointeursblaiidPas encore d'évaluation

- RemarqueDocument1 pageRemarqueanas100% (1)

- BiologieDocument6 pagesBiologieSenatPas encore d'évaluation

- TP 2 - MISE - ELT - Ind - M1Document2 pagesTP 2 - MISE - ELT - Ind - M1Bousmaha YoucefPas encore d'évaluation

- Mini Projet de RéducteurDocument14 pagesMini Projet de RéducteurWissem OthmaniPas encore d'évaluation

- Conception Des Systemes Dinformation LaDocument34 pagesConception Des Systemes Dinformation Laznga zengaPas encore d'évaluation

- Les Trois Piliers Du Management 07-19Document20 pagesLes Trois Piliers Du Management 07-19alleyPas encore d'évaluation

- ch1 LogiqueDocument19 pagesch1 LogiquePierre-Yves BischoffPas encore d'évaluation

- Cours Espace BacDocument5 pagesCours Espace BacMarouaneHaddadPas encore d'évaluation

- Rads 270617Document157 pagesRads 270617yannickantsakePas encore d'évaluation

- Codes CorrecteursDocument12 pagesCodes CorrecteursArounan DembelePas encore d'évaluation

- Fichier Produit 1027Document10 pagesFichier Produit 1027Salomon JosephPas encore d'évaluation

- Normes de Dessin TechniqueDocument22 pagesNormes de Dessin TechniqueChaker ChaoualPas encore d'évaluation

- TD2 Mecanique Du PointDocument10 pagesTD2 Mecanique Du PointIssam JissamPas encore d'évaluation

- Sujet de Maths Bac C Et E 2022Document4 pagesSujet de Maths Bac C Et E 2022Scherif SakoPas encore d'évaluation

- Liste Des RessourcesDocument11 pagesListe Des Ressourceseow7iuyfgkPas encore d'évaluation

- Diaepcb2010d10 FRDocument108 pagesDiaepcb2010d10 FRRabia Azami HassaniPas encore d'évaluation

- Candidature NGOYI NGOMA Eberlod AmourDocument3 pagesCandidature NGOYI NGOMA Eberlod AmourAmour NGOYIPas encore d'évaluation

- Chapitre 1Document5 pagesChapitre 1beloufaPas encore d'évaluation

- Atelier Regional Sur La Maitrise de L'eau en Zone ArideDocument15 pagesAtelier Regional Sur La Maitrise de L'eau en Zone ArideOumarPas encore d'évaluation

- TP ÉlectroDocument18 pagesTP ÉlectroBichou HomPas encore d'évaluation

- Loi de WeibullDocument7 pagesLoi de Weibullmee100% (2)

- Comment Faire - Citation Et Référence - TableauDocument3 pagesComment Faire - Citation Et Référence - Tableaubill1pouliotPas encore d'évaluation

- Cadastre Et Securite FonciereDocument71 pagesCadastre Et Securite FonciereDame DerPas encore d'évaluation

- Cellule de Thoma - BIOLTROPDocument2 pagesCellule de Thoma - BIOLTROPRahima Hadjer GouabiPas encore d'évaluation

- La Strategie de Fidelisation El Le CRMDocument78 pagesLa Strategie de Fidelisation El Le CRMSokayna DoumaniPas encore d'évaluation

- Presentation de TekupDocument11 pagesPresentation de TekupSoroPas encore d'évaluation

- TP1 PythonDocument3 pagesTP1 PythonFranck Jordan NOZAKAP FOSSIPas encore d'évaluation

- AOT Autorisation D'occupation Temporaire DefinitionDocument2 pagesAOT Autorisation D'occupation Temporaire DefinitionlecouveyPas encore d'évaluation

- Testing Sartorius (Photo)Document2 pagesTesting Sartorius (Photo)choplinPas encore d'évaluation