Académique Documents

Professionnel Documents

Culture Documents

DT DC2 3ST 23 24

Transféré par

Badreddine KraiemTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

DT DC2 3ST 23 24

Transféré par

Badreddine KraiemDroits d'auteur :

Formats disponibles

Devoir de contrô le N°2

Lycée MENZEL JEMIL Section : Sciences Techniques

Épreuve : électricité

Date le 16/02/2024

Durée : 2h Classe : 3ST - Coefficient : 4

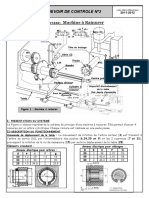

CELLULE DE PERCAGE ET DE TARAUDAGE

I – DESCRIPTION : La cellule de perçage et de taraudage est constituée d’un tapis roulant 1, possédant

sur un pas régulier, des supports pour le maintien de deux types de pièces (pièces hautes et pièces basses).

Le tapis 1 se déplace simultanément devant les trois postes qui sont dans l’ordre :

Poste 1 : Perçage des deux types de pièces.

Poste 2 : Taraudage des deux types de pièces. Détecteur d2

Poste 3 : Triage et éjection de la pièce basse sur le tapis 2.

Détecteur d1

P

P1 P4

3

P2

II – FONCTIONNEMENT DU SYSTEME : L’action sur l’interrupteur Dcy actionne le moteur M1

pour faire avancer le tapis 1 d’un pas (amener des pièces). La présence des pièces devant les postes

d’usinage déclenche simultanément les opérations suivantes :

Perçage : * rotation de M4 et descente de l’unité de perçage par C1.

* dégagement de l’unité tout en maintenant la rotation de M4.

Taraudage : * rotation (sens avant) et descente de l’unité par M3.

Dossier Technique SYSTEME : CELLULE DE PERCAGE ET DE TARAUDADAGE Page 1

* dégagement de l’unité par inversion de sens de rotation de M3.

Triage : * les pièces hautes sont évacuées par gravité vers la rampe (P2 et P3 sont

actionnés).

* les pièces basses sont éjectées par le vérin C2 vers le tapis 2 entraîné par le moteur

M2 (P2 actionné et P3 non actionné).

Le tapis T2 et le rampe d’évacuation orientent les caisses vers leurs cartons d’emballages.

Une fois que les trois opérations sont terminées, le système se trouve dans un état d’arrêt

(repos). Le fonctionnement reprend automatiquement, tant que Dcy reste actionné.

REMARQUE : Pour simplifier l’étude, ne pas tenir compte du fonctionnement du tapis 2.

III – IDENTIFICATION DES PREACTIONNEURS ET DES CAPTEURS UTILISE :

Actions Actionneurs Préactionneurs Capteurs

l11

Vérin C1 Distributeur M 1 (5/2)

l10

Percer la Pièce

Moteur électrique

KM4 -

(M4)

l21

Ejecter la Pièce Vérin C2 Distributeur M2 (5/2)

l20

Moteur électrique

Avancer la Pièce KM1 P1, P4

(M1)

Moteur électrique KM31 S1 : position basse

Tarauder la Pièce

(M3) KM32 S2 : position haute

N.B : S1 et S2 non représentés

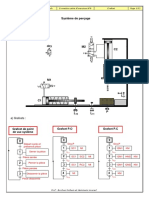

IV- Solution programmé GRAFCET

L21L20L11

dcyP1P2P3P4S1S2L10

0

U1

OSC1/CLKIN RB0/INT21

OSC2/CLKOUT RB122

RB223

2 RB3/PGM24

RA0/AN0 RA1/AN1 RB425

3

RA2/AN2/VREF-/CVREF RB526

4

RA3/AN3/VREF+ RB6/PGC27

5

RA4/T0CKI/C1OUT RB7/PGD28

6

RA5/AN4/SS/C2OUT

7

11

RC0/T1OSO/T1CKI

1 12

MCLR/Vpp/THV RC1/T1OSI/CCP2

13

RC2/CCP1 RC3/SCK/SCL RC4/SDI/SDA

14

RC5/SDO RC6/TX/CK RC7/RX/DT

15

PIC16F876A

16

17

18

?

M12_2 M14_2 M12_1 M14_1KM32 KM31KM4 KM1

Dossier Technique SYSTEME : CELLULE DE PERCAGE ET DE TARAUDADAGE Page 2

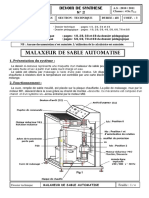

V- Module de comptage des pièces hautes:

Dès qu’une pièce haute est présente au niveau de rampe d’évacuation (détection par d1), le cycle de

remplissage du carton par 9 pièces commence. Une fois le carton est plein une lampe rouge s’allume pour

avertir l’opérateur de préparer un autre carton vide.

d1 (horloge) compteur des pièces hautes(CT1)

Solution programmée de comptage

registre OPTION_REG :

INTEDG TOCS TOSE PSA PS2 PS1 PS0

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Chacun de ces bits à une signification et une fonction :

Bit7: = Pull up Enable bit on PortB.

1=Pull up désactivé sur le PortB. (Pas de résistances) PS2 PS1 PS0 DIV

0=Pull up activé. (Résistances de tirage reliées à +VD D) 0 0 0 2

Bit6: INTEDG = Interrupt Edge select bit. 0 0 1 4

1=Interruption si front montant surRB0/INT

0=Interruption si front descendant surRB0/INT. 0 1 0 8

Bit5: TOCS = Timer TMR0 Clock Source selectbit. 0 1 1 16

1=L’horloge du Timer est l’entrée RA4/Clk

1 0 0 32

0=Le Timer utilise l’horloge interne du PIC.

Bit4 : TOSE =TimerTMR0SourceEdgeselectbit. 1 0 1 64

1=LeTimer s’incrémente à chaque front descendant sur RA4/1 1 0 128

0=LeTimer s’incrémente à chaque front montant surRA Clk. 1 1 1 256

Bit3 : PSA=Prescaler Assignement bit.

1=Le pré-diviseur est affecté au watchdog.

0=Le pré-diviseur est affecté au Timer TMR0.

Bits2, 1 et 0 : PS2PS1PS0 = Prescaler Rate Select bits.

Dossier Technique SYSTEME : CELLULE DE PERCAGE ET DE TARAUDADAGE Page 3

Vous aimerez peut-être aussi

- Exemple Rapport D'activitéDocument19 pagesExemple Rapport D'activitéSalah BoussettaPas encore d'évaluation

- Devoir+synt 3SCTech 2010Document8 pagesDevoir+synt 3SCTech 2010Bouabdellaoui saif ennasr100% (1)

- Poste AutomatiqueDocument3 pagesPoste AutomatiqueAH Med67% (3)

- Systeme de Conditionnement de Comprimes PharmaceutiquesDocument7 pagesSysteme de Conditionnement de Comprimes Pharmaceutiquessaber mecheri100% (2)

- TD Bois PDFDocument2 pagesTD Bois PDFNdiogou Guene100% (1)

- ds1 SC 2020 2021Document8 pagesds1 SC 2020 2021Ahmed NajjarPas encore d'évaluation

- DT DC3 FinaleDocument6 pagesDT DC3 FinaleChaabane BOUALIPas encore d'évaluation

- Unité D'usinageDocument5 pagesUnité D'usinageSsantrino OnirtnassPas encore d'évaluation

- (2019-2020) - DSN°1 - 2ème-Poste de Découpage de Marbre BarraDocument3 pages(2019-2020) - DSN°1 - 2ème-Poste de Découpage de Marbre BarraAdam Bensaid100% (1)

- Exo Choix Detecteur EleveDocument3 pagesExo Choix Detecteur EleveBabacarDiagoPas encore d'évaluation

- dc31 3st 2023 2Document4 pagesdc31 3st 2023 2labossefPas encore d'évaluation

- Unité de Poinçonnage (Corrigé)Document3 pagesUnité de Poinçonnage (Corrigé)mohamedmessahel754Pas encore d'évaluation

- dc2 3tech 2011 2012Document7 pagesdc2 3tech 2011 2012Bouabdellaoui saif ennasrPas encore d'évaluation

- Système Automatique de Découpage - Perçage: TechnologieDocument6 pagesSystème Automatique de Découpage - Perçage: TechnologieChaabane BOUALIPas encore d'évaluation

- Devoir de Contrôle N°2 2009 2010 (Ghanmi Nasr)Document7 pagesDevoir de Contrôle N°2 2009 2010 (Ghanmi Nasr)Khaled AmriPas encore d'évaluation

- Correction Devoir+de+Controle+N2 2AS+ Perceuse+Rotative 2021Document5 pagesCorrection Devoir+de+Controle+N2 2AS+ Perceuse+Rotative 2021aliPas encore d'évaluation

- Devoir de Synthese N°3: Disciplines TechniquesDocument4 pagesDevoir de Synthese N°3: Disciplines TechniquesJUSDOVIC EDJOZOMBIPas encore d'évaluation

- 1830-kazfets-c1-tp12-travail-demandeDocument4 pages1830-kazfets-c1-tp12-travail-demandegirardPas encore d'évaluation

- Upload - Série D'exercices N°8-3tech-Grafcet1 - 2013-2014 CorrectionDocument12 pagesUpload - Série D'exercices N°8-3tech-Grafcet1 - 2013-2014 CorrectionaymenmoatazPas encore d'évaluation

- DEV3_SHEMA BAC F3Document3 pagesDEV3_SHEMA BAC F3Daouda OUEDRAOGOPas encore d'évaluation

- 1 Tronconneuse Automatique Grafcet Organigramme Systeme Minimum CorrigeDocument18 pages1 Tronconneuse Automatique Grafcet Organigramme Systeme Minimum CorrigeQFE100% (2)

- Bts 2019 Elect de Puissance Asservissement Inf IndustDocument5 pagesBts 2019 Elect de Puissance Asservissement Inf IndustOk OkokPas encore d'évaluation

- CORRECTION-Devoir de Synthése N1-1AS-2013Document5 pagesCORRECTION-Devoir de Synthése N1-1AS-2013sghaierfaridPas encore d'évaluation

- Devoir de Synthèse N°2 - Technologie Dossier Technique MALAXEUR DE SABLE - Bac Technique (2010-2011) MR ZAAFOURI mEHREZDocument4 pagesDevoir de Synthèse N°2 - Technologie Dossier Technique MALAXEUR DE SABLE - Bac Technique (2010-2011) MR ZAAFOURI mEHREZsuiton fzPas encore d'évaluation

- Tte 03 Ce 1Document4 pagesTte 03 Ce 1Djerbien Slouma100% (1)

- DCN°3 3ScT 16-17 DTDocument3 pagesDCN°3 3ScT 16-17 DTBouabdellaoui saif ennasr100% (1)

- DC2 2 SC2Document3 pagesDC2 2 SC2Adel KmimechPas encore d'évaluation

- ASE-GP1-T2-2021Document19 pagesASE-GP1-T2-2021Mamadou DiagnePas encore d'évaluation

- Malaxeur de Sable AutomatiseDocument9 pagesMalaxeur de Sable AutomatiseHamada HamadaPas encore d'évaluation

- DS1 - DT - Cellule Flexible D'usinageDocument4 pagesDS1 - DT - Cellule Flexible D'usinageElafif Hamdi0% (1)

- TP ΜContr 21Document2 pagesTP ΜContr 21Taha Chergui MouanePas encore d'évaluation

- S A D T D C: Ysteme Utomatique E RI E AissesDocument6 pagesS A D T D C: Ysteme Utomatique E RI E Aisseslou louPas encore d'évaluation

- TD N°6 Min PDFDocument2 pagesTD N°6 Min PDFSanda OumarouPas encore d'évaluation

- Poste Automatique de Séchage Et D'évacuation: RoyaumeDocument53 pagesPoste Automatique de Séchage Et D'évacuation: RoyaumeAbdelhakimPas encore d'évaluation

- Série PILEDocument6 pagesSérie PILEHamami AymenPas encore d'évaluation

- 7 Le Demarrage Etoile Triangle Eleve PDFDocument3 pages7 Le Demarrage Etoile Triangle Eleve PDFPaul DayPas encore d'évaluation

- L3_ELM_TP_AutomatismeDocument9 pagesL3_ELM_TP_AutomatismegadegbekoueliPas encore d'évaluation

- Devoir Corrigé de Synthèse N°2 - Génie Mécanique Unité de TRI Automatique Des Caisses - 3ème Technique (2013-2014) MR Ben Abdallah Marouan PDFDocument14 pagesDevoir Corrigé de Synthèse N°2 - Génie Mécanique Unité de TRI Automatique Des Caisses - 3ème Technique (2013-2014) MR Ben Abdallah Marouan PDFYosra Flh100% (1)

- Schéma AutoDocument10 pagesSchéma AutoKaneki KenPas encore d'évaluation

- Synthese Variation Vitesse Mas Tri 1Document11 pagesSynthese Variation Vitesse Mas Tri 1yassinePas encore d'évaluation

- Devoir de Contrôle N°1 - Technologie - Poste automatique de cambrage - 1ère AS (2011-2012) Mr Chokri MessaoudDocument4 pagesDevoir de Contrôle N°1 - Technologie - Poste automatique de cambrage - 1ère AS (2011-2012) Mr Chokri Messaoudahmed tounsiPas encore d'évaluation

- evaluation Schéma BAC F3Document3 pagesevaluation Schéma BAC F3Daouda OUEDRAOGOPas encore d'évaluation

- TD2 - Démarrage 2sensDocument5 pagesTD2 - Démarrage 2sensnada mojahidPas encore d'évaluation

- DST de MTSDocument5 pagesDST de MTSMPONGUIPas encore d'évaluation

- Devoir Contrôle 2 3tecDocument4 pagesDevoir Contrôle 2 3tecAhmed GhediraPas encore d'évaluation

- Devoir de Synthese #02: Bouabidi Y. Ben Othman MDocument6 pagesDevoir de Synthese #02: Bouabidi Y. Ben Othman MBouabdellaoui saif ennasrPas encore d'évaluation

- Dossier TechniqueDocument6 pagesDossier Techniqueمحمد بن موسى الخوارزمي0% (1)

- Devoir Corrigé de Synthèse N°2 - Génie Mécanique Banderouleuse - Bac Technique (2013-2014) MR Ben Abdallah MarouanDocument17 pagesDevoir Corrigé de Synthèse N°2 - Génie Mécanique Banderouleuse - Bac Technique (2013-2014) MR Ben Abdallah MarouanKhalil Bkekri100% (2)

- TD Percage de PieceDocument5 pagesTD Percage de Piecevalou cnPas encore d'évaluation

- Encaisseuse de Coffrets D'extincteurs: 1. Présentation Du SystèmeDocument4 pagesEncaisseuse de Coffrets D'extincteurs: 1. Présentation Du SystèmeTaieb BentaherPas encore d'évaluation

- 4 Sc Tech-dt-11-12-Systeme Automatique de MoulageDocument3 pages4 Sc Tech-dt-11-12-Systeme Automatique de MoulageezzinePas encore d'évaluation

- DS1 3ScT 2019-2020Document6 pagesDS1 3ScT 2019-2020Ridha ManaaPas encore d'évaluation

- Schema 4eme Annee 2Document4 pagesSchema 4eme Annee 2BAMALJoseph Firmin100% (5)

- Unité de Remplissage Des Bouteilles en Huile D'olive: Drep XXDocument20 pagesUnité de Remplissage Des Bouteilles en Huile D'olive: Drep XXAhmed ChebchoubPas encore d'évaluation

- Support Sujets GIM S3Document9 pagesSupport Sujets GIM S3Thierry BoulayPas encore d'évaluation

- Manuel Des Plug-In de Commande Des Moteurs Du Robot L6201Document10 pagesManuel Des Plug-In de Commande Des Moteurs Du Robot L6201Sofiane AltairPas encore d'évaluation

- Upload - Série D'exercices N°8-3tech-Grafcet1-2013-2014Document14 pagesUpload - Série D'exercices N°8-3tech-Grafcet1-2013-2014admmehdiPas encore d'évaluation

- tp7 Freinage Machine Asynchrone Injection Courant ContinuDocument4 pagestp7 Freinage Machine Asynchrone Injection Courant ContinuGlodi Maestro MbwamaPas encore d'évaluation

- DC2-2 Info - 2021Document3 pagesDC2-2 Info - 2021Besbes ZiedPas encore d'évaluation

- 8c5lh-Unite Automatique de PDFDocument3 pages8c5lh-Unite Automatique de PDFl mPas encore d'évaluation

- Le syndrome périodique associé à la cryopyrine (CAPS)D'EverandLe syndrome périodique associé à la cryopyrine (CAPS)Pas encore d'évaluation

- Simulation des vibrations mécaniques, 2e édition: par Matlab, Simulink et AnsysD'EverandSimulation des vibrations mécaniques, 2e édition: par Matlab, Simulink et AnsysPas encore d'évaluation

- Les Vis PDFDocument7 pagesLes Vis PDFadilofivePas encore d'évaluation

- Plan PDF Kit Du Jardineur Novice PDFDocument13 pagesPlan PDF Kit Du Jardineur Novice PDFDelassusPas encore d'évaluation

- Qualité, Tenue Mécanique Et Durabilité Du BoisDocument18 pagesQualité, Tenue Mécanique Et Durabilité Du BoisElouakassi OuijdanePas encore d'évaluation

- Spaenaur 14Document1 713 pagesSpaenaur 14Derek KolePas encore d'évaluation

- Bordereaux Des PrixDocument1 pageBordereaux Des Prixsadouk mohamedPas encore d'évaluation

- Vocabulaire TechniqueDocument26 pagesVocabulaire TechniqueMariem beautyPas encore d'évaluation

- Tracteur Tondeuse Husqvarna Yt130 Vue-Eclate-Liste-Des-Pieces 1996-01Document23 pagesTracteur Tondeuse Husqvarna Yt130 Vue-Eclate-Liste-Des-Pieces 1996-01Pascal FRANCESPas encore d'évaluation

- HORNBACH FCH Plafond en BoisDocument2 pagesHORNBACH FCH Plafond en BoisRedouane DahmaniPas encore d'évaluation

- Filetage - Taraudage 1Document5 pagesFiletage - Taraudage 1Aziz KaborePas encore d'évaluation

- Catalogo Sandvick TornoDocument42 pagesCatalogo Sandvick TornoTaty ProañoPas encore d'évaluation

- Fichier Vocabulaire TechniqueDocument26 pagesFichier Vocabulaire Techniquehasnae100% (1)

- ++TD #3 - Usure Des Outils de CoupeDocument2 pages++TD #3 - Usure Des Outils de CoupeRayen AbPas encore d'évaluation

- Rapport Ahmed WannesDocument21 pagesRapport Ahmed WannesWannes AhmedPas encore d'évaluation

- Porte BalaiDocument22 pagesPorte BalaiMohamed MtaallahPas encore d'évaluation

- TD GrafcetDocument6 pagesTD GrafcetJovy Berny100% (1)

- 2016 11 22 AAB Guide EbenisterieDocument23 pages2016 11 22 AAB Guide EbenisteriebhardhamuPas encore d'évaluation

- 02 Charpente Traditionnelle PDFDocument5 pages02 Charpente Traditionnelle PDFlekouf43Pas encore d'évaluation

- Meuler, Poncer, Brosser PDFDocument1 pageMeuler, Poncer, Brosser PDFMamou DeflaouiPas encore d'évaluation

- TP N 3 PercageDocument5 pagesTP N 3 PercagetthPas encore d'évaluation

- Chapitre 5. Les Opérations de Sciage de La 1ere Transformation Du BoisDocument40 pagesChapitre 5. Les Opérations de Sciage de La 1ere Transformation Du BoisreyannadjessiPas encore d'évaluation

- TPFAO2 TournageDocument7 pagesTPFAO2 TournageBoutef El HachemiPas encore d'évaluation

- Fard 3 3aep FR 12Document5 pagesFard 3 3aep FR 12MOULOUD LAGHRIFIPas encore d'évaluation

- (Brico) Bois - Les Assemblages Tenon Et MortaiseDocument4 pages(Brico) Bois - Les Assemblages Tenon Et MortaiselebPas encore d'évaluation

- TechnologieDocument11 pagesTechnologieDayang DayangPas encore d'évaluation

- Bois Paul AndréDocument3 pagesBois Paul AndréTMarlierPas encore d'évaluation

- Menuiserie BoisDocument21 pagesMenuiserie BoisHanane BenGamra50% (2)

- XXXXXXXDocument14 pagesXXXXXXXSofianePas encore d'évaluation