Académique Documents

Professionnel Documents

Culture Documents

Sol Ex3

Transféré par

safiachraf21Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Sol Ex3

Transféré par

safiachraf21Droits d'auteur :

Formats disponibles

Solution:

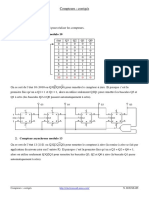

1. Entrées et sorties du circuit CL : (2pts) P0

DL0

OD0

CL OD1

DL1

NP

DL LP P1

FIFO

N N N

P P P

I I I

N N N

F F F Bus de données

O O O

Symbole Signification

LP Lecture prête

DL Demande de Lecture en FIFO

NP Numéro de processeur

Pi Processeur i

DLi Demande de lecture du processeur i

ODi Ouverture du Bus de Données pour le processeur i

2. Table de vérité : (1pt)

N° LP NP DL0 DL1 DL OD0 OD1

0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0

2 0 0 1 0 0 0 0

3 0 0 1 1 0 0 0

4 0 1 0 0 0 0 0

5 0 1 0 1 0 0 0

6 0 1 1 0 0 0 0

7 0 1 1 1 0 0 0

8 1 0 0 0 0 0 0

9 1 0 0 1 0 0 0

10 1 0 1 0 1 1 0

11 1 0 1 1 1 1 0

12 1 1 0 0 0 0 0

13 1 1 0 1 1 0 1

14 1 1 1 0 0 0 0

15 1 1 1 1 1 0 1

3- ROM (1pt)

0

1

2

3

LP 4

NP 5

6

DL0 7

DL1 8

9

10

11

12

13

14

15

DL OD0 OD1

1

Vous aimerez peut-être aussi

- Sol td1.2 Ex3Document2 pagesSol td1.2 Ex3safiachraf21Pas encore d'évaluation

- Tipaza TD2Document1 pageTipaza TD2Guergour WalidPas encore d'évaluation

- TP5 Logique Combinatoirel2eln NS442Document3 pagesTP5 Logique Combinatoirel2eln NS442ボディ ービル ダーPas encore d'évaluation

- Rapport VHDLDocument5 pagesRapport VHDLSofiane AltairPas encore d'évaluation

- Lab 3 - Décodeurs, Afficheurs Et MultiplexeursDocument11 pagesLab 3 - Décodeurs, Afficheurs Et Multiplexeursnoe finaritra RandriambolaPas encore d'évaluation

- TP ApiDocument9 pagesTP Apibenesseddik.abdessalemePas encore d'évaluation

- CircombrevsolDocument9 pagesCircombrevsolrahma kaabi100% (1)

- ALLAM Abdallah °4Document14 pagesALLAM Abdallah °4acabPas encore d'évaluation

- PointDocument24 pagesPointHAM TESTE-webhostPas encore d'évaluation

- TP 2 Fpga M1 ESEDocument4 pagesTP 2 Fpga M1 ESEIlyas KendouciPas encore d'évaluation

- Zatla ADocument12 pagesZatla ARaja Ben CharradaPas encore d'évaluation

- 3 Exercices Corrigés D'electrotechniqueDocument8 pages3 Exercices Corrigés D'electrotechniqueyousra chakPas encore d'évaluation

- Corrigé TD1Document13 pagesCorrigé TD1All AhmeDciaPas encore d'évaluation

- Corrigé TD3Document7 pagesCorrigé TD3All AhmeDciaPas encore d'évaluation

- Imane Chahtan VHDLDocument32 pagesImane Chahtan VHDLImane Ech-chahtanPas encore d'évaluation

- Compte Redu Ilias RAHMOUNI TP1 AutomatismeDocument12 pagesCompte Redu Ilias RAHMOUNI TP1 AutomatismemidoPas encore d'évaluation

- POKDocument3 pagesPOKhrushko.maksymPas encore d'évaluation

- Les Bascules Et Les CompteursDocument2 pagesLes Bascules Et Les CompteurskhayyamPas encore d'évaluation

- Chapitre III PDFDocument14 pagesChapitre III PDFtinhinane hadjouPas encore d'évaluation

- Decodeur 7 SegmentsDocument3 pagesDecodeur 7 Segmentsarnaud.michauxPas encore d'évaluation

- TP2 Can ElnDocument2 pagesTP2 Can ElnkhaledteslaPas encore d'évaluation

- TP3 Dsp-Fpga S2 2021Document4 pagesTP3 Dsp-Fpga S2 2021yousraPas encore d'évaluation

- TP 1 CPL Ex1 Ex2Document5 pagesTP 1 CPL Ex1 Ex2zinebPas encore d'évaluation

- Fiche TD LDDocument2 pagesFiche TD LDasma abdedayemPas encore d'évaluation

- Lecon A2-3 - Circuits CombinatoiresDocument5 pagesLecon A2-3 - Circuits CombinatoiresKadri MongiPas encore d'évaluation

- Rapport VHDL Rémi ADDEDocument19 pagesRapport VHDL Rémi ADDEsorejadPas encore d'évaluation

- Decodeur 7Document1 pageDecodeur 7khaled fawazPas encore d'évaluation

- TP2Codeurs Et DecodeursDocument4 pagesTP2Codeurs Et DecodeursBassmala BaraaPas encore d'évaluation

- Devoir-Circuit-Logique Final 2015 CorigéDocument4 pagesDevoir-Circuit-Logique Final 2015 CorigéabderrahmenPas encore d'évaluation

- TD 5 SolutionDocument5 pagesTD 5 Solutionphysiquesmp33Pas encore d'évaluation

- Activité PratiqueDocument5 pagesActivité PratiqueChang MinPas encore d'évaluation

- Activites Corrigée PDFDocument31 pagesActivites Corrigée PDFKadri MongiPas encore d'évaluation

- C CompteursDocument7 pagesC CompteursyayaPas encore d'évaluation

- Confiabilidad Alfa de Cronbach - KR 20m TecnicasDocument4 pagesConfiabilidad Alfa de Cronbach - KR 20m TecnicasAlindor Quiñones rosalesPas encore d'évaluation

- BinaireDocument4 pagesBinairegael thomPas encore d'évaluation

- TD4 SolutionsDocument7 pagesTD4 SolutionsSafae EL HAIRACHPas encore d'évaluation

- TP JKDocument7 pagesTP JKDouaa MoussaouiPas encore d'évaluation

- TP 1Document4 pagesTP 1Otmane El FaihPas encore d'évaluation

- Matière: TECHNOLOGIE Devoir de Synthèse N°2: Automatique de Levage 1 Partie: Système CombinatoireDocument5 pagesMatière: TECHNOLOGIE Devoir de Synthèse N°2: Automatique de Levage 1 Partie: Système CombinatoireMarouen MekkiPas encore d'évaluation

- Intro1 FPGADocument2 pagesIntro1 FPGAAdnyl OudPas encore d'évaluation

- TP3 1GE CorrectionDocument4 pagesTP3 1GE CorrectionasmaPas encore d'évaluation

- Test Strm+corrDocument10 pagesTest Strm+corrRe Sab RinaPas encore d'évaluation

- Activité PratiqueDocument5 pagesActivité PratiqueChang MinPas encore d'évaluation

- Elnum TD5 Sol PDFDocument5 pagesElnum TD5 Sol PDFbenaouda31Pas encore d'évaluation

- Problèmes de Logique Combinatoire CorrDocument4 pagesProblèmes de Logique Combinatoire CorrAbdalah DaliPas encore d'évaluation

- Geii 1a Logique TP 2Document11 pagesGeii 1a Logique TP 2Thibaud BouzyPas encore d'évaluation

- TD01Document1 pageTD01Înēs KblPas encore d'évaluation

- Devoir de Synthèse N°3 - Technologie Vérin D'un Parabole - 1ère AS (2014-2015) MR TAREK BAZMIDocument6 pagesDevoir de Synthèse N°3 - Technologie Vérin D'un Parabole - 1ère AS (2014-2015) MR TAREK BAZMITarek BenattiguePas encore d'évaluation

- Lab 2 - Logique BooléenneDocument14 pagesLab 2 - Logique Booléennenoe finaritra RandriambolaPas encore d'évaluation

- Correction TDCOMPTEDocument4 pagesCorrection TDCOMPTENejib JallouliPas encore d'évaluation

- ConversionDocument1 pageConversionchrisbierPas encore d'évaluation

- TP Simulation PIC18f8722Document2 pagesTP Simulation PIC18f8722dodoPas encore d'évaluation

- Ch4 Revisions - Logique - SequentielleDocument35 pagesCh4 Revisions - Logique - SequentielleTaramba kossiPas encore d'évaluation

- TD Conv Binaire4bits Vers Double BCDDocument2 pagesTD Conv Binaire4bits Vers Double BCDlouisboudier3Pas encore d'évaluation

- Corre Ction TD1 SuiteDocument5 pagesCorre Ction TD1 SuiteBeyaz ÇiçekPas encore d'évaluation

- Modele Fiche Etat Vehicule Location L UxIBF4Document1 pageModele Fiche Etat Vehicule Location L UxIBF4corporatecarsPas encore d'évaluation

- Rapport 4Document6 pagesRapport 4Ugo TiraboschiPas encore d'évaluation

- Memoir de YohanDocument14 pagesMemoir de Yohanyohan koffiPas encore d'évaluation

- Pca3 PDFDocument18 pagesPca3 PDFfaridassiPas encore d'évaluation

- Ceh Exam 2Document9 pagesCeh Exam 2the best music in the world أجمل موسيىقى في العالمPas encore d'évaluation

- Marché TunisienDocument2 pagesMarché Tunisienabdenacer meratiPas encore d'évaluation

- Document de Cadrage BROUILLONDocument3 pagesDocument de Cadrage BROUILLONRebecca Dipama (Partner)Pas encore d'évaluation

- Revue de ContratDocument1 pageRevue de ContratDominique Fluzin0% (1)

- Partage de Charge Et Ingiénierie de Trafic MPLSDocument227 pagesPartage de Charge Et Ingiénierie de Trafic MPLSjeremiees2015100% (1)

- Compte Rendu C++Document18 pagesCompte Rendu C++essadam96Pas encore d'évaluation

- Microsoft Project 2019Document6 pagesMicrosoft Project 2019İmane Bouziane0% (1)

- Brochure FIBRE Promoteur - 0415 - v2Document5 pagesBrochure FIBRE Promoteur - 0415 - v2Maryam SendiPas encore d'évaluation

- Exercices Vocabulaire PDFDocument2 pagesExercices Vocabulaire PDFGhostnotePas encore d'évaluation

- Memoire DMIDocument121 pagesMemoire DMIabla.zmit24Pas encore d'évaluation

- Calendrier Ine1 Semestre 2 v5Document13 pagesCalendrier Ine1 Semestre 2 v5Abderrahim OuakkiPas encore d'évaluation

- Piratage - Le Site Ivoirien AtooDocument3 pagesPiratage - Le Site Ivoirien AtooArnaud RomaricPas encore d'évaluation

- Veeam Backup 7 Highlights FRDocument2 pagesVeeam Backup 7 Highlights FRYves YoroPas encore d'évaluation

- TP Info GR 1Document11 pagesTP Info GR 1Patrick DenaPas encore d'évaluation

- SticapDocument29 pagesSticapLemjid YesminePas encore d'évaluation

- Reglementation IncendieDocument8 pagesReglementation IncendieFatima EzzahraPas encore d'évaluation

- Finyear 03 Mai 2011Document39 pagesFinyear 03 Mai 2011FinyearPas encore d'évaluation

- Les ComposantsDocument9 pagesLes ComposantsSaad NouiouaPas encore d'évaluation

- HONOR Magic4 Lite Guide de L¡®utilisateur - (Magic UI 4.2 - 01, FR)Document92 pagesHONOR Magic4 Lite Guide de L¡®utilisateur - (Magic UI 4.2 - 01, FR)Djoman Djako Abed-negoPas encore d'évaluation

- EDDEROUASSI 2017 Archivage PDFDocument743 pagesEDDEROUASSI 2017 Archivage PDFali bouazzaPas encore d'évaluation

- Introduction Au Système Information ActualiséDocument53 pagesIntroduction Au Système Information ActualisébgfdPas encore d'évaluation

- Antivol D'oeuvres D'art Par RFIDDocument2 pagesAntivol D'oeuvres D'art Par RFIDbioaccezPas encore d'évaluation

- Livret 3 Reseau Aerien MV Nu V1Document10 pagesLivret 3 Reseau Aerien MV Nu V1Georges TarabayPas encore d'évaluation

- Pilote IsamDocument2 pagesPilote Isamyassin101Pas encore d'évaluation

- Client Projet FlashReport AaaammjjDocument3 pagesClient Projet FlashReport AaaammjjFashionitaPas encore d'évaluation

- Intelligence ÉconomiqueDocument26 pagesIntelligence ÉconomiqueAurelienPas encore d'évaluation

- Memoire MasterDocument78 pagesMemoire MasterSelma MehenniPas encore d'évaluation