Académique Documents

Professionnel Documents

Culture Documents

Mise A Niveau 1

Transféré par

koyabeTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Mise A Niveau 1

Transféré par

koyabeDroits d'auteur :

Formats disponibles

FILIERE : IIA Prépa EPS 1

MISE A NIVEAU 1 : INTERFACE PARALLELE : PIA 6821

Compétences visées : A la fin de ce cours, l’étudiant devra être capable de :

- Décrire la structure du PIA 6821

- Programmer le PIA 6821

I. ARCHITECTURE INTERNE

L’interface parallèle de type PIA 6821 (Peripherical Interface Adapter) fournit un moyen d’interface des appareils

périphériques avec un microprocesseur 680X. Ce circuit interface le MPU avec les périphériques par deux bus de données 8

bits bidirectionnels et quatre lignes de contrôle. La configuration fonctionnelle du PIA est programmée habituellement par le

MPU pendant l’initialisation du système. Chacune des lignes de données vers la périphérie (Port A et B) peut être

programmée pour être utilisée soit en entrée, soit en sortie à partir des registres internes et du bus de données.

REDIGE PAR NKAMNDA SATEU CHRISTIAN NOEL ANNEE ACADEMIQUE 2020-2021 1

FILIERE : IIA Prépa EPS 2

Bus de données (D0 à D7) :

8 lignes bidirectionnelles directement reliées au bus du 6809. Elles assurent l’échange des données entre le

microprocesseur et le PIA. Si elles ne sont pas utilisées, ces lignes sont à l’état haute impédance.

Bus d’adresses :

- CS0, CS1, /CS2 (Chip Select) : Sélectionnent le boîtier PIA (CS0.CS1./CS2 = 1.1.0)

- RS0, RS1 (Register Select) : Sélectionnent les registres internes (4 octets mémoire).

Bus de contrôle :

- E : Signal d’activation des échanges

- /RESET : Initialisation du PIA. Les registres internes sont mis à zéro.

- R/W : Lecture – Ecriture

- IRQA, IRQB : Lignes d’interruptions

Lignes de transfert : PA0 à PA7, PB0 à PB7 : Ces 16 broches (2 x 8) permettent de transmettre ou recevoir un mot de 8

bits. Suivant la programmation du DDRA/DDRB, elles seront utilisées en entrée ou en sortie.

II. FONCTIONNEMENT

Le PIA contient six registres (deux fois trois) permettant de diriger son fonctionnement :

Le registre ORA (ou ORB) : mémorise les données en sortie lors d'une écriture. C'est à cette même adresse qu'il est

possible de lire les données présentées en entrée.

Le registre DDRA (ou DDRB) est celui qui contient le mot fixant le sens de transfert (entrée ou sortie) pour chacune des

lignes de données. Un état « 1 », définit une broche en sortie et un état « 0 » la définit en entrée.

Le registre CRA (ou CRB) contrôle et de définit les différentes fonctions du PIA. Celles-ci sont résumées figure ci-dessous.

Ce dernier registre a de plus un rôle particulier car il contient un bit (le troisième) permettant de sélectionner I'un ou I'autre

des deux registres précédents (ORA ou DDRA). En effet, ceux-ci sont adressés par le microprocesseur à I'aide du même

mot binaire (« 00 » aux broches RS0 et RS1). Par conséquent, un deuxième adressage est nécessaire : il est obtenu par

l'état de ce bit (« 0 » pour DDRA et « 1 » pour ORA).

Tous ces registres sont représentés sur la figure en annexe

Les modules interface A et interface B sont des amplificateurs bidirectionnels pouvant délivrer un courant relativement

important, en particulier avec le modèle de PIA référencé 6822.

Ainsi, ce circuit peut servir à interfacer pratiquement n'importe quel ensemble électronique. Programmé correctement, il est

capable d'assurer les échanges entre tous les périphériques placés à proximité (tels que clavier, imprimante, disquettes,

disques durs, etc.) et connectés en mode parallèle

De la périphérie vers le processeur : La donnée disponible sur le port A en réception (port A configuré en entrée) est

directement transmise à l’amplificateur de bus de données par l’intermédiaire du bus de sortie. Elle ne transite pas par

l’ORA, il n’y a donc pas mémorisation des données en entrée.

Du processeur vers la périphérie : La donnée disponible sur le bus du MPU est chargée dans le registre de sortie B par

l’intermédiaire du bus d’entrée, elle est donc mémorisée. Le port B est en sortie, la donnée est disponible tant qu’une

nouvelle écriture n’est pas intervenue.

REDIGE PAR NKAMNDA SATEU CHRISTIAN NOEL ANNEE ACADEMIQUE 2020-2021 2

FILIERE : IIA Prépa EPS 3

Sélection des registres :

Registre de contrôle CRA - CRB :

Ce registre permet la commande et le contrôle des ports de

sortie A et B. Pour y accéder, il suffit de fixer les états

logiques sur RS1 et RS0. Ce registre va permettre d’accéder

aux autres registres : DDRA-DDRB et ORA-ORB à partir du

bit 2 du registre de contrôle :

Registres de sortie ORA – ORB :

Ce sont les registres dans lesquels vont transiter les données. Pour lire une donnée reçue par un port, il suffira de lire le

contenu de ce registre.

Registres de direction DDRA – DDRB :

Ils permettent de définir le sens de transfert de chacune des lignes des ports A et B. Un état logique « 1 » définit la ligne en

sortie, un état « 0 », en entrée. Ex : pour mettre la ligne PB4 en entrée et toutes les autres en sortie, il faut écrire la valeur

$10 dans le registre DDRB.

PROGRAMMATION D’INITIALISATION DU PIA :

(port A en entrée, port B en sortie).

REDIGE PAR NKAMNDA SATEU CHRISTIAN NOEL ANNEE ACADEMIQUE 2020-2021 3

FILIERE : IIA Prépa EPS 4

ANNEXE 1

Figure : Schéma synoptique du 6821. Le MPU peut adresser six registres en lecture et en écriture : CRA, CRB, DDRA,

DDRB, ORA et ORB

REDIGE PAR NKAMNDA SATEU CHRISTIAN NOEL ANNEE ACADEMIQUE 2020-2021 4

Vous aimerez peut-être aussi

- Pia6821 PDFDocument4 pagesPia6821 PDFMounaim MatiniPas encore d'évaluation

- PIA6821Document4 pagesPIA6821Badel TchangomPas encore d'évaluation

- Cours-Micro Chap 6Document9 pagesCours-Micro Chap 6abidhafedh_842455669Pas encore d'évaluation

- 5cpu 8086Document9 pages5cpu 8086Ben Aissa OussamaPas encore d'évaluation

- Cours Microcontrôleur MCS-51Document19 pagesCours Microcontrôleur MCS-51Maha BadriPas encore d'évaluation

- Chapitre 1 EtudiantDocument4 pagesChapitre 1 EtudiantChristianPas encore d'évaluation

- 6809 EnsaDocument15 pages6809 EnsaAchraf Rossoneri75% (12)

- Programmation Assembleur Des PICDocument12 pagesProgrammation Assembleur Des PICEden BenPas encore d'évaluation

- Chapitre 4 2020-2021Document64 pagesChapitre 4 2020-2021M'hamed Saadi BachirPas encore d'évaluation

- TD1 Solution-1 PDFDocument4 pagesTD1 Solution-1 PDFzenazel miloudPas encore d'évaluation

- Microprocesseur 8086Document79 pagesMicroprocesseur 8086Hichem Hamdi100% (3)

- Cours No 04 Etude de L'architecture Du Microprocesseur 8086Document6 pagesCours No 04 Etude de L'architecture Du Microprocesseur 8086Wassim AmamichePas encore d'évaluation

- Etude de L'architecture Du Microprocesseur 8086.: Chapitre N 04Document6 pagesEtude de L'architecture Du Microprocesseur 8086.: Chapitre N 04Zakaria ToualbiaPas encore d'évaluation

- Chapitre I Le Microprocesseur 6809Document10 pagesChapitre I Le Microprocesseur 6809Sabri AbidiPas encore d'évaluation

- Microprocess EurDocument12 pagesMicroprocess Eurmabroukoussema61Pas encore d'évaluation

- TP1 Iot 2023Document6 pagesTP1 Iot 2023Hamed KasmiPas encore d'évaluation

- 2 Cours Info Indus Partie2Document34 pages2 Cours Info Indus Partie2Mourad HoulPas encore d'évaluation

- TD 06 CorrigeDocument12 pagesTD 06 CorrigeOmar KhayyamPas encore d'évaluation

- TP Bus Et Interface Kouamé He YimingDocument7 pagesTP Bus Et Interface Kouamé He YimingMai Anh ThưPas encore d'évaluation

- Initiation Aux Microcontrôleurs dsPIC30FDocument10 pagesInitiation Aux Microcontrôleurs dsPIC30Fanon_72023590100% (1)

- Wa0000.Document2 pagesWa0000.Paréto BessanhPas encore d'évaluation

- IntroductionDocument9 pagesIntroductionabderezakpcPas encore d'évaluation

- Chapitre I Microprocesseur 6809 GSEA12013 PDFDocument56 pagesChapitre I Microprocesseur 6809 GSEA12013 PDFRyan Hj100% (1)

- Bus I2CDocument8 pagesBus I2CtechnoPas encore d'évaluation

- Architecture Et Programmation Des Micro-Contrôleurs: Khaled - Taouil@enetcom - Usf.tnDocument47 pagesArchitecture Et Programmation Des Micro-Contrôleurs: Khaled - Taouil@enetcom - Usf.tnamalPas encore d'évaluation

- Chapitre III Microprocesseur 6809 GSEA1Document36 pagesChapitre III Microprocesseur 6809 GSEA1kaoutarPas encore d'évaluation

- HC 11 JMFDocument22 pagesHC 11 JMFKarim ApcPas encore d'évaluation

- CH 04 09Document16 pagesCH 04 09Frisco Elyah AndriantsialoPas encore d'évaluation

- 15.registres MemoiresDocument6 pages15.registres MemoiresHeritiana RakotoPas encore d'évaluation

- TD Decodage Adresses - KissaouiDocument3 pagesTD Decodage Adresses - KissaouiMohamed KissaouiPas encore d'évaluation

- CH 2Document45 pagesCH 2raghda amamiPas encore d'évaluation

- 05 Les Interfaces E-S Du 8086Document9 pages05 Les Interfaces E-S Du 8086MENANI ZineddinePas encore d'évaluation

- 68hc11 v2 PDFDocument17 pages68hc11 v2 PDFmoutchedPas encore d'évaluation

- Pia 8255Document8 pagesPia 8255radn23100% (1)

- Architectures Des Ordinateurs 2: Dr. Fouzi MekhaldiDocument26 pagesArchitectures Des Ordinateurs 2: Dr. Fouzi MekhaldiRanPas encore d'évaluation

- Exercices Architecture 4 CITISEDocument8 pagesExercices Architecture 4 CITISEchfakhtPas encore d'évaluation

- Cours AUT AII M1 SESTRDocument29 pagesCours AUT AII M1 SESTRichrak.djelil.idPas encore d'évaluation

- Chapitre3 ProfDocument21 pagesChapitre3 ProfFedi AffesPas encore d'évaluation

- Les Microcontrôleurs PIC de MicrochipDocument28 pagesLes Microcontrôleurs PIC de MicrochipMohamed CoulibalyPas encore d'évaluation

- Cours-PIC Mise A JourDocument69 pagesCours-PIC Mise A JourAmil DhafPas encore d'évaluation

- Le Port SérieDocument9 pagesLe Port SérierabahPas encore d'évaluation

- Travaux Pratique 2 RLIDocument12 pagesTravaux Pratique 2 RLIKader AbdoulPas encore d'évaluation

- MicroprocesseurDocument25 pagesMicroprocesseurTH3JAZOULIPas encore d'évaluation

- Chapitre 1 Lat 54Document6 pagesChapitre 1 Lat 54radiaPas encore d'évaluation

- DSP Lf2407ADocument92 pagesDSP Lf2407AFarid KhouchaPas encore d'évaluation

- Le Pic 16f877Document5 pagesLe Pic 16f877karam karamPas encore d'évaluation

- Spi MyrioDocument14 pagesSpi MyrioelmcadbuickPas encore d'évaluation

- Pia 6809Document5 pagesPia 6809Abdelwahab EL Filali100% (2)

- Uc-16F877 DIADocument14 pagesUc-16F877 DIAPapeCheikh SYLLAPas encore d'évaluation

- Chapitre 2Document18 pagesChapitre 2EwanePas encore d'évaluation

- Modes D AdressageDocument26 pagesModes D Adressagebasma hassaniPas encore d'évaluation

- Chap 3-MicrocontroleurDocument35 pagesChap 3-MicrocontroleurYosra rhim YosraPas encore d'évaluation

- Cours DSP ISEN Partie2Document20 pagesCours DSP ISEN Partie2Smart ClassePas encore d'évaluation

- 68 HC 11Document15 pages68 HC 11Abdelhadi TaoufikPas encore d'évaluation

- Maths GénéDocument17 pagesMaths GénékoyabePas encore d'évaluation

- Chapitre 3 Electromagnetisme 2019 2020Document33 pagesChapitre 3 Electromagnetisme 2019 2020koyabePas encore d'évaluation

- Javascript IsmailDocument101 pagesJavascript IsmailIsmail Benbya100% (1)

- CV MardocheeDocument1 pageCV MardocheekoyabePas encore d'évaluation

- Cours Réseaux Chap 01Document23 pagesCours Réseaux Chap 01Ndjidama youssoufaPas encore d'évaluation

- Travail de Groupe 1Document11 pagesTravail de Groupe 1koyabePas encore d'évaluation

- Nouvelle Fiche Stage Commutation Voix & DonnéesDocument1 pageNouvelle Fiche Stage Commutation Voix & DonnéeskoyabePas encore d'évaluation

- TIA PortalDocument10 pagesTIA PortalAyoub AyayPas encore d'évaluation

- Chap 06 ActexpleffetwahwahcorrigeDocument6 pagesChap 06 ActexpleffetwahwahcorrigekoyabePas encore d'évaluation

- COURS DE GENIE LOGICIEL by Pof. YENDE R PDFDocument89 pagesCOURS DE GENIE LOGICIEL by Pof. YENDE R PDFEn Personne AlaeddinePas encore d'évaluation

- Chap 3Document15 pagesChap 3koyabePas encore d'évaluation

- TIA PortalDocument10 pagesTIA PortalAyoub AyayPas encore d'évaluation

- Physique Terminale S PDFDocument250 pagesPhysique Terminale S PDFrachid100% (9)

- UmlDocument20 pagesUmlhappylady90Pas encore d'évaluation

- AopDocument9 pagesAopNaima LaaroussiPas encore d'évaluation

- Chap 2Document18 pagesChap 2koyabePas encore d'évaluation

- CM TransmissionDataDocument63 pagesCM TransmissionDataA'chille Arouko LeKaizerPas encore d'évaluation

- AutomgenDocument9 pagesAutomgenHani ErrachidPas encore d'évaluation

- TD 03 CorrigeDocument14 pagesTD 03 CorrigerabehPas encore d'évaluation

- CH MatricesDocument21 pagesCH MatricesSergio Davensky PIERREPas encore d'évaluation

- AopDocument9 pagesAopNaima LaaroussiPas encore d'évaluation

- Corrigés Des Tests N°2: Test N°2 Sujet N°1Document10 pagesCorrigés Des Tests N°2: Test N°2 Sujet N°1koyabePas encore d'évaluation

- Exercice N°0:: État Bouton Appuyé ÉtatDocument36 pagesExercice N°0:: État Bouton Appuyé ÉtatkoyabePas encore d'évaluation

- 6 ConducteursenquilibreDocument16 pages6 ConducteursenquilibrekoyabePas encore d'évaluation

- 5 DiplelectrostratiqueDocument9 pages5 DiplelectrostratiquekoyabePas encore d'évaluation

- GHDocument28 pagesGHAina Hery100% (1)

- Corrigés Des Tests N°2: Test N°2 Sujet N°1Document10 pagesCorrigés Des Tests N°2: Test N°2 Sujet N°1koyabePas encore d'évaluation

- Flux Électrostatique Théorème de Gauss: Exercice 15 Flux Électrostatique Créé Par Une Charge PonctuelleDocument8 pagesFlux Électrostatique Théorème de Gauss: Exercice 15 Flux Électrostatique Créé Par Une Charge Ponctuellekoyabe100% (1)

- Exposé IGBTDocument8 pagesExposé IGBTIlhem Fares100% (1)

- UFS Manuel en FrançaisDocument33 pagesUFS Manuel en FrançaisMohan RajPas encore d'évaluation

- Moog D638 Series Digital Valves FRDocument0 pageMoog D638 Series Digital Valves FRnabil160874Pas encore d'évaluation

- Principe de La Conversion Analogique Numérique PDFDocument40 pagesPrincipe de La Conversion Analogique Numérique PDFnardjes merzouguiPas encore d'évaluation

- Long Term Evolution (LTE) (4G) : TitreDocument18 pagesLong Term Evolution (LTE) (4G) : TitreCoeur Verouiller0% (1)

- Cours BTS Puissance ElectromecaDocument11 pagesCours BTS Puissance ElectromecaAmadou SARRPas encore d'évaluation

- Cours API L3Document46 pagesCours API L3Badiel MarcPas encore d'évaluation

- LoRa Et LoRaWan de La Théorie À La Pratique PDFDocument83 pagesLoRa Et LoRaWan de La Théorie À La Pratique PDFYynn FerdinandPas encore d'évaluation

- Chapitre 5 L'amplificateur Opérationnel Et Ses Applications PratiquesDocument1 pageChapitre 5 L'amplificateur Opérationnel Et Ses Applications PratiquesBushraPas encore d'évaluation

- Chapitre 05Document40 pagesChapitre 05Sim BtbPas encore d'évaluation

- PDF PDFDocument74 pagesPDF PDFMoussa YameogoPas encore d'évaluation

- VX400s LED Display Controller User ManualDocument33 pagesVX400s LED Display Controller User Manualroland “RolanDelmas” delmasPas encore d'évaluation

- La DomotiqueDocument18 pagesLa Domotiquemed smiPas encore d'évaluation

- Cours 7 CpuDocument90 pagesCours 7 CpuSandra BouPas encore d'évaluation

- FT CVMDocument2 pagesFT CVMMohamed ElbanadiPas encore d'évaluation

- TP N Matlab 2Document14 pagesTP N Matlab 2Hoùssëm DhîēbPas encore d'évaluation

- Transformate UrsDocument26 pagesTransformate UrsJustin SmithPas encore d'évaluation

- Série 6 Supplémentaire - EXERCICES - SUR - SYNTHESE DES FILTRES RIIDocument5 pagesSérie 6 Supplémentaire - EXERCICES - SUR - SYNTHESE DES FILTRES RIIMe Re100% (1)

- Variateur de Vitesse Pour Moteur MonophaséDocument9 pagesVariateur de Vitesse Pour Moteur MonophaséJIHENE GHAOUIPas encore d'évaluation

- Cours Transmission Par SatelliteDocument27 pagesCours Transmission Par Satellitec68gw899fn100% (1)

- 0-Rapport PFE deFMDocument57 pages0-Rapport PFE deFMbenbark.noureddinePas encore d'évaluation

- Tutoriel HandbrakeDocument26 pagesTutoriel HandbrakeMimosa74Pas encore d'évaluation

- Réseaux CellulairesDocument66 pagesRéseaux CellulairesRaïssa TCHIBOZOPas encore d'évaluation

- RAM (Random Access Memory) : Les Mémoires Vives (RAM)Document8 pagesRAM (Random Access Memory) : Les Mémoires Vives (RAM)dettlaff xxxPas encore d'évaluation

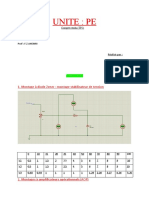

- Unite: Pe: 1. Montage À Diode Zener: Montage Stabilisateur de TensionDocument4 pagesUnite: Pe: 1. Montage À Diode Zener: Montage Stabilisateur de Tensiondouha kchPas encore d'évaluation

- Cours Redressement Simple Et Double AlternanceDocument6 pagesCours Redressement Simple Et Double AlternanceAmani AmounaPas encore d'évaluation

- Plaquette MX482 FR BDDocument2 pagesPlaquette MX482 FR BDmanskebe6121Pas encore d'évaluation

- Liste Et Brochage ConnecteursDocument10 pagesListe Et Brochage Connecteursleclick42Pas encore d'évaluation

- Transmission de L'informationDocument19 pagesTransmission de L'informationOthman NchifaPas encore d'évaluation

- 1 TP Numerisation Signal Analogique-2 PDFDocument4 pages1 TP Numerisation Signal Analogique-2 PDFAnonymous jbjqt9LhtIPas encore d'évaluation