Académique Documents

Professionnel Documents

Culture Documents

Circuits Analogiques - Problemes Et Corriges

Circuits Analogiques - Problemes Et Corriges

Transféré par

Anonymous PLxbsVTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Circuits Analogiques - Problemes Et Corriges

Circuits Analogiques - Problemes Et Corriges

Transféré par

Anonymous PLxbsVDroits d'auteur :

Formats disponibles

Enseignements E.E.A.

Electronique analogique

P r o b lè m e s

e t c o r r ig é s

année 2010

par Sylvain Géronimi

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

TABLE DES PROBLEMES

Partie 1

Rappel sur la théorie des circuits

Mise en équations et théorèmes fondamentaux 3-4

Réponse d’un circuit RL 5-8

Corrélation entre temps de montée et fréquence de coupure d’un circuit RC 9-10

Sonde passive d’oscilloscope 11-12

Caractérisation d’un quadripôle 13-15

Sensibilité d’un pont de Wheatstone 16-17

Polarisation d’un transistor

Dispersion des caractéristiques d’un JFET 18-20

Polarisation d’un JBT par diverses topologies 21-22

Stabilisation par résistance d’émetteur 23-26

Caractérisation d’un étage

Etage déphaseur à JBT 27-30

Etage source commune 31-33

Etage collecteur commun chargé par un miroir de courant 34-36

Etage différentiel à JBT 37-39

Etage différentiel à JFET 40-42

Réponse en fréquence

Réponse en fréquence d’un étage émetteur commun 43-50

Réponse en fréquence d’un étage base commune 51-55

Réponse en fréquence d’un étage collecteur commun 56-59

Comparaison des performances des montages fondamentaux à JBT 60

Réponse en fréquence d’un étage pseudo émetteur commun 61-64

Réponse en fréquence d’un étage source commune 65-70

Réponse en fréquence d’un étage pseudo-source commune 71-74

Réponse en fréquence d’un montage cascode 75-78

Réponse en fréquence d’un montage émetteur commun collecteur commun 80-86

Eléments de circuits intégrés

Miroir de courant élémentaire pour polarisation d’étage 87-88

Miroir de courant élémentaire pour transfert dynamique 89-90

Source de courant simple à JFET pour polarisation d’étage 91

Source de courant à gain pour polarisation d’étage 92-93

Source de Wilson pour transfert dynamique 94-96

Source de Widlar en répétiteur de courant pour polarisation d’étages 97-98

Multiplicateur de VBE 99-100

Réalisation d’une opération arithmétique complexe (1 et 2) 101-102

Conception d’un buffer 103-109

Etage différentiel à charges asymétriques 110-112

Etage différentiel à charges actives (partie 1) 113-119

Etage de tension (partie 2) 120-124

Etage différentiel cascode à charges actives (miroir) 125-133

Partie 2

Amplificateurs idéaux

Intégrateur de tension différentielle 134

Convertisseurs d’impédance 135-136

Amplificateur d’instrumentation amélioré 137-139

Amplificateur d’instrumentation INA 114 140

Amplificateurs logarithmiques et exponentiels 141-142

Multiplicateur / diviseur 143-144

Amplificateurs à conductance de transfert 145-148

Voir aussi « Le filtrage analogique »

Sylvain Géronimi Page 1 Tables des problèmes

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Filtrage analogique

Filtre passe-bas à deux suiveurs de tension 149-151

Filtre passe-bas à contre-réaction multiple (structure de Rauch) 152-156

Filtre passe-bas à source contrôlée (structure Sallen-Key) 157-162

Conception d’un filtre passe-haut Butterworth d’ordre 4 163-166

Filtre passe-bande à contre-réaction multiple (structure de Rauch) à sensibilité améliorée 167-169

Filtre passe-bande à INIC 170-172

Filtre passe-tout (déphaseur pur) du premier ordre 173-174

Filtre passe-tout (déphaseur pur) du second ordre 175-177

Filtre réjecteur à deux amplificateurs de tension 178-180

Filtre réjecteur à variable d’état 181-183

Filtre universel 184-187

Oscillateurs sinusoïdaux

Oscillateur triphasé 188

Oscillateur à pont RLC 189-190

Oscillateur à pont RLC avec potentiomètre 191-192

Oscillateur à pont de Wien 193-196

Oscillateur Colpitts 197-201

Oscillateur Colpitts (variante) 202

Oscillateur Clapp 203

VCO à JFET source commune 204-207

VCO à JFET drain commun 208-210

Régulateurs de tension

Principe de stabilisation par diode zener 211-213

Circuits de stabilisation d’une tension par référence zener 214-221

Régulateur de tension 15 V / 2 A 222-223

Amplificateurs de puissance

Etage de puissance push-pull série avec sources de Widlar 224-229

Etage suiveur piloté par un amplificateur de tension intégré et contre-réaction 230-235

Etage de puissance push-pull série en pont 236-240

Partie 3

Quelques structures de circuits intégrés

Amplificateur de tension LM 741 simplifié 241-257

Amplificateur de tension TL071 (technologie BiFet) 258-264

Amplificateur Norton LM 359 et applications 265-276

Amplificateur à conductance de transfert LM 13600 et application 277-284

Buffer et amplificateur à conductance de transfert OPA 660 et applications 285-395

Amplificateur à contre réaction de courant LT1223 et application 296-306

Comparateur LM 139 307-312

PLL analogique NE 565 et applications 313-337

Annexes

Modèles de composants associés aux différents régimes (diode, JBT, JFET) 338-342

Méthode de travail pour la caractérisation linéaire d’un étage différentiel symétrique 343-344

Méthode de travail pour la caractérisation linéaire d’un circuit complexe 344-345

Méthode de travail pour l’analyse en fréquence (approximation du pôle dominant) 346-347

Transformation de schéma par application du théorème de Miller 348-349

Bibliographie, symboles, notations 350

Sylvain Géronimi Page 2 Tables des problèmes

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

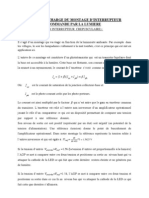

Mise en équations et théorèmes fondamentaux

Diviseur de tension

R1

VE R2 VS

R3

Exprimez la tension VS en fonction de VE , R1, R2 , R3 .

Diviseur de courant

I

I2

R1 R2 R3 V

Exprimez le courant I 2 en fonction de I, R1, R 2 , R3 .

Application du théorème de Millman

R1 V1 I

10

V R2 R

10 V 30 5

Evaluez le courant I.

Application du théorème de Thévenin et de superposition

R1 R3

I

V R2

Donnez le générateur de Thévenin équivalent au dipôle.

Sylvain Géronimi Page 3 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Corrigé

Diviseur de tension

⎧VE = (R1 + R2 + R3 )I R2

⎨ ⇒ VS = VE

⎩VS = R 2 I R1 + R2 + R3

Diviseur de courant

⎧ V V V 1

⎪I = R + R + R

⎪ R2

⎨

1 2 3

⇒ I2 = I

⎪I = V 1 1 1

+ +

⎪⎩ 2 R2 R1 R2 R3

Application du théorème de Millman

V 1

R1 V1 R

Calcul du potentiel de nœud : V1 = ⇒ I= = V ( I = 0 .6 A )

1 1 1 R 1 1 1

+ + + +

R1 R2 R3 R1 R2 R

Application du théorème de Thévenin et de superposition

La présence des deux sources indépendantes V et I invite à utiliser le théorème de superposition

pour le calcul de la tension de Thévenin VTh (tension à vide du dipôle). Ce calcul s’effectue donc

en deux étapes :

R2

1ère étape : extinction de la source de courant ( I = 0 , circuit ouvert) VTh1 = V.

R1 + R2

R1 R2

2ème étape : extinction de la source de tension ( V = 0 , court-circuit) VTh2 = I.

R1 + R2

R2 R R

d’où la superposition VTh = VTh1 + VTh2 = V+ 1 2 I.

R1 + R2 R1 + R2

La résistance du dipôle se calcule en éteignant les deux sources indépendantes, ce qui donne

R R

RTh = 1 2 + R3 .

R1 + R2

Sylvain Géronimi Page 4 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Réponse temporelle d’un circuit RL

Soit le circuit RL avec condition initiale nulle.

vE 100 L

100mH

Une excitation sinusoïdale d’amplitude crête VE est appliquée au circuit. Le but du problème est

d’obtenir les réponses du courant i (t ) circulant dans la maille et de la tension aux bornes de

l’inductance v L (t ) par les trois techniques suivantes :

Réponse temporelle (variable t)

1. Ecrivez l’expression analytique du courant.

2. Ecrivez l’expression analytique de la tension.

3. Démontrez que la tension est en avance de π/2 par rapport au courant en régime permanent.

Régime sinusoïdal établi (variable jω)

4. Ecrivez les expressions du module et de l’argument du courant et de la tension.

5. Comparez ces résultats à ceux obtenus précédemment en régime permanent.

Transformées de Laplace (variable p)

6. Ecrivez la fonction de transfert en tension VL ( p) VE ( p) .

7. Par transformées de Laplace, donnez l’expression de la tension.

Corrigé

Réponse temporelle

⎧ d

⎪⎪v E (t ) = R i (t ) + L dt i (t ) L

⎨ (posons τ = )

⎪v (t ) = L d i (t ) R

⎪⎩ L dt

1. Expression analytique du courant

d 1 v (t )

Résolvons l’équation différentielle du premier ordre i (t ) + i ( t ) = E en quatre étapes :

dt τ L

c équation homogène

t

d 1 di dt i t −

i (t ) + i (t ) = 0 ⇒ =− ⇒ Log =− d’où i H (t ) = λ e τ

dt τ i τ λ τ

d variation de la constante

VE sin(ω t ) VE

[ ]

t

−

λ ' (t ) e τ = = ℑm e jω t

L L

Sylvain Géronimi Page 5 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

⎡ ⎤

⎡ ⎛⎜ 1 + j ω ⎞⎟t ⎤ t

⎢ e jω t ⎥

VE VE τ

⇒ λ (t ) =

L

ℑm e ⎢

⎢

⎝τ ⎠ ⎥

dt =

⎥ ∫L

e ℑm ⎢

⎢ 1

+ ω

⎥

⎥

⎣ ⎦ ⎢⎣ τ

j

⎦⎥

⎡ ⎤

⎢ cos(ω t ) + j sin(ω t ) ⎥ ⎡1 ⎤

⎢τ sin(ω t ) − ω cos(ω t )⎥ = sin(ω t − α )

1

car ℑm ⎢ ⎥=

+ω ⎣ ⎦

⎢ 1 ⎥ 1

+ jω 2

⎣⎢ τ ⎦⎥ τ 2

+ ω 2 = 1 avec α = arctg (τ ω ) et τ = 1 + τ 2ω 2

1 1

en posant cos α = et sin α = ω ⇒

τ τ2

e solution particulière de l’équation complète

t

−

sin(ω t − α )

VE

i P (t ) = λ (t ) e τ d’où i P (t ) =

R + L2ω 2

2

f solution globale

t

− VE

i (t ) = λ e τ + i P (t ) avec i (0) = 0 ⇒ λ = sinα

R + L2ω 2

2

t

−

sin(ω t − α )

VE VE

d’où i (t ) = sin α e τ +

R +L ω 2 2 2

R + L2ω 2

2

Le premier terme correspond au régime transitoire et le second terme au régime établi ou

permanent.

2. Expression analytique de la tension

⎡ 1 −

t ⎤ ⎡ −

t ⎤

v L (t ) = VE ⎢− sin α e τ + ω cos(ω t − α )⎥ = VE sin α ⎢− cos α e τ + cos(ω t − α )⎥

⎢⎣ τ ⎥⎦ ⎢⎣ ⎥⎦

3. Déphasage

⎛ π ⎞ ⎛π ⎞ π

cos(ω t − α ) = sin⎜ ω t + − α ⎟ ⇒ ϕL − ϕI = ⎜ − α ⎟ − (− α ) = +

⎝ 2 ⎠ ⎝ 2 ⎠ 2

Régime transitoire (VE =1 V et f = 1 kHz)

régime transitoire

1.0V

0V

-1.0V

0s 0.5ms 1.0ms 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms

V(L) V(E)

Time

Sylvain Géronimi Page 6 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Régime permanent

1 2 2.0mA

1.0V

1.0mA

tension

d'entrée

(0°)

0V 0A

tension

en avance

de 9° courant

en retard

-1.0mA de 81°

-1.0V

>>

-2.0mA

18.0ms 18.5ms 19.0ms 19.5ms 20.0ms

1 V(L) V(E) 2 I

Time

Régime sinusoïdal établi

⎧⎪VE = (R + jLω ) I VE jLω

⎨ ⇒ I= et VL = VE

⎪⎩VL = jLω I R + jLω R + jLω

4. Modules et arguments

VE Lω

I = et ϕI = ϕ E − arctg ( VE = VE e jϕE )

R +Lω

2 2 2 R

Lω π Lω

VL = VE et ϕL = ϕE + − arctg

R 2 + L2ω 2 2 R

5. Comparaison du régime établi

i (t ) =

VE

sin(ω t + ϕI ) ↔ [

I ℑm e j (ω t +ϕI ) ]

R +L ω

2 2 2

v L (t ) = VE sin α sin(ω t + ϕ L ) avec sin α = ω =

Lω

τR

=

Lω

↔ [

VL ℑm e j (ω t +ϕL ) ]

R + L2ω 2

2

Transformées de Laplace

⎧VE ( p ) = (R + Lp ) I ( p )

⎨

⎩VL ( p ) = Lp I ( p )

6. Fonction de transfert

p

V ( p) ωn R 1

H ( p) = L = avec ωn = =

VE ( p ) p L τ

1+

ωn

Sylvain Géronimi Page 7 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

7. Expression de la tension aux bornes de l’inductance

ω ω

Tableau des transformées : sin(ω t ) →

p

⇒ VL ( p ) = VE

p +ω

2 2

p + p +ω

1 2 2

τ

Décomposition en éléments simples :

(a + b )p 2 + ⎛⎜ b + c ⎞⎟ p + c + aω 2

p

=

a

+

bp + c

= ⎝τ ⎠ τ

⎛ 1⎞ 2

(

⎜p + ⎟ p +ω

⎝ τ⎠

2

p +

τ

)

1 p2 + ω 2 ⎛

(

1⎞ 2

⎜p + ⎟ p +ω

⎝ τ⎠

2

)

τ τ 2ω 2

⇒ b=−a= , c =

1 + τ 2ω 2 1 + τ 2ω 2

⎡ ⎤

ω ⎢ 1 1 1 p ω ⎥

VL ( p ) = VE ⎢− + +ω 2 ⎥

⎛ 1⎞ ⎢ τ p + τ p +ω p +ω ⎥

2 1 2 2 2

ω + ⎜ ⎟ ⎢⎣

2

τ ⎥⎦

⎝τ ⎠

ω

→ sin(ω t ) , 2 → cos(ω t )

1 p

Tableau des transformées : → e − at , 2

p+a p +ω 2

p + ω2

2

⎛ 1⎞

⇒ ω 2 + ⎜ ⎟ = 1 et cos α cos(ω t ) + sin α sin(ω t ) = cos(ω t − α )

1

Posons cos α = et sinα = ω

τ ⎝τ ⎠

⎡ −

t ⎤

d’où v L (t ) = VE sin α ⎢− cos α e τ + cos(ω t − α )⎥

⎢⎣ ⎥⎦

La technique dans le domaine temporel est d’une grande complexité, puisqu’elle fait apparaître des

équations intégro-différentielles dont la résolution mathématique est rapidement limitée (utilisation du

calcul numérique). La technique du calcul complexe est aisée, mais limitée uniquement à une

excitation sinusoïdale fournissant le régime permanent (pas de transitoire). L’étude par les

transformées de Laplace est la méthode la plus généraliste, pouvant fournir la réponse du circuit à

une excitation quelconque.

Sylvain Géronimi Page 8 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Corrélation entre temps de montée et fréquence de coupure d’un circuit RC

Soit le circuit RC avec condition initiale nulle.

vE C

Un échelon unité de tension d’amplitude VE est appliqué au circuit. Le but du problème est d’écrire la

relation exprimant la corrélation entre temps de montée et fréquence de coupure du circuit.

1. Ecrivez la fonction de transfert en tension VC ( p ) VE ( p ) et tracez les courbes de réponse dans le

plan de Bode (module et argument).

2. Par transformées de Laplace, donnez l’expression de la tension v C (t ) .

3. Ecrivez l’expression du temps de montée t r défini par la différence des temps pour atteindre

respectivement 90% et 10% de la valeur finale en fonction de la constante de temps du circuit.

4. Ecrivez la relation entre la fréquence de coupure fh du circuit passe-bas et le temps de montée.

Corrigé

1. Fonction de transfert

A partir de l’équation dans le domaine temporel, on écrit

d 1 v (t ) 1 1

v C (t ) + v C (t ) = E → p VC ( p ) + VC ( p ) = VE ( p)

dt τ τ τ τ

⎧ ⎛ 1 ⎞

⎪VE ( p ) = ⎜⎜ R + ⎟ I ( p)

⎪ ⎝ C p ⎟⎠ V ( p) 1

ou directement ⎨ ⇒ H ( p) = C = avec τ = RC

⎪V ( p ) = 1 I ( p ) VE ( p ) 1 + τp

⎪ C

⎩ Cp

⇒ H dB = −20 log 1 + (ωτ ) , ϕ = − arctg (ωτ )

1

En régime sinusoïdal, H ( jω ) =

2

1 + j ωτ

1 0 2 0d

-10 (159.436,-3.0185)

-20 -50d

(159.652,-45.089)

-30 filtre du premier ordre

τ = 1 ms

-40 -100d

1.0Hz 10Hz 100Hz 1.0KHz 10KHz

1 DB(VC) 2 P(VC)

Frequency

Sylvain Géronimi Page 9 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

2. Réponse à l’échelon de tension

VE V V VE

VC ( p ) = = E − E avec VE ( p ) = (échelon de tension d’amplitude VE )

p (1 + τ p ) p 1 p

p+

τ

⎛ −

t ⎞

v C (t ) = VE ⎜1 − e τ ⎟

1

Tableau des transformées F ( p ) = → f (t ) = e − α t ⋅ u(t ) , d’où

p +α ⎜ ⎟

⎝ ⎠

L’application des théorèmes de la valeur initiale et de la valeur finale donne immédiatement la

valeur de cette fonction à l’origine et au temps infini sans qu’il soit nécessaire de calculer vC(t) :

VE

pVC ( p ) = ⇒ lim pVC ( p ) = lim v C (t ) = 0 et lim pVC ( p ) = lim v C (t ) = VE

1+ τ p p→∞ t →0 p→0 t →∞

1.2V

vE(t)

0.8V vC(t)

t = 3 ms

VC = 95 %

0.4V t = 1 ms de VE

VC = 63.2 %

de VE

0V

0s 1.0ms 2.0ms 3.0ms 4.0ms

Temps

⎡d ⎤ V

VE = 1V , τ = 1 ms , pente à l’origine ⎢ v C (t )⎥ = E , v C (τ ) ≅ 0.632 V , v C (3τ ) ≅ 0.95 V

⎣ dt ⎦t =0 τ

3. Expression de t r (τ )

⎧ 10

⎪v C (t1 ) = 0.1VE → t1 = τ Ln

⎨ 9 ⇒ t r = t 2 − t1 = τ Ln 9 soit t r ≅ 2.2 τ

⎪v (t ) = 0.9V → t 2 = τ Ln 10

⎩ C 2 E

L’échelon est la combinaison de la variation de la tension la plus abrupte et de la plus lente

variation possible de tension.

4. Expression de t r (fh )

1 1 2 .2 0.35

H ( p) = avec ωh = ⇒ tr ≅ ou t r ≅

1+

p τ ωh fh

ωh

fh étant la fréquence de coupure haute du passe-bas du 1° ordre.

Si le système est un passe-bas à plusieurs pôles, cette relation est une approximation d’autant

meilleure que la valeur de fh est faible devant celles des autres pôles (pôle dominant).

Sylvain Géronimi Page 10 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Sonde passive d’oscilloscope

Soit le schéma de principe d’une sonde passive atténuatrice.

embout de sonde

CS

câble de mesure entrée de l'oscilloscope

RS

vE CP

CC R0

capacité v0

100p 1Meg 13p

du câble

L’amplificateur vertical de l’oscilloscope est représenté par le schéma équivalent parallèle R0 - C p aux

bornes duquel existe la tension v 0 (t ) .

1. Ecrivez la fonction de transfert V0 ( p) VE ( p) .

2. Donnez la condition pour que la fonction de transfert soit indépendante de la fréquence. Evaluez

la résistance RS pour avoir une atténuation de rapport 1/10 et déduisez la valeur de la capacité

CS0 découlant de la condition.

3. Déterminez l’impédance d’entrée de la sonde branchée sur l’oscilloscope, sous forme d’un

schéma R-C parallèle à la condition précédente.

4. Calculez et tracez les réponses temporelles de v 0 (t ) à un échelon de tension unité pour une

capacité de sonde réglée aux valeurs CS0 ± ∆CS (on supposera que CS >> ∆CS 10 et que les

bandes passantes de la sonde et de l’oscilloscope sont très larges).

Le temps de montée lu sur l’écran d’un oscilloscope est donné par t rlu ≅ t r2signal + t r2oscillo + t r2sonde . Pour

effectuer cette mesure, on dispose d’un oscilloscope associé à une sonde dont les bandes passantes

sont respectivement de 100 MHz et de 500 MHz.

5. Calculez l’erreur commise sur la mesure de signaux carrés dont le temps de montée serait de 5

ns et 50 ns.

0.35

Formulaire : t r ≅ , t r lu = t r2signal + t r2oscillo + t r2sonde .

fh

Corrigé

Posons C0 = CC + CP = 113 pF , τ 0 = R0C0 et τ S = RSCS .

1. Fonction de transfert

V0 ( p ) Z0 ( p ) R R0 1 + τS p

H ( p) = = avec Z ( p ) = ⇒ H ( p) =

VE ( p ) Z0 ( p ) + ZS ( p ) 1 + RCp R0 + RS R0τ S + RSτ 0

1+ p

R0 + RS

2. Condition pour un régime apériodique

R0τ S + RSτ 0

La fonction de transfert est indépendante de la fréquence si τ S = soit τ S = τ 0 .

R0 + RS

Sylvain Géronimi Page 11 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

⎧RS = 9R0 = 9 MΩ

R0 1 ⎪

Sonde atténuatrice de rapport 1/10 → H = = ⇒ ⎨ C0

R0 + RS 10 ⎪CSO = = 12.56 pF

⎩ 9

3. Impédance d’entrée de la sonde

Z E ( p ) = ZS ( p ) + Z 0 ( p )

10 R0 RE

Au réglage optimal de la sonde → ZE ( p ) = = soit RE = 10 R0 = 10 MΩ en

1 + R0C0 p 1 + RE CE p

parallèle avec CE = C0 10 = 11.3 pF .

4. Réponses temporelles

CS = CS 0 ± ∆CS ⇒ τ S = τ 0 ± ∆τ

⎛ ⎞

⎜ ⎟

1 1 + (τ 0 ± ∆τ )p 1 ⎛ ∆τ p ⎞ 1 ⎜ 1 ∆τ 1 ⎟

H ( p) = ≅ ⎜1 ± ⎟ d’où V0 ( p ) ≅ ±

10 ⎛ ∆τ ⎞ 10 ⎝ 1 + τ 0 p ⎟⎠

⎜ 10 ⎜ p τ 0 1 ⎟

1 + ⎜τ 0 ± ⎟p ⎜ +p⎟

⎝ 10 ⎠ ⎝ τ0 ⎠

⎛ t ⎞

1 ⎜ ∆CS − τ 0 ⎟

Transformation inverse de Laplace → v 0 (t ) ≅ 1 ± e

10 ⎜⎜ CS0 ⎟⎟

⎝ ⎠

Trois cas de réglage de la sonde apparaissent au sein de la simulation ci-dessous, à savoir la

compensation optimale (∆CS = 0), la surcompensation (∆CS > 0), la sous compensation (∆CS < 0).

200mV

surcompensation Réponse à un signal carré d’amplitude 2 Vpp

100mV

vO(t)

sous compensation

0V

compensation

optimale

-100mV

Réglage de la sonde à ∆Cs/Cs

-200mV

0s 0.2ms 0.4ms 0.6ms 0.8ms 1.0ms

Time

5. Erreur commise sur la mesure

0.35

Instrumentation : t r oscillo = = 3.5 ns (bande passante 100 MHz)

10 8

0.35

t rsonde = = 0.7 ns (bande passante 500 MHz)

5 10 8

Signal : t rlu ≅ t rsignal (à 1 % près) pour t r signal = 50 ns

t rlu ≅ 6.14 ns , soit une erreur de 1.14 ns (23%) pour t rsignal = 5 ns .

Pour l’étude de circuits numériques, nous constatons que l’instrumentation n’est pas assez

performante.

Sylvain Géronimi Page 12 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Caractérisation d’un quadripôle

Le but de ce problème est de caractériser un quadripôle, c’est-à-dire d’évaluer ses résistance d’entrée

et de sortie et son transfert, en présence d’une source contrôlée.

i1 is

Rg R1

k i1 R2 vs Rch

ve

vg

1. Déterminez la résistance d’entrée Re du quadripôle chargé par Rch .

2. Déterminez les éléments RTh et vTh de Thévenin formant le dipôle de sortie du quadripôle non

chargé par Rch .

3. Dessinez le nouveau schéma équivalent du quadripôle, puis dessinez ce schéma sous la forme

modélisée d’un amplificateur de tension.

Corrigé

La difficulté de la mise en équations du système linéaire et de sa résolution vient de la présence de la

source de courant k i1 contrôlée par le courant i1 de la branche supportant la résistance R1 . Ce type

de source, symbolisée par un losange, représente une modélisation de comportement correspondant

à un transfert d’un courant de branche (branche contrôlante) vers une autre branche (branche

contrôlée) à un coefficient constant près (k). La source est donc dépendante d’une autre branche et,

de ce fait, n’a rien de commun avec une source fournissant une excitation au circuit tel que le

générateur indépendant de tension symbolisé par un cercle ( v g ).

1. Expression de la résistance d’entrée

Le quadripôle, chargé par la résistance de charge Rch , constitue un dipôle dont la résistance

équivalente Re est obtenue par l’application du théorème de Thévenin/Norton.

v0

Par définition, la résistance d’entrée s’écrit Re = d’après le schéma à droite ci-dessous.

i1

i1 i1

R1 i2

v0 k i1 R2 Rch → v0 Re

La topologie du circuit se simplifie en posant Req = R2 // Rch , ce qui conduit à l’écriture d’une

maille et d’un nœud.

⎪⎧v 0 = R1 i1 + Req i 2

⎨ ⇒ v 0 = R1 i1 + Req (k + 1)i1 , d’où Re = R1 + (k + 1)(R2 // Rch )

⎪⎩(k + 1)i1 = i 2

Sylvain Géronimi Page 13 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

2. Expressions des éléments de Thévenin

La tension de Thévenin étant une tension à vide, la résistance de charge est donc débranchée. La

topologie présente une maille et un nœud, soit deux équations auxquelles il faut ajouter la tension

aux bornes de la résistance R 2 afin de définir vTh .

i1

Rg R1 i2

k i1 R2 vth

vg

⎧(k + 1)i1 = i 2 ⎧ ⎛ Rg + R1 ⎞

⎪

( ) ⎪v g = ⎜⎜

⇒ ⎨

+ R2 ⎟⎟ i 2

d’où vTh =

(k + 1)R2

⎨v g = Rg + R1 i1 + R2 i 2 ⎝ k + 1 ⎠ vg

⎪ ⎪ Rg + R1 + (k + 1)R2

⎩vTh =R2 i 2 ⎩ Th

v = R i

2 2

Le dipôle devant être passif, la source indépendante de tension v g est éteinte, mais la source de

v0

courant contrôlée par le courant i1 est présente. La résistance du dipôle s’écrit RTh = .

i0

i1 i0 i0

R1 i2

Rg k i1 R2 v0

→ RTh v0

vg = 0

La topologie présente deux mailles et un nœud, donc un système de trois équations à résoudre

⎧i 0 + (k + 1)i1 = i 2

⎪

+ (k + 1)

v0 v0

⎨v 0 =R2 i 2 ⇒ i0 =

Rg + R1

⎪v = − R + R i

⎩ 0 g ( 1 1 ) R2

1 1 k +1 Rg + R1

d’où = + (conductance) ou encore RTh = R2 // (résistance).

RTh R2 Rg + R1 k +1

3. Schémas équivalents du quadripôle

Le générateur ( v g , Rg ) voit à ses bornes la résistance d’entrée du quadripôle et la charge voit à

ses bornes le dipôle équivalent sous forme Thévenin.

Rg RTh

Re vs Rch

vg vTh

Sylvain Géronimi Page 14 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

La modélisation du quadripôle sous la forme d’un amplificateur de tension utilise une source de

tension contrôlée par la tension v e aux bornes de la branche contrôlante supportant Re . D’autre

part, la résistance de sortie Rs du quadripôle s’identifie à RTh .

Rg Rs

ve Re vs Rch

vg Av ve

Sylvain Géronimi Page 15 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Sensibilité d’un pont de Wheatstone

Le schéma du pont de Wheatstone est le suivant.

R1 R3

VE

1 VM 2

1Vdc

R2 R4

Le but de ce problème est de définir les conditions sur les quatre résistances afin d’obtenir une

sensibilité maximale du pont.

1. Ecrivez l’expression analytique de la tension différentielle VM aux points de mesure 1 et 2 et

déduisez la condition pour que cette tension soit nulle.

2. Déterminez la sensibilité du pont et écrivez la condition sur les résistances pour que cette

sensibilité soit maximale.

3. Pour des résistances à tolérance 1%, évaluez l’erreur maximale sur la tension VM dans le cas

d’une sensibilité maximale du pont.

Corrigé

1. Condition d’équilibre du pont

⎧ R2

⎪V1 = R + R VE ⎛ R2

⎪ R4 ⎞

⎨

1 2

⇒ VM = ⎜⎜ − ⎟ VE

⎟

⎪V = R 4 ⎝ 1

R + R 2 R 3 + R4 ⎠

V

⎪⎩ 2 R3 + R4 E

La condition pour que la tension différentielle VM soit nulle est R1R 4 = R2R3 .

2. Sensibilité du pont

La tension différentielle est fonction de cinq paramètres VM (R1, R2 , R3 , R 4 , VE ) et l’approche au

∂VM ∂V ∂V ∂V ∂V

premier ordre donne dVM = dR1 + M dR2 + M dR3 + M dR4 + M dVE avec

∂R1 ∂R2 ∂R3 ∂R4 ∂VE

∂VM R2 a 1 ∂VM R1 a 1

=− VE = − VE , = VE = VE ,

∂R1 (R1 + R2 )2

(a + 1) R1

2 ∂R2 (R1 + R2 )2

(a + 1) R2

2

∂VM R4 a 1 ∂VM R3 a 1

=− V =− VE , = V = VE ,

∂R3 (R3 + R4 )2 E

(a + 1) 3

2 R ∂R 4 (R3 + R4 )2 E

(a + 1) 4

2 R

∂VM R2 R4 R R

= − = 0 en posant 1 = 3 = a .

∂VE R1 + R2 R3 + R4 R2 R 4

⎛ dR1 dR2 dR3 dR 4 ⎞ a

d’où dVM = S ⎜⎜ − + − + ⎟ VE avec S =

⎝ R1 R2 R3 R4 ⎟⎠ (a + 1)2

Sylvain Géronimi Page 16 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

dS 1

La sensibilité devient maximale si =0 ⇒ a = 1 , Smax =

da 4

d’où la condition R1 = R2 et R3 = R 4 .

3. Erreur maximale sur la tension différentielle

∆R

∆VM = S 4 VE et pour Smax , ∆VM max = 10 mV

R

La sensibilité du détecteur de zéro doit être meilleure que l’erreur maximale. Ainsi, pour mesurer

des résistances avec une précision de 1% à partir d’une source fournissant 1 V, il faut que le

détecteur ait une sensibilité meilleure que 10 mV.

Sylvain Géronimi Page 17 Rappel sur la théorie des circuits

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Dispersion de caractéristiques d’un JFET

L’étude porte sur la comparaison de la dispersion, en régime continu, obtenue à partir de deux

topologies de schéma (figures 1 et 2). Le constructeur donne les dispersions suivantes pour le

transistor à effet de champ de type 2N4416A :

dispersions maximales → I DSS = 15 mA, VP = − 6 V

dispersions minimales → I DSS = 5 mA, VP = − 2.5 V

RD RG1 RD

2k 2k

J2N4416A J2N4416A

VCC VCC

J1 J1

30 V 30 V

RS RG2 RS1

1Meg

figure 1 figure 2

Polarisation automatique (figure 1)

La polarisation du transistor est obtenue automatiquement par la tension continue produite aux bornes

de la résistance de source. Le transistor à dispersion maximale est d’abord monté dans ce circuit, puis

remplacé par le transistor à dispersion minimale.

1. Calculez la résistance de source RS pour avoir le point de fonctionnement VGSo = − 2 V dans le

cas de dispersion maximale.

2. Evaluez la dispersion sur I Do , VDSo , VGSo .

Polarisation mixte (figure 2)

Une autre façon de polariser le transistor est employée, mettant en oeuvre la polarisation automatique

utilisée précédemment associée à un pont de grille. Dans le cas où la résistance RG1 est de valeur

infinie, le montage redevient à polarisation automatique. Les démarches analytiques restent

identiques, si ce n’est d’introduire la nouvelle valeur de la résistance de source.

3. En prenant la résistance de source RS1 = 3 RS , calculez la résistance de pont de grille RG1 pour

avoir le point de fonctionnement VGSo = − 2 V dans le cas de dispersion maximale.

4. Evaluez la dispersion sur I Do , VDSo , VGSo .

Comparaison des deux topologies

5. Concluez sur le choix de la topologie du circuit.

Sylvain Géronimi Page 18 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Corrigé

Polarisation automatique

1. Evaluation de la résistance RS

+VCC

⎧ ⎛ V ⎞

2

⎪I D = I DSS ⎜1 − GS ⎟⎟

RD ⎨ ⎜ (transistor)

⎝ VP ⎠

⎪

ID

(

⎩ S

I ≅ I D )

IG=0

VDS

VGS ⎧VCC ≅ (RD + RS )I D + VDS

⎨ (circuit)

⎩VGS ≅ − RS I D

RS

système de 3 équations à 3 inconnues ( I D , VDS , RS )

2

⎛ VGSo ⎞ − VGSo

I Do = I DSS ⎜⎜1 − ⎟ ≅ 6.67 mA , RS ≅

⎟ ≅ 300 Ω , VDSo ≅ VCC − (RD + RS )I Do ≅ 14.7 V

⎝ VP ⎠ I Do

2. Evaluation des dispersions

Le transistor à dispersion minimale est monté en place du transistor précédent. Les équations du

système à résoudre demeurent inchangées, mais les inconnues sont maintenant I D , VGS , VDS , ce

qui conduit à la résolution d’une équation du second degré.

2

VGS ⎛ 1 2 ⎞

+ ⎜⎜ − ⎟VGS + 1 = 0 ⇒ VGS ≅ − 0.74 V telle que VP < VGS < 0 (JFET canal N)

⎟

VP2 ⎝ I DSS RS VP ⎠

o 0

− VGSo

et I Do = ≅ 2.48 mA , VDSo = VCC − (RD + RS )I Do ≅ 24.3 V

RS

Les dispersions extrêmes donnent des écarts de position du point de repos dans le plan de sortie

∆ I D ≅ 4.2 mA , ∆VDS ≅ 9.6 V pour cette structure de circuit.

Polarisation mixte

3. Evaluation de la résistance de pont de grille RG1

Une maille d’entrée unique apparaît après application du théorème de Thévenin.

+VCC 2

⎛ V ⎞

I D = I DSS ⎜⎜1 − GS ⎟⎟ (transistor)

RD

⎝ VP ⎠

( )

ID

RG

IG=0 ⎧⎪VCC ≅ RD + RS1 I D + VDS

VDS ⎨ (circuit)

⎪⎩VGS ≅ VG − RS1 I D

VGS

VG

RS1

RG2

avec VG = VCC , RG = RG1 // RG2

RG1 + RG2

Sylvain Géronimi Page 19 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

I Do ≅ 6.67 mA , VG ≅ 4 V , RG1 ≅ 6.5 MΩ , VDSo ≅ 10.7 V

4. Evaluation des dispersions

Le transistor à dispersion minimale est monté en place du transistor précédent.

2

VGS ⎛ 1 2 ⎞⎟ VG

+⎜ − V + 1− = 0 ⇒ VGSo ≅ − 0.11V , I Do ≅ 4.57 mA , VDSo ≅ 16.7 V

VP2 ⎜ I DSS RS VP ⎟ GS I DSS RS1

⎝ 1 ⎠

Les dispersions extrêmes donnent des écarts de position du point de repos dans le plan de sortie

∆ I D ≅ 2.1 mA , ∆VDS ≅ 6 V pour cette structure de circuit.

5. Conclusion

La polarisation mixte diminue le phénomène de dispersion. En effet dans le plan de sortie, les

plages des coordonnées du point de repos sont réduites de ∆I D = 4.2 mA → 2.1 mA et

∆VDS = 9.6 V → 6 V .

Sylvain Géronimi Page 20 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Polarisation d’un transistor bipolaire

L’étude porte sur diverses topologies permettant de polariser un transistor bipolaire avec un courant

de collecteur donné et se placer sensiblement au milieu de la droite de charge statique dans les

caractéristiques de sortie.

Le transistor est de type 2N1711 ( β typique = 150 ).

RB RC RC

RB

VCC VCC

20 V 20 V

Q1 Q1

figure 1 figure 2

RB RC RB1 RC

100k

VCC VCC

Q1 20 V Q1 20 V

RE RB2 RE

180 180

figure 3 figure 4

Déterminez les résistances au sein des topologies suivantes, pour un courant ICo = 10 mA et en

prenant VBEo ≅ 0.6 V .

1. Polarisation simple (figure 1).

2. Polarisation par résistance entre collecteur et base (figure 2).

3. Polarisation avec résistance d’émetteur (figure 3).

4. Polarisation avec résistance d’émetteur et pont de base (figure 4).

Corrigé

Le point de repos étant placé sensiblement au milieu de la droite de charge statique dans les

caractéristiques de sortie, la tension VCEo ≅ VCC 2 = 10 V

1. Polarisation simple

+VCC ⎧VCC = RC IC + VCE

⎪

⎨VCC = RB I B + VBE

RB RC ⎪I = β I

⎩C B

IC

IB

VCE VCC − VCEo VCC − VBEo

⇒ RC = = 1 kΩ , RB = β = 291 kΩ

VBE IC o IC o

Sylvain Géronimi Page 21 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

2. Polarisation par résistance entre collecteur et base

+VCC ⎧VCC = RC (IC + I B ) + VCE

⎪

RC ⎨VCE − VBE = RB I B

⎪I = β I

RB

⎩C B

IC

IB

VCE VCC − VCEo β VCEo − VBEo

⇒ RC = ≅ 1 kΩ , R B = β = 141 kΩ

VBE IC o β +1 IC o

3. Polarisation avec résistance d’émetteur

+VCC ⎧VCC = VCE + RC IC + RE I E

⎪ VCC − VCEo

⎪VCC = RB I B + VBE + RE I E

RC ⎨ ⇒ RC ≅ − RE = 820 Ω ,

⎪I E = I B + IC

RB

IC o

IC

⎪I = β I

IB ⎩C B

VCE

VBE ⎛ VCC − VBEo ⎞

RB ≅ ⎜ − RE ⎟ β ≅ 264 kΩ

RE ⎜ IC o ⎟

⎝ ⎠

4. Polarisation avec résistance d’émetteur et pont de base

+VCC ⎧VB = RB I B + VBE + RE I E RB2

⎨ VB = VCC , RB = RB1 // RB2

⎩VCC = RC IC + VCE + RE I E RB1 + RB2

RB1 RC

IC

VCC − VCEo VBEo + RE ICo

IB RC ≅ − RE = 820 Ω , RB ≅ ≅ 18 kΩ ,

VB VCE IC o VCC ICo

−

VBE RB1 β

RB2 RE RB2 ≅ 22 kΩ

Sylvain Géronimi Page 22 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Stabilité du point de repos par résistance d’émetteur

L’étude porte sur le comportement du montage de la figure ci-dessous en fonction de la température.

RB1 RC

100k 1.5k

VCC

Q1 20 V

RB2 RE

470

Le transistor, de type 2N1711 ( β typique = 150 ), possède les caractéristiques constructeur

Ptot (TA ≤ 25 °C )max = 0.8 W , TJmax = 200 °C , RthJA = 220 °C /W , RthJB = 58 °C /W

Etude du régime continu

1. En supposant IB << IC et VBE << VCE , écrivez que la puissance Pd dissipée dans le transistor,

satisfait à la condition dPd dIC = 0 et déduisez le point de repos correspondant et la valeur de la

résistance RB 2 nécessaire pour polariser correctement le transistor ( VBE0 ≅ 0.6 V ).

2. En prenant comme valeur de température ambiante TA = 25 °C , calculez la température TJ de la

jonction.

Stabilité en température

3. Dans le cas général, écrivez IC = [β (T ),VBE (T ),ICBO (T )] .

4. Déduisez les facteurs de stabilité SI = ∂IC ∂ICBO , SV = ∂IC ∂VBE , S β = ∂IC ∂β .

5. Evaluez dans le cas du montage dIC dT et dVCE dT sachant que, pour le silicium, le fabricant

indique dVBE dT ≅ − 2.5 mV / °C , dβ (β dT ) ≅ 0.5 % / °C , dICBO (ICBO dT ) ≅ 11 % / °C et

ICBO = 1 nA à 25 °C .

Corrigé

Etude du régime continu

1. Expression de la puissance dissipée

+VCC

⎧VB = RB I B + VBE + RE I E

⎪

⎪VCC = RC IC + VCE + RE I E

RB1 RC

⎨

IC ⎪I E = I B + IC

⎪IC = α I E + ICBO

VB

IB

VCE

⎩

RB2

VBE avec VB = VCC , RB = RB1 // RB2

RB2 RE

RB1 + RB2

Sylvain Géronimi Page 23 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

et ICBO courant de fuite de la jonction base-collecteur polarisée en inverse (dérive thermique).

Les deux jonctions présentées par le transistor produisent une résistance au passage des

courants, d’où une puissance dissipée en chaleur. La traversée du courant IC à travers la jonction

base-collecteur, aux bornes de laquelle existe la tension VCB , produit une dissipation de

puissance égale à VCB IC . De la même façon, la puissance dissipée dans la jonction base-

émetteur vaut VBE I E . La puissance dissipée dans le transistor s’écrit

Pd = VBE I E + VCB IC = VBE I B + (VCB + VBE )IC = VBE I B + VCE IC ≅ VCE IC car IB << IC et VBE << VCE .

La puissance transformée en chaleur dans le transistor est presque intégralement dissipée par la

jonction base-collecteur dont le courant de fuite ICBO varie en fonction de la température.

En considérant que I E ≅ IC ( β >> 1 ) dans l’équation de la maille de sortie,

Pd ≅ IC [VCC − (RC + RE )IC ] d’où = 0 ⇒ VCC = 2 (RC + RE )IC

dPd

dIC

cinquième équation du système linéaire dont les cinq inconnues sont I B , IC , I E , VCE , RB2 .

La puissance dissipée passe par un maximum au point de repos (fonction parabolique)

VCC V

IC o ≅ ≅ 5 mA et VCEo ≅ VCC − (RC + RE ) ICo = CC = 10 V .

2 (RC + RE ) 2

Ces expressions, respectivement ordonnée et abscisse du point de repos dans le plan de sortie

du transistor, montrent une polarisation en classe A (au milieu de la droite de charge statique). En

ce point, il y a le meilleur effet de stabilisation possible du courant collecteur en fonction de la

température. En effet, à une variation de IC correspond une variation minimale de Pd (sommet

de la parabole). Il paraît donc souhaitable de polariser le transistor au milieu de la droite de

charge à condition, bien sur, de pouvoir dissiper la puissance maximale

2

VCC

Pdmax = ≅ 50 mW (<< 800 mW).

4 (RC + RE )

En considérant I E ≅ IC , la maille d’entrée s’écrit

RB I VBE o + RE ICo

VCC ≅ RB C + VBE + RE IC ⇒ RB ≅ ≅ 18 kΩ et RB2 ≅ 22 kΩ .

RB1 β VCC ICo

−

RB1 β

2. Calcul de la température TJ

La puissance maximale que peut dissiper un transistor, pour une température ambiante

déterminée, est une constante qui dépend des dimensions géométriques du transistor

TJ − TA

Pd = (approche linéaire)

RthJA

avec TJ température de la jonction ( TJmax = 200 °C ), TA température ambiante ( TA = 25 °C ),

RthJA résistance thermique jonction-ambiant ( RthJA = 220 °C /W ).

TJmax − TA

A remarquer que la formule satisfait les données constructeur Ptotmax = ≅ 0 .8 W .

RthJA

La température de la jonction vaut TJ = T A + RthJA Pd = 36 °C .

Sylvain Géronimi Page 24 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Il est possible d’avoir une approche de la température du boîtier TB en considérant la résistance

thermique jonction-boîtier ( RthJB = 58 °C /W ), soit TB = TJ − RthJB Pd ≅ 33 °C .

L’utilisation d’un radiateur permettrait d’augmenter le pouvoir de dissipation du transistor,

TJ − TA

Pd =

RthJB + RthBR + RthRA

avec RthBR résistance thermique boîtier-radiateur, RthRA résistance thermique radiateur-ambiant.

La somme des résistances thermiques serait alors de valeur plus faible que la résistance

thermique RthJA du transistor seul.

Stabilité en température

3. Expression de IC (β ,VBE , ICBO )

⎧VB = RB I B + VBE + RE I E

⎪ ⎧VB = (RB + RE )I E + VBE − RB IC

⎪ β ⎪

⎨IC = I E + ICBO ⇒ ⎨ β

⎪ β +1 ⎪IC = β + 1 I E + ICBO

⎪⎩I E = I B + IC ⎩

⇒ IC =

(RE + RB )(β + 1)ICBO + β (VB − VBE )

RB + (β + 1)RE

Le courant collecteur est fonction d’un ensemble de variables physiques dépendantes de la

température

4. Calcul des facteurs de stabilité

Ces facteurs sont les mesures de la stabilité de la polarisation du transistor. Ils sont définis

comme le rapport d’une variation ∆ IC du courant collecteur due à une variation de température, à

la variation correspondante d’une des fonctions suivantes ICBO (T ) , VBE (T ) , β (T ) , les autres

variations étant nulles, d’où ∆ IC = SI ∆ ICBO + SV ∆VBE + S β ∆ β .

Pour des variations suffisamment faibles des variables fonctions de la température, la relation au

∂IC ∂I ∂I

premier ordre est utilisée dIC = dICBO + C dVBE + C dβ .

∂ICBO ∂VBE ∂β

Il faut souligner que cette approche mathématique par les dérivées partielles est une approche

linéaire de phénomènes fortement non linéaires. Les facteurs s’écrivent alors :

⎡ ∂I ⎤

SI = ⎢ C ⎥ =

dIC

=

(β + 1)(RB + RE ) , S = ⎡ ∂IC ⎤ =

dIC

=−

β

⎢ ⎥ ,

RB + (β + 1)RE RB + (β + 1)RE

V

⎣ ∂ICBO ⎦VβBE =cte

=cte

dICBO ⎣ ∂VBE ⎦ IβCBO = cte

=cte

dVBE

⎡ ∂I ⎤

Sβ = ⎢ C ⎥

dI

= C =

(RB + RE ) ICo − ICBO ≅ SI I

⎣ ∂β ⎦VICBO==cte dβ RB + (β + 1)RE β β (β + 1) o

C

cte

BE

Ces trois facteurs de stabilité du montage doivent simultanément avoir des valeurs les plus faibles

possibles. Les trois expressions ayant même dénominateur, on se contentera de rendre possible

l’inégalité suivante RB << (β + 1)RE où RB représente le pont de base et (β + 1)RE l’impédance

ramenée à l’entrée par la contre-réaction.

Sylvain Géronimi Page 25 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Deux cas extrêmes peuvent être envisagés :

1 IC

- montage base commune RB = 0 ⇒ SI = 1 , SV ≅ − , S β ≅ 2o

RE β

β IC o

- montage émetteur commun RE = 0 ⇒ SI = β + 1 , SV = − , Sβ ≅

RB β

Le pire cas correspond au montage émetteur commun qui est le plus souvent employé.

5. Dérive du point de repos

Ces facteurs de stabilité permettent de calculer les variations du point de polarisation quand la

température varie.

⎧ dIC dICBO dVBE dβ dICBO dVBE dβ

⎪ dT = SI dT + SV dT + S β dT = SI ICBO I + SV + Sβ β

⎪ CBO dT dT β dT

⎨

⎪ CE ≅ − (R + R ) C

dV dI

⎪⎩ dT C E

dT

⎧ dIC −9 −6 −6

⎪⎪ dT ≅ 3.45 10 + 4.24 10 + 5.16 10 ≅ 9.4 µA

d’où ⎨

⎪ dVCE ≅ − (R + R ) dIC ≅ − 19 mV / °C

⎪⎩ dT C E

dT

L’application numérique montre que l’influence du courant de fuite ICBO est négligeable à une

température raisonnable et que les variations sur VBE et β jouent un rôle fondamental. Sans

résistance d’émetteur, la dérive aurait été cinq fois plus importante.

En conclusion, la présence d’une résistance d’émetteur diminue la fluctuation du point de repos

dans le plan de sortie IC (VCE ) du transistor.

Sylvain Géronimi Page 26 Polarisation d’un transistor

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Etage déphaseur

L’étude porte sur la caractérisation du circuit de la figure ci-dessous. Le transistor est de type 2N1711

( β typique = 150 ). Le composant CG est un condensateur de liaison.

RB RC

1k

rg CG VCC

Q1 20 V

50

RE vS1

vG

1k vS2

Etude du régime continu

1. Calculez la valeur de la résistance RB nécessaire pour que la tension VCE 0 soit de 10 V

( VBE0 ≅ 0.6 V ).

Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Dessinez le schéma et évaluez le paramètre rbe du modèle du transistor ( rce = ∞ ).

3. Calculez les gains en tension A v1 = v s1 v g et A v 2 = v s2 v g .

4. Calculez la résistance d’entrée Z e du montage.

5. Calculez les résistances de sortie Z s1 et Z s2 correspondant respectivement aux signaux de sortie

v s1 et v s2 .

6. Concluez sur la dénomination du montage.

Sylvain Géronimi Page 27 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Corrigé

Etude du régime continu

1. Evaluation de la résistance RB

+VCC

RB RC

⎧VCC = RB I B + VBE + RE I E

⎪

IC ⎪VCC = RC IC + VCE + RE I E

⎨

IB

Q1 VCE ⎪I E = I B + IC

⎪I = β I

VBE

⎩C B

RE

système de 4 équations à 4 inconnues ( I B , IC , I E , RB )

En considérant I E ≅ IC ( β >> 1 ), le système se réduit à 2 équations à 2 inconnues ( IC , RB )

⎧ IC

⎪VCC ≅ RB + VBE + RE IC VCC − VCEo VCC − VBE o − RE ICo

⎨ β ⇒ IC o ≅ = 5 mA et RB ≅ β = 432 kΩ

⎪V ≅ (R + R )I + V RC + RE IC o

⎩ CC C E C CE

Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Schéma et évaluation du paramètre rbe

Aux fréquences moyennes, le condensateur de liaison est équivalent à un court-circuit.

rg rbe UT

βi rbe ≅ β = 750 Ω

i IC o

RB RC vs1

vg rce = ∞

RE vs2

3. Calcul des gains en tension

En constatant que rg << RB dans l’application du théorème de Thévenin, le système s’écrit :

[

⎧v g ≅ rg + rbe + (β + 1)RE i

⎪⎪

]

⎨v s1 = − β RC i

⎪

⎪⎩v s2 = (β + 1)RE i

vs

⇒ A v1 = 1 ≅ −

β RC vs

et A v 2 = 2 ≅

(β + 1)RE

vg rg + rbe + (β + 1)RE vg rg + rbe + (β + 1)RE

≅ − 1 et A v 2 ≅ + 1 , car (β + 1)RE >> rg + rbe .

RC

soit A v1 ≅ −

RE

Sylvain Géronimi Page 28 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

4. Calcul de la résistance d’entrée

Le dipôle représenté est équivalent à une résistance par application du théorème de Thévenin.

Les courants dynamiques existant dans le dipôle sont générés par le courant d’excitation entrant

i 0 , issu de la source de tension v 0 .

i0 i0

i1 rbe

βi

i

v0 RB v0 ze

RC

RE

⎧i 0 = i1 + i

⎪

= RB // [rbe + (β + 1)RE ] ≅ 112 kΩ

v v0 v0

⎨v 0 = RB i1 ⇒ i0 = 0 + d’où Z e =

⎪v = r i + (β + 1)R i R B r be + (β + 1)RB i0

⎩ 0 be B

Remarquons ici que la topologie du circuit présente des branches en parallèle, ce qui conduit à

écrire l’expression de la conductance du dipôle et non de sa résistance (topologie série). A la vue

du schéma, cela se vérifie par la présence de la résistance RB en parallèle sur la résistance du

transistor vue de sa base.

5. Calcul des résistances de sortie

Pour le calcul de la résistance vue entre collecteur et masse, le courant d’excitation i 0 ne peut

traverser la branche de résistance infinie que représente la source liée. Le circuit en amont ne

peut être excité et i = 0 ⇒ β i = 0 . La résistance du dipôle est donc Z s1 = RC .

i0

i=0 βi=0

rbe

RE RC

v0

RG RB

Pour le calcul de la résistance vue entre l’émetteur et la masse, la topologie du circuit présente

une mise en parallèle des branches. Trouver RE en parallèle aux autres branches apparaît

évident. De plus, RC est en série avec la résistance infinie de la source liée et, de ce fait, ne doit

pas figurer dans l’expression de Z s2 . La source indépendante v g étant éteinte dans le dipôle, le

courant d’excitation entrant i 0 peut atteindre la branche qui supporte rbe et la fraction de courant i

commande la source β i .

i0

i βi i1

rbe

RE

v0

rg RB RC

Sylvain Géronimi Page 29 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

⎧i 0 = i1 − (β + 1)i

⎪ i 1 β +1 rbe + rg // RB

⎨v 0 = RE i1 ⇒ 0 = + d’où Z s2 = RE // ≅ 5 .3 Ω

v 0 RE rbe + rg // RB β +1

⎩ 0 (

⎪v = − r + r // R i

be g B )

6. Conclusion

Les dipôles équivalents du montage sous forme Thévenin sont, d’une part en sortie collecteur,

une source de tension indépendante d’amplitude v g et de phase opposée à celle de l’entrée en

série avec une résistance Z s1 = 1 kΩ (pseudo-émetteur commun) et, d’autre part en sortie

émetteur, une source de tension indépendante d’amplitude v g et de même phase que celle de

l’entrée en série avec une résistance Z s2 ≅ 5.3 Ω (émetteur suiveur). Le montage déphaseur de

tension propose deux dipôles pour attaquer un éventuel montage suivant.

collecteur émetteur

Zs1 Zs2

vg vs1 vg vs2

L’amplificateur de tension peut être représenté sous la forme d’un quadripôle faisant apparaître un

modèle utilisant une source contrôlée de tension, associée à une branche contrôlante supportant

la résistance d’entrée (voir cours « La caractérisation d’un amplificateur linéaire ».

collecteur émetteur

rg Zs1 rg zs2

50 1k 50 5.3

Ze ze

ve vs1 ve vs2

112k 112k

vg vg

A v1 ve A v2 ve

Ze

avec v e = v g ≅ v g car Ze >> rg

Z e + rg

⇒ v s1 = A v 1v g ≅ A v 1v e ≅ − v e et v s2 = A v 2 v g ≅ A v 2 v e ≅ + v e

Sylvain Géronimi Page 30 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Etage source commune

L’étude porte sur la caractérisation du circuit de la figure ci-dessous sous la forme d’un dipôle et d’un

quadripôle. Le transistor à effet de champ possède les caractéristiques I DSS = 15 mA, VP = −6 V .

La résistance Rch représente la charge extérieure de l’étage. Les condensateurs ont une fonction de

liaison (couplage).

RD

2k CL

rg CG J1 VCC

30 V

50 Rch

8k

R RS

vG 100k 300 CS

Etude du régime continu

1. Déterminez les points de fonctionnement du transistor.

Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Dessinez le schéma et évaluez le paramètre g m du modèle du transistor ( rds = ∞ ).

3. Calculez la résistance d’entrée Z e vue par le dipôle d’attaque ( v g , rg ).

4. Ecrivez les expressions des éléments du dipôle de Thévenin ( v s0 , Z s ) du montage attaquant la

charge Rch .

5. Identifiez les éléments du quadripôle représentatif de l’amplificateur de tension, attaqué par le

dipôle d’attaque et chargé par Rch .

6. Evaluez le transfert en tension v s v g .

Corrigé

Etude du régime continu

1. Calcul des points de fonctionnement

En continu ( ω = 0 ), les condensateurs de liaison sont équivalents à des circuits ouverts

1

( = ∞ ).

Cω

+VCC

⎧VCC ≅ (RD + RS )I D + VDS

RD ⎪ 2

ID ⎪ ⎛ VGS ⎞

⎨D

I = I ⎜

DSS ⎜ 1 − ⎟

IG=0

VDS ⎪ ⎝ VP ⎟⎠

⎪V ≅ − R I

VGS ⎩ GS S D

R RS

système de 3 équations à 3 inconnues ( I D , VDS , VGS )

Sylvain Géronimi Page 31 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

2

VGS ⎛ 1 2 ⎞

+ ⎜⎜ − ⎟VGS + 1 = 0 ⇒ VGS ≅ − 2 V et I D ≅ 6.67 mA , VDS ≅ 14.7 V .

⎟

VP2 ⎝ DSS S

I R VP ⎠

o o o

Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Schéma et évaluation du paramètre g m

Aux fréquences moyennes, les condensateurs de liaison sont équivalents à des courts-circuits.

2

rg

vgs

gm = − I DSS I Do ≅ 3.33 mA / V

vs VP

R gm vgs RD Rch

(canal N)

vg

3. Calcul de la résistance d’entrée vue par l’attaque

Le dipôle contient tout le circuit (y compris la

i0

G charge). La résistance d’entrée vue de la grille

du JFET étant de valeur énorme (jonction en

v0 R

inverse), le courant d’excitation i 0 du dipôle se

dirige entièrement dans la résistance R.

Z e = R = 100 kΩ

4. Dipôle de Thévenin

Calcul de Z s vue par la charge Rch

i0

Le courant i 0 , issu de la source de tension v 0

extérieure appliquée au dipôle, est l’unique

rg vgs = 0 gm vgs courant d’excitation du circuit puisque v g = 0

=0

R RD v0 (source éteinte). Il n’y a donc aucune possibilité

vg = 0 d’atteindre la partie amont du circuit et v gs = 0 .

ZS = RD = 2 kΩ

La tension à vide, appelée v s0 , se calcule en déconnectant la charge.

⎧ R

⎪v gs = R + r v g R

⎨ g ⇒ v s0 = − g m RD vg

⎪v = − g v R R + rg

⎩ s0 m gs D

La tension de sortie en charge est

RD

vs Rch

v s0 = − g m (RD // Rch )

Rch R

vs = vg

vs0 Rch + RD R + rg

Sylvain Géronimi Page 32 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

5. Quadripôle représentatif de l’amplificateur de tension

L’amplificateur de tension peut être représenté sous la forme d’un quadripôle faisant apparaître un

modèle utilisant une source contrôlée de tension, associée à une branche contrôlante supportant

la résistance d’entrée (voir cours « La caractérisation d’un amplificateur linéaire ».

rg RD

ve R vs Rch

vg

A v ve

La branche d’entrée s’identifie à Z e = R . Le dipôle de sortie s’identifie au dipôle de Thévenin

attaquant la charge dont les éléments sont ZS = RD et A v v e . Le transfert en tension A v est le

coefficient de proportionnalité de la variable de commande v e tel que

R

Av v e = Av v g = v s0 ⇒ A v = − g m R D

R + rg

6. Evaluation du transfert en tension

L’expression analytique de la tension de sortie en charge est :

A v v e = − g m (RD // Rch )

Rch R v

vs = v g ⇒ s ≅ − 5.33

Rch + RD R + rg vg

(même expression que pour le dipôle, évidemment).

Sylvain Géronimi Page 33 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Etage collecteur commun chargé par un miroir de courant

L’étude porte sur la caractérisation du circuit de la figure ci-dessous (résistance d’entrée, résistance

de sortie, transfert en tension, fréquence de coupure basse).

Les transistors sont tous identiques tels que β = 100 ( β >> 1), VBE0 = 0.6 V , rce = 100 kΩ . Le

composant C est un condensateur de liaison.

RB

C R

Q1

VCC

ve 10 V

Q2 Q3

vs

Etude du régime continu

1. Evaluez la résistance R pour que la source de courant produise I E1 = 1 mA . ainsi que la résistance

RB pour avoir VCE2 = 0.6 V .

Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Dessinez le schéma et évaluez le paramètre rbe du modèle du transistor Q1 .

3. Calculez le transfert en tension A V = v s v e . la résistance d’entrée Z e et la résistance de sortie

Zs .

Etude du régime dynamique faibles signaux aux fréquences basses

4. Evaluez la capacité de liaison afin d’obtenir une fréquence de coupure de l’ordre du hertz.

Sylvain Géronimi Page 34 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Corrigé

Etude du régime continu

IR

RB

R

Q1

VCC

IB1

IE1

Q2 Q3

1. Evaluation des résistances

Les composants Q2 , Q3 et R constituent un miroir élémentaire qui reconduit le courant I R en

sortie de Q2 .

⎧⎪VCC = R I R + VBE3 VCC − VBEo

⎨ ⇒ R≅ = 9 .4 k Ω

⎪⎩I R ≅ I E1 I E1

Evaluation de la résistance RB

⎧⎪VCC = RB I B1 + VBE1 + VCE2 VCC − VBEo − VCE2

⎨ ⇒ RB ≅ β = 880 kΩ

⎪⎩I E1 ≅ IC1 = β I B1 ( β >> 1) I E1

Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Schéma et évaluation du paramètre du modèle

Aux fréquences moyennes, le condensateur de liaison est équivalent à un court-circuit.

ie i

rbe1 UT

rbe1 ≅ β = 2 .5 kΩ

βi IC1

RB req vs

ve rce

req = rce1 // rce2 = = 50 kΩ .

2

3. Caractérisation de l’étage

Calcul du gain en tension

[

⎧⎪v e ≅ rbe1 + (β + 1)req i] vs (β + 1)req

⎨ ⇒ Av = = ≅ 1.

⎪⎩v s = (β + 1)req i v e rbe1 + (β + 1)req

Sylvain Géronimi Page 35 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Calcul de la résistance d’entrée

Le dipôle représenté est équivalent à une résistance par application du théorème de Thévenin.

Les courants dynamiques existant dans le dipôle sont générés par le courant d’excitation entrant

i 0 , issu de la source de tension v 0 .

i0 i i0

i1 rbe1

βi

RB req v0 ze

v0

⎧i 0 = i1 + i

⎪ v v0

⎨v 0 = RB i1 ⇒ i0 = 0 +

⎪v = r i + (β + 1)r i R B r be1 + (β + 1)req

⎩ 0 be1 eq

d’où Z e =

v0

i0

[

= RB // rbe + (β + 1)req ≅ 750 kΩ ]

Calcul de la résistance de sortie

i i0

rbe1 i1

βi

RB req

ve = 0

v0

La source indépendante v e étant éteinte dans le dipôle, le courant d’excitation entrant i 0 peut

atteindre la branche qui supporte rbe1 et la fraction de courant i commande la source β i .

⎧i 0 = i1 − (β + 1)i

⎪⎪ i 1 β +1 rbe1 rbe

⎨v 0 = req i1 ⇒ 0 = + d’où Z s = req // ≅ 1 = 25 Ω .

⎪ v 0 req rbe1 β +1 β

⎩⎪v 0 = − rbe1 i

Etude du régime dynamique faibles signaux aux fréquences basses

4. Calcul de la capacité

Constatons que le montage représente une simple résistance s’identifiant à la résistance d’entrée.

ve 1

Ze fb = ⇒ C ≅ 212 nF avec fb = 1 Hz .

2π Z e C

Sylvain Géronimi Page 36 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Etage différentiel à JBT

L’étude porte sur la caractérisation de l’étage différentiel de la figure ci-dessous. Les deux transistors

sont supposés technologiquement identiques avec β = 200, VA très grand .

RC RC

VCC

S1 15 V

Q1 Q2

V1 V2 VCC

RE 15 V

Etude du régime continu

1. Démontrez que les courants collecteurs des transistors sont égaux.

2. En prenant I 0 = 200 µA , évaluez la résistance RE .

Etude du régime dynamique faibles signaux aux fréquences moyennes

3. Evaluez les paramètres rbe1 et rbe2 des modèles des transistors.

4. Exprimez la tension de sortie sous la forme v s1 = Ad (v 1 − v 2 ) + Ac (v 1 + v 2 ) 2 .

5. Evaluer RC pour avoir Ad = −100 , puis calculez le taux de réjection de mode commun TRMC .

6. Calculez la valeur de l’impédance d’entrée différentielle Z d .

7. Calculez la valeur de l’impédance d’entrée de mode commun Z c .

La résistance RE est remplacée par un miroir de courant élémentaire Q3 - Q4 avec VA = 100 V (voir

problème « miroir élémentaire pour polarisation d’étage », la polarisation étant directement

compatible.

8. Evaluez le nouveau taux de réjection de mode commun.

Sylvain Géronimi Page 37 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Corrigé

Etude du régime continu

RC RC

VCC

IC1 IC2 15 V

Q1 Q2

VBE1 VBE2 VCC

RE 15 V

I0

1. Relation des courants collecteurs

⎧ VBE1

⎪I ≅ I e UT

⎪B BS

Equations technologiques Q1 ≡ Q2 ⇒ ⎨ 1

VBE2

⎪

⎪I B2 ≅ I BS e UT

⎩

Equation de la maille d’entrée VBE1 = VBE 2 ⇒ IC1 ≅ IC2

2. Evaluation de la résistance RE

I0 VCC − VBE1

IC1 = IC1 = ICo ≅ = 100 µA et RE = o

≅ 72 kΩ

o o 2 I0

Etude du régime dynamique faibles signaux aux fréquences moyennes

vs1 RC RC

Q1 Q2

v1 v2

RE

ie1 + ie2

3. Evaluation des paramètres des modèles rbe1 et rbe2

UT

rbe = rbe1 = rbe2 = β = 50 kΩ

IC0

4. Expression de la tension de sortie

Méthode classique

(voir cours « Montages à plusieurs transistors »)

Sylvain Géronimi Page 38 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Méthode du demi-schéma (voir annexe sur « Méthode de travail pour la caractérisation linéaire

d’un étage différentiel »)

vs1 RC RC vs1 RC RC vd

v1 = + vc

ie1 = - ie2 ie1 = ie2 2

Q1 Q2 Q1 Q2 v

v2 = − d + vc

vd / 2 - vd / 2 vc vc 2

masse

RE virtuelle RE

0 ie1 + ie2 = 2 ie

Pour le régime différentiel, le montage (parfaitement symétrique) se réduit au montage émetteur

commun de gauche, les tensions d’émetteur et de masse étant équipotentielles puisque la

résistance RE est traversée par un courant nul. La tension de sortie v s1 est à gauche :

β RC v d

v s1 = −

rbe1 2

Pour le régime de mode commun, le montage se réduit au montage pseudo-émetteur commun,

l’émetteur de Q1 voyant une résistance équivalente 2 RE traversée par son courant d’émetteur :

β RC

v s1 = − vc

rbe1 + 2 (β + 1)RE

β RC β RC

Le théorème de superposition donne v s1 = − vd − vc

2 rbe1 rbe1 + 2 (β + 1)RE

v s1 β RC v s1 β RC

On identifie Ad = =− et Ac = =−

vd 2 rbe1 vc rbe1 + 2 (β + 1)RE

5. Evaluation de la résistance RC et du taux de réjection TRMC

2 rbe Ad 1

= + (β + 1) E ≅ 289 (49.2 dB)

Ad R

RC = − = 50 kΩ , TRMC =

β Ac 2 rbe1

6. Evaluation de la résistance différentielle Z d

Z d = rbe1 + rbe2 = 100 kΩ (résistance inter-bases, vue par la tension différentielle d’entrée)

7. Evaluation de la résistance de mode commun Z c

Z c = rbe1 + 2 (β + 1)RE ≅ 29 MΩ (résistance entre base et masse, vue par la tension de mode

commun d’entrée pour le demi-schéma)

La source v c voit à ses bornes une résistance Z c 2

8. Evaluation du nouveau taux de réjection TRMC

VA

La charge dynamique du miroir rce3,4 ≅ = 500 kΩ remplace la résistance RE = 72 kΩ , ce qui

I0

améliore les performances de l’étage différentiel ( TRMC ≅ 66 dB , Z c ≅ 201 MΩ )

Sylvain Géronimi Page 39 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Etage différentiel à JFET

L’étude porte sur la caractérisation de l’étage différentiel de la figure ci-dessous. Les deux transistors

sont supposés technologiquement identiques avec I DSS = 2 mA, VP = − 2 V .

+VCC +VCC

RD RD

vs

10k 10k

J1 J2

v1 v2

I0

J3

RS

500

-VCC

Etude en régime continu

1. Evaluez les courants de drain des transistors.

Etude du régime dynamique faibles signaux aux fréquences moyennes

2. Déduisez de l’étude du régime continu, les valeurs des paramètres g mi des transistors J i .

3. Ecrivez l’expression de la résistance dynamique z0 de la source de courant I 0 vue entre le drain

et la masse. Evaluez cette dernière, le paramètre rds3 étant estimé à 100 kΩ.

4. Les paramètres rds des transistors J1 et J 2 étant négligés, écrivez puis évaluez les gains en

vs v

tension Ad = et Ac = s .

vd vc

5. Déduisez le TRMC en dB.

6. Evaluez les résistances différentielle Z d , de mode commun Z c et de sortie Z s du montage.

Sylvain Géronimi Page 40 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Corrigé

Etude du régime continu

+VCC +VCC

RD RD

10k 10k

ID1 ID2

J1 J2

0 VGS1 VGS2 0

I0

J3

VGS3

RS

0 500

-VCC

1. Evaluation des courants de drain des transistors

⎧ ⎛ VGS1 ⎞

2

⎪I = I ⎜ ⎟

DSS ⎜ 1 −

⎪ D1

⎝ Vp ⎟⎠

⎪

⎪ ⎛ VGS2 ⎞

2

⎪ ⎜ ⎟

Equations technologiques ( J1 ≡ J 2 ≡ J 3 ) ⎨I D2 = I DSS ⎜1 − (mêmes I DSS , VP )

⎪ ⎝ Vp ⎟⎠

⎪ 2

⎪ ⎛ VGS3 ⎞

⎜

⎪I D3 = I DSS ⎜1 − ⎟

⎪⎩ ⎝ Vp ⎟⎠

⎧I 0 ≡ I D = I D + I D

⎪⎪ 3 1 2

Equations du circuit ⎨VGS1 −VGS2 = 0

⎪

⎪⎩VGS3 = − RS I 0

⎧ I0

⎪I D1 = I D2 = 2

⎪ R2 ⎛ 2 RS 1 ⎞

d’où ⎨ 2 ⇒ S2 I 02 + ⎜ − ⎟ I0 + 1 = 0

⎛ ⎞ ⎜ ⎟

⎪I = I ⎜ RS I 0 ⎟ Vp ⎝ Vp I DSS ⎠

⎪0 DSS ⎜1 + ⎟

⎝ V p ⎠

⎩

soit I 0 ≅ 1.07 mA, I D1 = I D2 ≅ 536 µA

o o

2. Evaluation des paramètres g mi

2

gm = − I Do I DSS , g m1 = g m2 ≅ 1.035 mA / V , g m3 ≅ 1.46 mA / V

Vp

Sylvain Géronimi Page 41 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

3. Calcul de la charge dynamique

i0

⎧⎪v 0 = rds3 (i 0 − g m3 v gs ) + RS i 0

rds3 ⎨

⎪⎩v gs = − RS i 0

i0 - gm vgs gm vgs

v

0

RS vgs

⇒ z0 =

v0

i0

( )

= RS + 1 + g m3 RS rds3 ≅ 173 kΩ

4. Expression de la tension de sortie

La méthode du demi-schéma est mise en œuvre (voir annexe sur « Méthode de travail pour la

caractérisation linéaire d’un étage différentiel symétrique»).

G1 S1 S2 G2

vgs1 vgs2

gm vgs1 z0 gm vgs2 vd / 2

vd / 2

D1 D2

vc vc

RD RD vs

Pour le régime différentiel, le montage se réduit au montage source commune, car la charge z0

est traversée par un courant nul et la tension de sortie v s est à droite, d’où

⎛ v ⎞ v g R

v s = − g m RD ⎜ − d ⎟ d’où le gain différentiel Ad = s = m D ≅ 5.18 .

⎝ 2 ⎠ v d 2

Pour le régime de mode commun, le montage se réduit au montage pseudo-source commune, la

source de J 2 voyant une charge équivalente 2 z0 traversée par son courant de source, d’où

g m RD vs g m RD

vs = − vc d’où le gain de mode commun Ac = =− ≅ − 29 10 −3 .

1+ 2 g m z0 vc 1 + 2 g m z0

Le théorème de superposition donne v s = Ad v d + Ac v c .

5. Evaluation du TRMC

Ad 1

TRMC = = + g m z0 ≅ 180 (45 dB)

Ac 2

6. Calcul des résistances différentielle, de mode commun et de sortie du montage

Z d = ∞ , Z c = ∞ , Z s = RD = 10 kΩ

Sylvain Géronimi Page 42 Caractérisation d’un amplificateur linéaire

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Réponse en fréquence d’un étage émetteur commun

L’étude proposée porte sur le comportement en fréquence du montage de la figure ci-dessous. Le

transistor possède les caractéristiques suivantes

β = 150, ft = 70 MHz,Cbc = 20 pF , VA = ∞

Les composants CG et CE sont respectivement des condensateurs de liaison et de découplage.

RB1 RC

100k 1.5k

rg CG Q1 VCC

S

50 10u 20 V

RB2 RE CE

vG 22k 470 100u

Etude du régime continu

1. Déterminez le point de repos du transistor.

Etude du régime dynamique aux faibles signaux

2. Déduisez la valeur du paramètre rbe de l’étude précédente.

3. Aux fréquences moyennes, calculez le gain en tension Av o = v s v g , les résistances d’entrée et

de sortie.

4. Evaluez la fréquence de coupure basse du montage.

5. Evaluez la fréquence de coupure haute du montage.

Sylvain Géronimi Page 43 Réponse en fréquence

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Corrigé

Etude du régime continu

RC

RB1

IC

IB VCC

VCE

VBE

RB2 RE

IE

1. Point de repos du transistor

⎧VCC ≅ (RC + RE )IC + VCE RB2

⎨ avec VB = VCC et RB = RB1 // RB2

⎩VB = RB I B + VBE + RE I E RB1 + RB2

RB ≅ 18 kΩ , IC0 ≅ 5.07 mA

Etude du régime dynamique

2. Résistance dynamique de la jonction base-émetteur

UT

rbe ≅ β ≅ 740 Ω

IC 0

3. Gain en tension aux fréquences moyennes

rg β ib

rbe

RB RC vs

ib

vg

Ce schéma peut être simplifié au regard des valeurs numériques, car RB >> rg par Thévenin.

( )

⎧⎪v g ≅ rg + rbe i b v β RC

⎨ ⇒ Av o = s ≅ − ≅ − 285

⎪⎩v s = − β i b RC vg rg + rbe

soit un gain d’amplitude de 285 avec déphasage de π ou encore gain de 49 dB.

Les résistances d’entrée et de sortie s’écrivent : Z e = RB // rbe ≅ 711 Ω et Z s = RC ≅ 1.5 kΩ .

Sylvain Géronimi Page 44 Réponse en fréquence

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

4. Fréquence de coupure basse

Schéma aux fréquences basses

CG

rg rbe

RB ib β ib RC

vg

RE

CE

La fonction de transfert en tension est du type passe-haut du second ordre par la présence des

deux condensateurs indépendants au sein du montage.

Méthode classique de mise en équations

⎧ 1

⎪ω3 = R C

⎪ E E

⎛ p ⎞ P ⎪ RB + rbe + (β + 1)RE

⎪ω 4 =

⎜⎜1 +

⎝ ω

⎟⎟

3 ⎠ ω4 ⎪ R [

B rg + rbe RB + rg CG ( )]

Av ( p ) = Av o avec ⎨

2ζ ⎪ 2 ζ = r + R // [r + (β + 1)R ] C + ⎛⎜ R // rbe + RB ⎞

1+

ωn

p+

p2

ωn2 ⎪ ωn g { B be E G ⎜ E β +1

} ⎟⎟ CE

⎝ ⎠

⎪

⎪ 1 1 [

RB rg + rbe RB + rg CG RE CE ( )]

⎪ 2 =ω ω = RB + rbe + (β + 1)RE

⎩ ωn 3 4

Le calcul du coefficient d’amortissement ζ et de la pulsation naturelle ωn du système non amorti

permet l’évaluation de la fréquence de coupure à – 3 dB (voir cours « Le filtrage analogique »).

ωc = ωn 2 ζ 2 − 1 + ( 2 ζ 2 − 1)2 + 1 soit fc ≅ 327 Hz (filtre passe-haut du second ordre).

Méthode par l’approximation du pôle dominant

Calcul du premier pôle :

Résistance RG∞ du dipôle vu par CG lorsque CE est assimilé à un court-circuit.

RG∞

rg RB rbe RC

βi

i

RG∞ = rg + RB // rbe ≅ 761 Ω

Sylvain Géronimi Page 45 Réponse en fréquence

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Résistance RE∞ du dipôle vu par CE lorsque CG est assimilé à un court-circuit.

i0

rbe βi i i1

βi

i rbe

rg //RB RC

RE v0

RE RE∞ RC

rg //RB

⎧ v0

⎪i1 =

⎪ R

⎪

E

1 β +1 rg // RB + rbe

⎨i 0 = i1 − (β + 1)i

i0

⇒ = + d’où RE∞ = // RE ≅ 5.21 Ω

⎪ v0

v 0 RE rbe + rg // RB ( ) β +1

⎪− i =

⎪⎩ (

rbe + rg // RB )

1 ⎛ 1 1 ⎞

ce qui donne la fréquence de coupure à – 3 dB, fb ≅ ⎜ ⎟ ≅ 326 Hz .

2π ⎜ R∞ C + R∞ C ⎟

⎝ G G E E ⎠

Calcul du deuxième pôle :

Résistance RE0 du dipôle vu par CE lorsque CG est assimilé à un circuit ouvert.

Résistance RG0 du dipôle vu par CG lorsque CE est assimilé à un circuit ouvert.

RG0

rbe

βi

i

RB RC

rg

RE RE0

RB + rbe

RG0 = rg + RB // [rbe + (β + 1)RE ] ≅ 14440 Ω , RE0 = RE // ≅ 95.8 Ω

β +1

1

d’où f3 ≅ ≅ 1 Hz

2π (RG0 CG + RE0 CE )

Calcul du zéro :

Le zéro est produit par la liaison entre émetteur et masse, couplage dû à CE . En effet, si

l’émetteur du transistor est en l’air, le courant dans la charge est nul, donc

RE 1 1

=∞ ⇒ p=− et f2 = ≅ 3.39 Hz .

1 + RE C E p R E CE 2π RE CE

Les résultats sont valables avec une excellente précision car les deux pôles sont séparés de plus

de deux décades et le zéro est à deux décades en dessous du pôle dominant. La simulation sur

Spice confirme ces chiffres.

Sylvain Géronimi Page 46 Réponse en fréquence

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

5. Fréquence de coupure haute

IC 0

Estimation de la capacité de diffusion Cbe + Cbc = Cbc = 20 pF , Cbe ≅ 440 pF

2π UT ft

Schéma aux fréquences hautes

Cbc

rg

Cbe

RB v rbe gm v Rc vs

vg

La fonction de transfert en tension est du type passe-bas du second ordre par la présence des

deux capacités indépendantes au sein du montage.

Méthode classique de mise en équations

L’écriture de la fonction de transfert en tension est la suivante :

⎧ gm

⎪ω z =

⎛ p ⎞ ⎪ C

⎜⎜1 − ⎟ bc

ωZ ⎟⎠ ⎪⎪ 2 ζ

AV ( p ) = AVo ⎝

2ζ

avec ⎨ ( ) [ (

= rg // RB // rbe Cbe + RC + (1 + g m RC ) rg // RB // rbe Cb 'c )]

1+ p+

p2 ⎪ ωn

ωn ωn2 ⎪ 1

(

⎪ 2 = rg // RB // rbe RC Cbe Cbc )

⎪⎩ ω n

Le calcul du coefficient d’amortissement ζ et de la pulsation naturelle ωn du système non amorti

permet l’évaluation de la fréquence de coupure à – 3 dB (voir cours « Le filtrage analogique »).

ωc = ωn 1 − 2 ζ 2 + ( 2 ζ 2 − 1)2 + 1 soit fc ≅ 477 kHz (filtre passe-bas du second ordre).

Méthode par l’approximation du pôle dominant

Calcul du premier pôle :

0

Rbc

v 0

rg rbe R be RC

RB

gm v

Résistance du dipôle vu par C be lorsque Cbc est assimilé à un circuit ouvert :

0

Rbe = rg // RB // rbe ≅ 46.7 Ω

Sylvain Géronimi Page 47 Réponse en fréquence

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Résistance du dipôle vu par C bc lorsque Cbe est assimilé à un circuit ouvert :

0

Rbe

i0

v

gm v 0 i + R (i + g v )

⎧⎪v 0 = R be 0 C 0 m

v0 RC ⎨

⎪⎩v = R be

0 i

0

0

Rbc = (1 + g m RC )Rbe

0

+ RC ≅ 15730 Ω

1

0

a1 = Rbe 0

Cbe + Rbc Cbc ≅ 3.35 10 −7 s , fh ≅ ≅ 475 kHz ce qui donne la fréquence de coupure

2π a1

à - 3 dB.

Calcul du deuxième pôle :

Résistance Rbc

be du dipôle vu par C

bc lorsque C be est assimilé à un court-circuit :

be

Rbc

be = R = 1.5 kΩ

Rbc C

v=0 RC

gm v = 0

a1

a2 = Rbe

0 C R be C

bc ≅ 6.17 10

−16 s 2 , d’où f ≅

2 ≅ 86.5 MHz .

2π a2

be bc

Calcul du zéro :

Le zéro est produit de manière telle que le courant circulant dans la charge RC est nul, couplage

dû à Cbc . En effet, le courant circulant dans la branche supportant Cbc est égal au courant fourni

par la source liée, donc

g gm

Cbc p V ( p ) = g m V ( p ) ⇒ p = m et f3 = ≅ 1.6 GHz .

C bc 2π Cbc

Malgré que les calculs, conduisant à l’évaluation de f2 , outrepasse le domaine de validité du

modèle de comportement en fréquence du transistor ( f2 et f3 > ft ), la fréquence de coupure haute

demeure valable avec une bonne précision, car les deux pôles sont séparés de plus de deux

décades. L’hypothèse du pôle dominant est donc vérifiée à une précision inférieure à 1%.

Sur un plan purement analytique, une meilleure précision peut être atteinte en évaluant une

fréquence de coupure corrigée telle que

1 1 1 1 1 1

≅ 2π a1 = + ⇒ ≅ − d’où f1 = fhcorrigée ≅ 478 kHz en prenant la valeur trouvée de

fh f1 f 2 f1 fh f2

f2 (valeur approchée).

Sylvain Géronimi Page 48 Réponse en fréquence

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Méthode par transformation de schéma par application du théorème de Miller

Le schéma H.F. fait apparaître un quadripôle ponté par la branche capacitive C bc . Le théorème