Académique Documents

Professionnel Documents

Culture Documents

Logique

Transféré par

Achraf ElTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Logique

Transféré par

Achraf ElDroits d'auteur :

Formats disponibles

TD logique

Forme disjonctive normale

Pour la table suivante, donner l’expression des fonctions f1, f2, f3 et f4 et les circuits correspondants avec

des portes ET, OU et Inverseurs. Dans la table, le cas indifférent (0 ou 1) est noté d.

a b c f1 f2 f3 f4

0 0 0 1 1 d 0

0 0 1 1 1 1 1

0 1 0 0 1 0 1

0 1 1 0 1 1 d

1 0 0 1 0 d d

1 0 1 0 0 0 d

1 1 0 1 0 1 1

1 1 1 1 1 1 0

f1=a/b/+ab+ac/ ou ab+a/b/+b/c/

f2=a/+bc

f3=a/c+bc+ab ou a/c+bc+ac/

f4=bc/+a/c

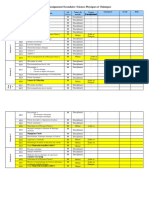

Afficher 7-segments

On veut réaliser un circuit de commande d’un afficheur 7-segments.

Les entrées du circuit sont e3e2e1e0e qui codent sur 4 bits les 10 chiffres décimaux de 0 à 9. Les sorties

sont les 7 segments a,b,c,d,e,f,g auxquels on associe une variable binaire.

On veut obtenir sur les 7-segments les 10 chiffres décimaux de 0 à 9. Donner les expressions de a à g en

fonction de e3e2e1e0e après simplification.

a

b f

g

c e

d

La table de vérité est la suivante :

ei a b c d e f g

0000 1 1 1 1 1 1

0001 1 1

0010 1 1 1 1 1

0011 1 1 1 1 1

0100 1 1 1 1

0101 1 1 1 1 1

0110 1 1 1 1 1 1

0111 1 1 1

1000 1 1 1 1 1 1 1

1001 1 1 1 1 1 1

Chiffres

0 : a,b,c,d,e,f

1 : e,f

2 : a,c,d,f,g

Solutions TD_logiques suplémentaires 1

3 : a,d,e,f,g

4 : b,e,f,g

5 : a,b,d,e,g

6 : a,b,c,d,e,g

7 : a,e,f

8 : a,b,c,d,e,f,g

9 : a,b,d,e,f,g

Segment : déterminer à partir des chiffres on regroupe les termes

a : 0,2,3,5,6,7,8,9

b : 0,4,5,6,8,9

c : 0,2,6,8

d : 0,2,3,5,6,8,9

e : 0,1,3,4,5,6,7,8,9

f : 0,1,2,3,4,7,8,9

g : 2,3,5,6,8,9

Expressiosn logiques déduites à partir de la table de vérité

a=e1/+e0e2+e0/e2/

b=e3+e2e1/+e2e0/+e1/e0/

c=e2/e0/+e1e0/

d=e3+e2/e1+e&e0/+e2e1/e0

e=e2+e1e0+e1/e0/

g=e1+e3e0/+e2e0

Comparateurs

Soit le comparateur 4 bits dont le schéma logique est donné ci-dessous. Il a 2 entrées A (a3a2a1a0) et B

(b3b2b1b0) et des entrées provenant d’un comparateur précédent que nous appelons A-1inf, a-1eg et A-

1sup. Il a 3 sorties que nous appelons ainf, Aeg et Asup qui traduisent le résultat de la comparaison

(Ainf=1 si A<B ...).

a3 b3 a2 b2 a1 b1 a0 b0

Comparateur 4 bits A-1inf

A-1eg

A-1sup

Ainf Aeg Asup

1. Donner les expressions logiques ai inf, ai eg et ai sup d’un comparateur 1 bit en fonction de ai et bi.

2. Donner les expressions logiques ai inf, ai eg et ai sup d’une tranche 1 bit d’un comparateur en

fonction de ai, bi et de l’étage précédent ai-1 inf, bi-1 sup, ou bi-1 sup.

3. Donner le schéma logique du comparateur 4 bits.

4. Donner le temps de retard exprimé en nombre de couches logiques pour le comparateur 4 bits réalisé

avec 4 tranches de 1 bit.

5. Même question avec un comparateur 8 bits, 16 bits. (Temps de retard : inverseur 1tp, ET 1tp, Ou 1tp,

(ai=bi) 3 tp).

6. Proposer d’autres versions des comparateurs 4 bits, 8 bits, 16 bits permettant de réduire le temps de

retard.

1) A partir de la table de vérité :

• ai inf=ai/bi

• ai eg=aibi+ai/bi/=(note ai=bi dans la suite)

ai sup= aibi/

Solutions TD_logiques suplémentaires 2

2) le resultat est inferieur si au rang i le resultat est inférieur ou bien si au rang i c’est

égale et qu’au rang i-1 le resultat est inférieur... même raisonnement pour les autres

• ai inf=ai/bi+(ai=bi).ai-1 inf

• ai eg=(ai=bi)ai-1 eg

• ai sup= aibi/+(ai=bi)ai-1 sup

3) Bonne chance.....

4)

• ai inf, ai sup=5 tp

• ai eg = 4tp

5) Comparateur N bits

N*5tp pour Ainf et Asup

N*4tp pour Aeg

6) principe / on propage les valeurs

Ainf= a3/b3 + (a3=b3) a2/b2 +(a3=b3) (a2=b2)a1/.b1 + (a3=b3)(a2=b2)(a1=b1)a0/b0

+(a3=b3)(a2=b2)(a1=b1)(a0=b0)A-1inf

Aeg=(a3=b3)(a2=b2)(a1=b1)(a0=b0)A-1eg

Asup= a3b3/ + (a3=b3) a2b2/ +(a3=b3) (a2=b2)a1.b1/ + (a3=b3)(a2=b2)(a1=b1)a0b0/

+(a3=b3)(a2=b2)(a1=b1)(a0=b0)A-1sup

Ainf, Asup en 5 tp

A eg en 4tp

Quelque soit N, mais avec des portes ET de N+1 entrées (problèmes de Fanin)

Conversion Binaire Gray

On rappelle ci-dessous la représentation en code binaire normal et en code de Gray des nombres de 0 à 15

Décimal Normal Gray

0 0000 0000

1 0001 0001

2 0010 0011

3 0011 0010

4 0100 0110

5 0101 0111

6 0110 0101

7 0111 0100

8 1000 1100

9 1001 1101

10 1010 1111

11 1011 1110

12 1100 1010

13 1101 1011

14 1110 1001

15 111 1000

On veut réaliser un convertisseur code normal-> code de gray.

Donner les expressions logiques des sorties S3, S2, S1, S0 en fonctions des entrées E3, E2, E1, E0 du

convertisseur. Les entrées sont en code normal, les sorties en code de gray. E3 correspond au poids fort,

E0 au poids faible.

S0=e1/e0+e1e0/

s1=e2e1/+e2/e1

Solutions TD_logiques suplémentaires 3

s2=e3e2/+e3/e2

s3=e3

Conversion 2 parmi 5

On veut réaliser le transcoder suivant : Du code DCB vers le code « 2 parmi 5 ». On donne les codes

suivants :

a b c d A B C D E

0 0 0 0 1 1 0 0 0

0 0 0 1 0 0 0 1 1

0 0 1 0 0 0 1 0 1

0 0 1 1 0 0 1 1 0

0 1 0 0 0 1 0 0 1

0 1 0 1 0 1 0 1 0

0 1 1 0 0 1 1 0 0

0 1 1 1 1 0 0 0 1

1 0 0 0 1 0 0 1 0

1 0 0 1 1 0 1 0 0

1. Exprimer A,B,C,D,E, en fonction de a,b,c,d.

2. Réaliser le câblage en utilisant uniquement des portes NAND et ou exclusif.

Additionneur

On veut fabriquer un additionneur de deux nombres binaires A et B tel que S soit leur somme.

Soit A=a3a2a1a0 et B=b3b2b1b0.

1) Etablir la table de vérité donnant les variations de Sn et Rn en fonction de an, bn et Rn-1.

2) En déduire l’expression de Rn et de Sn.

3) Donner les schémas des circuits logique donnant Sn et Rn à partir de Rn-1, an et bn.

Voir cours

Additionneur BCD

On veut réaliser un additionneur modulo 10 pour additionner deux chiffres BCD (décimal codé binaire).

L’addition modulo 10 de deux nombres A=A3A2A1A0 et B=B3B2B1B0 peut être réalisée en deux

étapes :

• Ajouter A et B (addition binaire)

• Si le résulta est supérieur où égal à 10 (base 10), ajouter 6(10) (il y a alors retenue pour l’étage

suivant), sinon ajouter 0. Ne pas tenir compte du débordement du 2ème étage additionneur.

On dispose d’additionneurs binaire 4 bits dont les entrées sont X et Y et la retenue d’entrée re. Les sorties

sont Z et la retenue de sortie rs.

Donner le schéma logique d’un additionneur BCD avec entrées A, B retenue d’entrée re, sorties S et

retenue de sortie rs à partir d’additionneurs binaires 4 bits et de portes ET et OU (ou mieux Nand).

La détection >=9 sur les sorties Zi du premier additionneur correspond aux cas

z3 z2 z1 z0

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

Solutions TD_logiques suplémentaires 4

0

re Z

AI

ET 0

S

OU

Bi ET

rs

rs r sortie

soit z3z1+z »z2 pour les sommes de 10 à 15, et la retenue de sortie=1 pour les sommes

16 à 19.

La retenue décimale de l’addition de deux chiffres BCD est donc

rs=rs1 (1er additionneur)+z3z2+z3z1

Le schéma de l’addionneur BCD en découle

Les entrées du deuxième additonneur sont z et 0 ou 6

si rs=0 et 6 si rs=1

Le choix 0 ou 6 s’obtient en entrant la configuration 0 rs rs 0 sur l’addionneur.

Soustracteur

Réaliser un étage soustracteur, à partir :

• De deux demi-soustracteur

• D’un demi additionneur et d’un demi soustracteur.

1/2 add

1/2sous

Problèmes

I) Une installation d’aspiration composée de 2 aspirateurs (A1,A2) est chargée de collecter les poussières

de 5 tubulures (vite le Robert). Chaque tubulure est mise en relation avec le système d’aspiration par une

électrovanne dont l’ordre de fermeture s’exécute par l’excitation Si de sa bobine (i de 1 à 5).

• Les conditions particulières de fonctionnement sont les suivantes :

• Le premier aspirateur fonctionne si une ou deux tubulures au maximum doivent être dépoussiérées.

• Le second aspirateur est mis en fonctionnement dans le cas où une ou deux autres tubulures au

maximum doivent être dépoussiérées. Ce qui signifie que les 2 aspirateurs ne peuvent collecter les

dépoussières que dans 4 tubulures en même temps.

• Le signal de verrouillage V est élaboré dés l’excitation de 4 électrovannes, afin d’éliminer le

fonctionnement de la 5ème.

On désire établir le schéma logique de la commande de fonctionnement des aspirateurs, et réaliser le

schéma logique du circuit qui fournit l’ordre de verrouillage V.

1. Préciser les variables logiques indépendantes d’entrées, ainsi que les différentes fonctions de sorties.

Définissez les états logiques de ces variables et fonctions.

2. Donner les expressions simplifiées des différentes fonctions de sorties (L’utilisation du tableau de

Karnaugh à 5 variables est équivalent à 2 tableaux de 4 variables).

3. Construire les schémas des circuits logiques réalisant les différentes fonctions de sorties définies en 2.

Solutions TD_logiques suplémentaires 5

A1 fonctionne si 1 ou 2 tubulures au max en service

A2 fonctionne si 1 ou 2 autres tubulures en service

Il faut donc 4 tubulures en tout.

A1 A2

E1 E2 E3 E4 E5

T1 T2 T3 T4 T5

Les variables d’entrées : Les electrovannes Ei

Les variables de sorties A1,A2,V

Ei = [ouvert 0,ferme 1], Ai = [ouvert 0,ferme 1], V = [non verouillé 0,verrouillage

1=>electrovanne ouverte].

On donne la table de vérité suivante :

E5 E4 E3 E2 E1 A1 A2 V

0 0 0

1 0 0

1 0 0

1 0 0

1 0 0

1 0 0

1 0 0

1 1 0

1 0 0

1 0 0

1 0 0

1 1 0

1 0 0

1 1 0

1 1 0

1 1 1

1 0 0

1 0 0

1 0 0

1 1 0

1 0 0

1 1 0

1 1 0

1 1 1

1 0 0

1 1 0

1 1 0

1 1 1

1 1 0

1 1 1

Solutions TD_logiques suplémentaires 6

1 1 1

x x 1

A1=E5+E4+E3+E2+E1 (X=1)

Pour déterminer A2, on peut faire 2 tableau de karnaugh en posant E5 et E5/

E5/

1

1 1 1

1

E5

1

1 1 1

1 1 X 1

1 1 1

Grâce aux deux groupements semblables, on élimine E5 pour un certains nombre de

monômes.

A2=E3E2E1+E4E2E1+E4E3E1+E4E3E2+E1E2E5+E3E4E5+E3E1E5+E4E1E5+E3E2

E5+E4E2E5

A2=E4E5(E1+E2+E3)+E3E1(E2+E4+E5)+E2(E4E1+E4E3+E1E5+E3E5)

V=E2E1(E3E4+E5E3+E1E2)+E4E5(E3E1+E3E2)

II) Soit F une fonction de quatre variables binaires a,b,c et d qui a pour expression

F=ab+a/b/c/d/+bcd/+a/b/cd+bc/d

1. Transformer F en somme logique de produits de quatre variables. On pourra utiliser un tableau de

Karnaugh.

2. On veut câbler cette fonction F à l’aide d’un multiplexeur du type 74151 (pour un nom...) comportant

8 entrées d’information (E0,E1, ... E7), 3 entrées d’adresse et une sortie S. Rappeler la forme générale

du signal de sortie S associé aux 8 entrées E0,E1, ... E7.

3. Les variables b,c,d de la fonction F sont choisies comme variables d’adresse. Identifier les termes

E0,E1, ...E7 et déterminer les signaux à appliquer aux 8 entrées du circuit. On résumera les données

du câblage sur un tableau donnant les adresses des entrées Ei et les signaux à y appliquer afin de

réaliser F.

4. Représenter le câblage symbolique de ce multiplexeur.

1) F=a/b/c/d/+a/b/cd+a/bcd/+abcd/+a/bc/d+abc/d+abcd+abc/d/+abc/d+abcd/

yo= a/b/c/d

y1= abc/

y2=

2)

C B A S

0 0 0 y0.c/b/a/

0 0 1 y1

0 1 0 y2

Solutions TD_logiques suplémentaires 7

0 1 1 y3

1 0 0 y4

1 0 1 y5

1 1 0 y6

1 1 1 y7.cba

S=A/B/C/y0+AB/C/y1+a/bc/y2+ac/y3+a/b/cy4+ab/cy5+a/bcy6+abcy7

3) câblage

On choisit comme variables d’adresse les variables b,c,d de la fonction F

S=B/C/D/Y0+BC/D/Y1+BCD/Y3+BC/DY5+B/CDY6+BCDY7

0

1

a

a/

b 0 1 2 3 4 5 6 7

c

d

Solutions TD_logiques suplémentaires 8

Vous aimerez peut-être aussi

- Correction Des TD 3 Decodage Et Multuplixage (SMP S6)Document21 pagesCorrection Des TD 3 Decodage Et Multuplixage (SMP S6)RABAB MASDOURPas encore d'évaluation

- Électronique NumeriqueDocument152 pagesÉlectronique NumeriqueSîdïMôhâmèdBënPas encore d'évaluation

- ch4 CircuitscombinatoiresDocument8 pagesch4 CircuitscombinatoiresKais BouzraraPas encore d'évaluation

- Corrig TD1 2Document5 pagesCorrig TD1 2Amine Aissaoui100% (1)

- TD1 Correction PDFDocument19 pagesTD1 Correction PDFAhmed LakhalPas encore d'évaluation

- UuuuDocument7 pagesUuuuissamtribiPas encore d'évaluation

- Ystemes Ogiques Ombinatoires: Xercice Ranscodeur Binaire Naturel Binaire ReflechiDocument4 pagesYstemes Ogiques Ombinatoires: Xercice Ranscodeur Binaire Naturel Binaire ReflechiYoussef Elfatihi100% (1)

- Fiche de TD 2Document4 pagesFiche de TD 2cedricPas encore d'évaluation

- Correction 4567Document6 pagesCorrection 4567gaaloul ghaithPas encore d'évaluation

- Archi ExamDocument3 pagesArchi Exammohanned.abbasPas encore d'évaluation

- Chapitre 2Document7 pagesChapitre 2Selma BouzertiniPas encore d'évaluation

- Polycopié - TP-Elect - SMP - S6-2023-2024Document25 pagesPolycopié - TP-Elect - SMP - S6-2023-2024azizaziz21212121212121Pas encore d'évaluation

- Cours Architecture Ordinateurs Chapitre2Document18 pagesCours Architecture Ordinateurs Chapitre2Kamer LovePas encore d'évaluation

- TD6 - Additionneur Comparateur DecodeurDocument2 pagesTD6 - Additionneur Comparateur DecodeurPhantom Tonton100% (1)

- Logique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Document37 pagesLogique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Soufiane El AoufiPas encore d'évaluation

- CC3 Computer&EssentialsDocument2 pagesCC3 Computer&EssentialsIvan NgandjuiPas encore d'évaluation

- 2016 17.TD - td1 4.sujet Copie - InfoDocument22 pages2016 17.TD - td1 4.sujet Copie - Infofifi foufouPas encore d'évaluation

- TP 1Document4 pagesTP 1Otmane El FaihPas encore d'évaluation

- Cours APM 01Document11 pagesCours APM 01Leroy Lionel SonfackPas encore d'évaluation

- Mi 1an13 Emd Structure - Machine2020 - 3Document2 pagesMi 1an13 Emd Structure - Machine2020 - 3Gaya MhbPas encore d'évaluation

- Numerique Serie 3Document3 pagesNumerique Serie 3Bilal EL MANSSOURIPas encore d'évaluation

- 2013-14 TD Cahier-Td InfoDocument16 pages2013-14 TD Cahier-Td InfoKorbous HfPas encore d'évaluation

- Techno Tle f2Document134 pagesTechno Tle f2Ange Dmi100% (2)

- 2019 2020 Rattrapage - SMI3Document4 pages2019 2020 Rattrapage - SMI3FadelPas encore d'évaluation

- Algébre de Boole Exrecice CorrigéDocument10 pagesAlgébre de Boole Exrecice CorrigéAhmat Sale100% (1)

- Devoir de Contrôle N°1 Corrigé Génie Mécanique 2008 2009 (Ben Aouicha)Document6 pagesDevoir de Contrôle N°1 Corrigé Génie Mécanique 2008 2009 (Ben Aouicha)Oumayma BoudaboussPas encore d'évaluation

- TD 32 Corrigé - Numération Et CodageDocument5 pagesTD 32 Corrigé - Numération Et Codagesoufiane8fka75% (4)

- (MATHS) Chapitre 1 - NumérationDocument5 pages(MATHS) Chapitre 1 - Numérationsio-montaPas encore d'évaluation

- Circuits Logiques Combinatoires - LicDocument29 pagesCircuits Logiques Combinatoires - LicHoucem B HsnPas encore d'évaluation

- NL CM9 PDFDocument11 pagesNL CM9 PDFCesar MalkiPas encore d'évaluation

- Archi Td3et4Document3 pagesArchi Td3et4Aychtu0% (1)

- Examen: Electronique Numérique Année Universitaire 2021 - 2022 Smi - S3Document9 pagesExamen: Electronique Numérique Année Universitaire 2021 - 2022 Smi - S3jarjinikhawla74Pas encore d'évaluation

- Corrige DecembreDocument4 pagesCorrige DecembreMalek AdelaPas encore d'évaluation

- TP01 PDFDocument11 pagesTP01 PDFMed Mohamed100% (1)

- Examen 2017Document9 pagesExamen 2017asma.rahmouniPas encore d'évaluation

- Intra Ele1300 A2012 CorrigeDocument13 pagesIntra Ele1300 A2012 CorrigeKIHEPas encore d'évaluation

- CRI - Chapitre 1Document11 pagesCRI - Chapitre 1Tinhinane Ait MessaoudPas encore d'évaluation

- TD1 Architecture-E+SDocument6 pagesTD1 Architecture-E+SZakaria TouyebPas encore d'évaluation

- 3ST 20082009Document23 pages3ST 20082009akremibechirPas encore d'évaluation

- FAHMI TPDocument10 pagesFAHMI TPINISSIRE FHDPas encore d'évaluation

- BooleDocument6 pagesBooleredPas encore d'évaluation

- Electronique Numerique Logique CombDocument24 pagesElectronique Numerique Logique CombKhalid SalmiPas encore d'évaluation

- ! Exercices - Logique-CombinatoireDocument10 pages! Exercices - Logique-CombinatoireTimo ShmittPas encore d'évaluation

- Architecture Des Ordinateurs TD1 - Portes Logiques Et Premiers CircuitsDocument13 pagesArchitecture Des Ordinateurs TD1 - Portes Logiques Et Premiers Circuitswafa wafaPas encore d'évaluation

- C3-Addition en BinaireDocument3 pagesC3-Addition en BinaireBASSILIST0% (1)

- TD3 ArchiDocument3 pagesTD3 ArchiDialloPas encore d'évaluation

- Chapitre2 Cours (Part. 2) Circuits Combinatoires PDFDocument47 pagesChapitre2 Cours (Part. 2) Circuits Combinatoires PDFabdesslem0jarrayPas encore d'évaluation

- Bai Tap KTS - 1 - Nguyen Ngo Lam - Huong DanDocument11 pagesBai Tap KTS - 1 - Nguyen Ngo Lam - Huong Danan Nguyễn ThànhPas encore d'évaluation

- TDN2 Electronique NumériqueDocument3 pagesTDN2 Electronique NumériqueybenguennyPas encore d'évaluation

- Chapitre 3 Circuits Logiques CombinatoiresDocument23 pagesChapitre 3 Circuits Logiques CombinatoiressoukainaPas encore d'évaluation

- Corrige JanvierDocument4 pagesCorrige JanviereugenedesuezPas encore d'évaluation

- 4 Etude Et Realisation D'un Circuit CombinatoireDocument15 pages4 Etude Et Realisation D'un Circuit CombinatoireReda Bou-abdallah100% (2)

- Affiche UrDocument5 pagesAffiche UrMohamed GountitiPas encore d'évaluation

- Travaux Pratiques Electronique Numérique I: Année Universitaire 2021/2022 Faculté Des Sciences Département de PhysiqueDocument25 pagesTravaux Pratiques Electronique Numérique I: Année Universitaire 2021/2022 Faculté Des Sciences Département de PhysiqueSimo GuemounPas encore d'évaluation

- Travaux Pratiques Electronique NumériqueDocument10 pagesTravaux Pratiques Electronique NumériqueOumaima RhayaPas encore d'évaluation

- Esi1an Lessons Archi-Algebre Boole SmahatDocument37 pagesEsi1an Lessons Archi-Algebre Boole SmahatN El kechaiPas encore d'évaluation

- J PortesDocument16 pagesJ PortesBOUCHEFFA HalimPas encore d'évaluation

- UntitledDocument25 pagesUntitledAchraf ElPas encore d'évaluation

- Equipement Du Laboratoire Check List FRDocument1 pageEquipement Du Laboratoire Check List FRAchraf ElPas encore d'évaluation

- RsersatzmaterialersatzteilefrDocument2 pagesRsersatzmaterialersatzteilefrAchraf ElPas encore d'évaluation

- Liste Du Materiel Disponible Sonorisation: FaçadeDocument1 pageListe Du Materiel Disponible Sonorisation: FaçadeAchraf ElPas encore d'évaluation

- Pret Audiovisuel Liste MaterielDocument2 pagesPret Audiovisuel Liste MaterielAchraf ElPas encore d'évaluation

- Materiel RestaurationDocument1 pageMateriel RestaurationAchraf ElPas encore d'évaluation

- CV Khalil Ridha-1Document1 pageCV Khalil Ridha-1Achraf ElPas encore d'évaluation

- PROCEDURE DE CANDIDATURE L2 L3 IUT Et MASTER 2021 2022 FRDocument3 pagesPROCEDURE DE CANDIDATURE L2 L3 IUT Et MASTER 2021 2022 FRAchraf ElPas encore d'évaluation

- Appel À Candidature Master ST-2022-2023Document1 pageAppel À Candidature Master ST-2022-2023Achraf ElPas encore d'évaluation

- Formulaire de Candidature A Une Bourse Niveau Master - Cap-Vert 2022-23Document3 pagesFormulaire de Candidature A Une Bourse Niveau Master - Cap-Vert 2022-23Achraf ElPas encore d'évaluation

- Fiche Tarifs 2021 2022 v1Document3 pagesFiche Tarifs 2021 2022 v1Achraf ElPas encore d'évaluation

- Modalites - Selection - Master - 2021 - 2022 - UaeDocument4 pagesModalites - Selection - Master - 2021 - 2022 - UaeAchraf ElPas encore d'évaluation

- Velo A Assistance ElectriqueDocument6 pagesVelo A Assistance ElectriqueAchraf ElPas encore d'évaluation

- Maquette LE Secondaire Physique - ChimieDocument2 pagesMaquette LE Secondaire Physique - ChimieAchraf ElPas encore d'évaluation

- Fiche Technique Qualité Du LogicielDocument3 pagesFiche Technique Qualité Du LogicielAchraf ElPas encore d'évaluation

- Fiche Technique Master CONSERVATION DE LA BIODIVERSITE MARINE - 0Document3 pagesFiche Technique Master CONSERVATION DE LA BIODIVERSITE MARINE - 0Achraf ElPas encore d'évaluation

- Fiche Technique Ingénierie InformatiqueDocument2 pagesFiche Technique Ingénierie InformatiqueAchraf ElPas encore d'évaluation

- Bureautique1 TsgeDocument180 pagesBureautique1 TsgemohcinechekkourPas encore d'évaluation

- 2700520300Document6 pages2700520300Daniel DefraeyPas encore d'évaluation

- ORACLE - Support de La Formation Oracle Database 11g DBA 1 (1Z0-052) - SSDocument347 pagesORACLE - Support de La Formation Oracle Database 11g DBA 1 (1Z0-052) - SSNguessan Kouadio100% (3)

- R061F1 1100D PJ PK NH & NJ Trop-Plein Élevé de L'injecteur-Pompe Électronique PDFDocument3 pagesR061F1 1100D PJ PK NH & NJ Trop-Plein Élevé de L'injecteur-Pompe Électronique PDFمهدي شقرونPas encore d'évaluation

- Branchement Digicode Sans Fil 10 Fonctions - FR - 7103 Branchement Digicode Sans Fil 10 FonctionsDocument12 pagesBranchement Digicode Sans Fil 10 Fonctions - FR - 7103 Branchement Digicode Sans Fil 10 FonctionsLoubetsPas encore d'évaluation

- AAmplificateur Diddérentiels Et D'instrumentationDocument22 pagesAAmplificateur Diddérentiels Et D'instrumentationaymane2002elfinouPas encore d'évaluation

- TP 2 CommandeDocument10 pagesTP 2 CommandeChicharito Oussama100% (1)

- Progression Techno TleF2 Et 3BTDocument2 pagesProgression Techno TleF2 Et 3BTGOUESSE ROMA SEIPas encore d'évaluation

- TP ORCAD Simulation Analogique Filtres PDocument13 pagesTP ORCAD Simulation Analogique Filtres PKAPAGNAN MOHAMED KONEPas encore d'évaluation

- Cours AsservissementDocument2 pagesCours AsservissementAsm MaPas encore d'évaluation

- Cours Securite Incendie Des BatimentsDocument17 pagesCours Securite Incendie Des BatimentsAchraf BoudayaPas encore d'évaluation

- Habinshuti JustinDocument1 pageHabinshuti Justinperspectives et organisationPas encore d'évaluation

- Guide System e Energie ElectriqueDocument143 pagesGuide System e Energie ElectriqueSikafouè Premier100% (2)

- TP1Document7 pagesTP1Maha BouattourPas encore d'évaluation

- Régulation PIDDocument33 pagesRégulation PIDRoboCEPT80% (5)

- SE Chapitre1 HARTI PDFDocument19 pagesSE Chapitre1 HARTI PDFmeryPas encore d'évaluation

- Support de Cours Téléphonie-Présenatation-Chapitre 1Document35 pagesSupport de Cours Téléphonie-Présenatation-Chapitre 1maîga100% (1)

- Icsv2 3008 T84 5008 T87 Not2551 Ind A 2Document13 pagesIcsv2 3008 T84 5008 T87 Not2551 Ind A 2Jose ManuelPas encore d'évaluation

- 8-jonctionPNDocument75 pages8-jonctionPNELAMRANIPas encore d'évaluation

- Téléphonie Mobile 2G 3G 4GDocument4 pagesTéléphonie Mobile 2G 3G 4GMED MOHPas encore d'évaluation

- Acquisition 2019Document66 pagesAcquisition 2019Mohamed OuaggaPas encore d'évaluation

- Electronique Informatique Embarquée Partie I II IV VDocument48 pagesElectronique Informatique Embarquée Partie I II IV Vmareme mbayePas encore d'évaluation

- TechniqueDocument8 pagesTechniqueFredj Kriaa100% (2)

- Code Secret NokiaDocument3 pagesCode Secret NokiajuniorPas encore d'évaluation

- 3.conversion D'un Signal Analogique en Signal Numérique PDFDocument5 pages3.conversion D'un Signal Analogique en Signal Numérique PDFkimmikPas encore d'évaluation

- Tarif Avril 2010Document46 pagesTarif Avril 2010btalalPas encore d'évaluation

- Devoir de Revision HediDocument5 pagesDevoir de Revision HediAmine AlaoUii AlaouiPas encore d'évaluation

- At Mega 32 AssembleurDocument102 pagesAt Mega 32 Assembleurdepset100% (1)

- TP 4 Réseau Triphasé en Couplage Étoile Sous Différentes ConditionsDocument11 pagesTP 4 Réseau Triphasé en Couplage Étoile Sous Différentes ConditionsMounaim MatiniPas encore d'évaluation

- 02-Synthese DissipateurDocument4 pages02-Synthese DissipateurBuen ChicoPas encore d'évaluation

- TP4 - Les Mux Et Les DemuxDocument7 pagesTP4 - Les Mux Et Les DemuxAloui Bechir0% (1)