Académique Documents

Professionnel Documents

Culture Documents

TD2 Architecture

Transféré par

mezghaniTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TD2 Architecture

Transféré par

mezghaniDroits d'auteur :

Formats disponibles

Module

: Architectures Avancées MREEA1

Travaux Dirigés N°2

Exercice 1 :

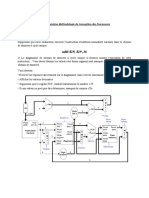

A/ Nous disposons d’un chemin de données monocycle MIPS (implémentant les

instructions de type R, ORI, lw, sw et beq)

Dans le chemin de données, le composant nommée GALU (Greater ALU) joue le rô le de

l’ALU mais possède de plus une sortie « Great » qui est égale à 1 si R[rs]-R[rt]>0 et 0 si

R[rs]=< R[rt]. Comme le cas de zéro, Great est un indicateur vers l’unité de

contrôle. C’est un indicateur de comparaison entre le contenu de deux registres

source et transfert.

1/ Etant donnée les latences d’exécution suivantes, donner le CPI et la durée du cycle de

l’horloge T1 pour l’implémentation de l’instruction lw sachant que :

Memory: 300ps | Banc de registres (READ/Write): 50ps | GALU et Adders: 100ps |

Portes logiques et multiplexeurs : 2ps | tout le reste est négligeable.

CPI =

T1 =

B/ Les concepteurs MIPS ont identifié des instructions supplémentaires que peut

réaliser le processeur MIPS (vu dans le cours). Ces instructions sont :

Instructions Description

cs $rd, $rs, $rt Le registre de destination rd reçoit le max (le

plus grand) suite à une comparaison entre le

contenu de rs et celui de rt

Dr Dhafer MEZGHANI Page 1

Module : Architectures Avancées MREEA1

cslw $rd, $rs, $rt Le registre de destination rd reçoit la donnée de

la mémoire de données dont son adresse est le

max suite à une comparaison entre le contenu

de rs et celui de rt

cslwcs $rd, $rs, $rt Le registre de destination rd reçoit le max suite

à une comparaison entre le contenu de rs et la

donnée générée par la mémoire de données

dont son adresse est déterminée aussi par le

maximum entre le contenu de rs et celui de rt

Il est alors clair que les abréviations cs et lw dans les mnémoniques ci-dessus

signifient : compare_select et load word

1/ A partir de la description ci-dessus, donner le niveau RTL des différentes instructions

Instructions RTL

cs $rd, $rs, $rt

cslw $rd, $rs, $rt

cslwcs $rd, $rs, $rt

2/ Nous nous proposons d’apporter des modifications au chemin de donnée et aux

signaux de contrô le, en suivant les consignes suivantes :

- Il est recommandé de minimiser le nombre de matériel à ajouter.

- En ajoutant une nouvelle instruction, il ne faut pas altérer le fonctionnement des

instructions de base.

- Eviter d’ajouter des registres ou des mémoires au chemin de données.

- Il est possible d’ajouter des multiplexeurs, GALU.

Pour chacune des nouvelles instructions mentionnées, nous demandons la modification

du chemin de données, les valeurs des signaux de contrô le ajoutés et existants et la

nouvelle valeur du cycle d’horloge. Il sera tenu compte de l’optimalité de la solution.

a-1 ère pseudo-instruction : cs $rd, $rs, $rt

Dr Dhafer MEZGHANI Page 2

Module : Architectures Avancées MREEA1

Points de contrô le :

Nouvelle durée du cycle de l’horloge :………………………………………

b-2 éme pseudo-instruction : cslw $rd, $rs, $rt

Points de contrô le :

Dr Dhafer MEZGHANI Page 3

Module : Architectures Avancées MREEA1

Nouvelle durée du cycle de l’horloge :………………………………………

c-3 éme pseudo-instruction : cslwcs $rd, $rs, $rt

Points de contrôle :

Nouvelle durée du cycle de l’horloge :………………………………………

Exercice 2

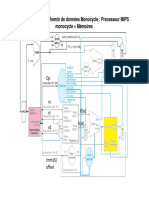

Nous rappelons le chemin de données monocycle MIPS (implémentant les instructions de type R,

addi, lw, sw et beq)

Dr Dhafer MEZGHANI Page 4

Module : Architectures Avancées MREEA1

(Q1) Etant donnée les latences d’exécution suivantes, donner le CPI et la durée du cycle de l’horloge :

Memory: 200ps | Banc de registres (READ/Write): 50ps | ALU et Adders: 100ps | Portes

logiques et multiplexeurs : 1ps | tout le reste est négligeable.

CPI = …………………………………………………………………

P = …………………………………………………………………….

Nous voulons implémenter de nouvelles instructions MIPS. Pour ceci, nous nous proposons

d’apporter des modifications au chemin de donnée et aux signaux de contrôle, en suivant les

consignes suivantes :

- Il est recommandé de minimiser le nombre de matériel à ajouter.

- En ajoutant une nouvelle instruction, il ne faut pas altérer le fonctionnement des instructions

de base.

- Eviter d’ajouter des ALU, des additionneurs, des registres ou des mémoires au chemin de

données.

- Il est possible d’ajouter des multiplexeurs et des portes logiques.

Dr Dhafer MEZGHANI Page 5

Module : Architectures Avancées MREEA1

Pour chacune des nouvelles instructions mentionnées, donner le RTL, la modification du chemin de

données, les valeurs des signaux de contrôle et la valeur du cycle d’horloge. Les instructions sont

indépendantes et il sera tenu compte de l’optimalité de la solution.

(Q2) instruction : getpc $rt . Cette instruction met dans $rt la valeur de PC de cette instruction.

RTL : ……………………………………………………………………………………………………………………………………….

Points de contôle :

Nouvelle durée du cycle de l’horloge :………………………………………

Dr Dhafer MEZGHANI Page 6

Module : Architectures Avancées MREEA1

(Q3) instruction : Load Word Register (lwr $rt, $rd ($rs))

Cette instruction met dans le register $rt le contenue de la mémoire d’adresse $rd plus $rs.

RTL : ……………………………………………………………………………………………………………………………………….

Points de contôle :

Nouvelle durée du cycle de l’horloge :………………………………………

Dr Dhafer MEZGHANI Page 7

Module : Architectures Avancées MREEA1

(Q4) instruction : Add à 3 opérandes: add3 $rd, $rs, $rt, $rx

Nouveau format d’instruction (opcode(6), rs(5), rt(5), rd(5), rx(5), (6 bits sont non utilisés)).

Cette instruction met dans le registre $rd la somme des contenus des registre $rs, $rt et $rx

RTL : ……………………………………………………………………………………………………………………………………….

Points de contôle :

Nouvelle durée du cycle de l’horloge :………………………………………

Dr Dhafer MEZGHANI Page 8

Module : Architectures Avancées MREEA1

(Q5) instruction : Branch Equal to Memory : beqm $rd, $rt, Imm11($rs)

Nouveau format d’instruction (opcode(6), rs(5), rt(5), rd(5), Imm11(11)).

Cette instruction modifie ajoute à PC le contenue du registre $rd, si le contenue du registre $rt est

égal au contenue de la mémoire d’addresse Imm11 plus le contenu de $rs.

RTL : ……………………………………………………………………………………………………………………………………….

Points de contôle :

Nouvelle durée du cycle de l’horloge :………………………………………

Dr Dhafer MEZGHANI Page 9

Module : Architectures Avancées MREEA1

(Q6) Les 2 instructions : Store Word and Increment swinc Rt, Imm16(Rs)

Cette instruction sauvegarde $rt dans la mémoire d’adresse $rs plus l’esxtension de Imm16 ET le

contenue de $rs pointera sur le mot suivant.

RTL : ……………………………………………………………………………………………………………………………………….

Points de contôle :

Nouvelle durée du cycle de l’horloge :………………………………………

Dr Dhafer MEZGHANI Page 10

Vous aimerez peut-être aussi

- TD3 ArchitectureDocument9 pagesTD3 ArchitectureDhafer MezghaniPas encore d'évaluation

- Examen Rattrapage IE5 2020 FinalDocument9 pagesExamen Rattrapage IE5 2020 FinalDhafer MezghaniPas encore d'évaluation

- Correction Rattrapage 2013Document10 pagesCorrection Rattrapage 2013abir cherifPas encore d'évaluation

- Examen MP1ERTA Janvier 2020 FinalDocument9 pagesExamen MP1ERTA Janvier 2020 FinalDhafer MezghaniPas encore d'évaluation

- Chapitre 3Document13 pagesChapitre 3Dhafer MezghaniPas encore d'évaluation

- Examen MCP Juin 2022 LEEA2Document6 pagesExamen MCP Juin 2022 LEEA2Dhafer MezghanniPas encore d'évaluation

- Examen SOC Session Rattrapage LEEA3 Janvier 2022Document6 pagesExamen SOC Session Rattrapage LEEA3 Janvier 2022Dhafer MezghanniPas encore d'évaluation

- TD 2 Complémentaire SoC MulticyckeDocument10 pagesTD 2 Complémentaire SoC MulticyckeDhafer MezghaniPas encore d'évaluation

- Examen MR1EEA Janvier 2020 FinalDocument9 pagesExamen MR1EEA Janvier 2020 FinalDhafer MezghaniPas encore d'évaluation

- Correction TD2 ArchitectureDocument8 pagesCorrection TD2 ArchitectureDhafer MezghaniPas encore d'évaluation

- Examen ISE MP2ERTA Janvier 2022Document5 pagesExamen ISE MP2ERTA Janvier 2022Dhafer MezghanniPas encore d'évaluation

- Examen Rattrapage Architectures Avancées Sur SoC 2019Document6 pagesExamen Rattrapage Architectures Avancées Sur SoC 2019Dhafer MezghaniPas encore d'évaluation

- Correction TD4 ArchitectureDocument3 pagesCorrection TD4 ArchitectureDhafer MezghaniPas encore d'évaluation

- Chapitre 2Document10 pagesChapitre 2Dhafer MezghaniPas encore d'évaluation

- TD1 ArchitectureDocument3 pagesTD1 ArchitecturemezghaniPas encore d'évaluation

- Chapitre 1Document13 pagesChapitre 1Dhafer MezghaniPas encore d'évaluation

- Partie 2Document126 pagesPartie 2AHMED AYADIPas encore d'évaluation

- TD FILTRES Isetcom STICL2 2018Document3 pagesTD FILTRES Isetcom STICL2 2018Mohamed Dhia Eddine DrissPas encore d'évaluation

- DS 3SE-archi Avancees 2020-2021-CorrectionDocument9 pagesDS 3SE-archi Avancees 2020-2021-CorrectionmehdiPas encore d'évaluation

- Amplificateur Lineaire Integre Et RetroaDocument10 pagesAmplificateur Lineaire Integre Et Retroapape diopPas encore d'évaluation

- Série 02Document5 pagesSérie 02kal joPas encore d'évaluation

- td3 BDDocument4 pagestd3 BDfouzibeladas16Pas encore d'évaluation

- Examen IE5 Janvier 2020 FinalDocument14 pagesExamen IE5 Janvier 2020 FinalDhafer MezghaniPas encore d'évaluation

- Examen MIPS 2019Document8 pagesExamen MIPS 2019Wael KhemakhemPas encore d'évaluation

- Serie TD 3Document5 pagesSerie TD 3Hani OmarPas encore d'évaluation

- Correction TD3 ArchitectureDocument9 pagesCorrection TD3 ArchitectureDhafer MezghaniPas encore d'évaluation

- SEmbarqué - M2-GSI Examen 2021 SolutionDocument2 pagesSEmbarqué - M2-GSI Examen 2021 Solutionaissat mohammed100% (1)

- Exercices Comp 1Document4 pagesExercices Comp 1ziribologhin2014Pas encore d'évaluation

- Examen PE IE5 Janvier 2022Document10 pagesExamen PE IE5 Janvier 2022Dhafer MezghanniPas encore d'évaluation

- Traitement Du Signal-Eln - L3 TD2: Analyse Et Synthèse Des Filtres AnalogiquesDocument4 pagesTraitement Du Signal-Eln - L3 TD2: Analyse Et Synthèse Des Filtres AnalogiquesSouha KhadraouiPas encore d'évaluation

- Examen Master RE 2019Document1 pageExamen Master RE 2019Omar BekkarPas encore d'évaluation

- Adaptation Des Impedances IDocument12 pagesAdaptation Des Impedances INabil DakhliPas encore d'évaluation

- DSP Resume PDFDocument31 pagesDSP Resume PDFStephane Durel MbidaPas encore d'évaluation

- EdeB TD4 1 2020Document2 pagesEdeB TD4 1 2020Arsene SohPas encore d'évaluation

- GEL-16120 - Modulation NumeriqueDocument30 pagesGEL-16120 - Modulation NumeriqueIbrahimFaroukSolarPas encore d'évaluation

- TD6 Tech T 2021Document4 pagesTD6 Tech T 2021ameni grami100% (2)

- Analyses VH DDocument10 pagesAnalyses VH DMustapha El IdrissiPas encore d'évaluation

- TD N 4 (Supplemetaire) FpgaDocument2 pagesTD N 4 (Supplemetaire) FpgaLE BARONPas encore d'évaluation

- TD N 3 FpgaDocument2 pagesTD N 3 FpgaLE BARON100% (1)

- TD4Document2 pagesTD4Ihssan KHPas encore d'évaluation

- Exercices Can CnaDocument6 pagesExercices Can CnaFlorian FerreiraPas encore d'évaluation

- Correction TD1 - 2Document5 pagesCorrection TD1 - 2Gliouez SirinePas encore d'évaluation

- Jeu D - Instructions Du PIC16F84ADocument9 pagesJeu D - Instructions Du PIC16F84AOMAR ENNAJIPas encore d'évaluation

- TD Corrigé ARCHI 1Document8 pagesTD Corrigé ARCHI 1Dhafer MezghaniPas encore d'évaluation

- Ser TD4 20222023Document4 pagesSer TD4 20222023ramzi ayadi100% (1)

- Partiels2a PDFDocument314 pagesPartiels2a PDFchfakhtPas encore d'évaluation

- Travaux PratiqueDocument23 pagesTravaux PratiqueRomaysa jijiPas encore d'évaluation

- Série de Révision Méthodologie de Conception Des ProcesseursDocument6 pagesSérie de Révision Méthodologie de Conception Des ProcesseursmezghaniPas encore d'évaluation

- Suite Suj Exam OP-2017-2018Document5 pagesSuite Suj Exam OP-2017-2018AliOucharPas encore d'évaluation

- Chapitre 1: Traitement Temporel Des Signaux: 4 3 Sin - 30 1 2 2 Sin - 20Document1 pageChapitre 1: Traitement Temporel Des Signaux: 4 3 Sin - 30 1 2 2 Sin - 20Issam Akermi100% (1)

- Presentation Cour Microproc2Document33 pagesPresentation Cour Microproc2user2014523Pas encore d'évaluation

- DevoirDocument2 pagesDevoirmohammed boufenziPas encore d'évaluation

- Support de Cours FH EtudiantDocument136 pagesSupport de Cours FH EtudiantbilllPas encore d'évaluation

- 2Document2 pages2isra khelielPas encore d'évaluation

- Poly TDs TNS Francais 2017 2018Document26 pagesPoly TDs TNS Francais 2017 2018Miloud MOULAY OMARPas encore d'évaluation

- TD Cours 1 CorrectionDocument8 pagesTD Cours 1 Correctionمصعب مصعبPas encore d'évaluation

- Architecture de 8086Document7 pagesArchitecture de 8086mezghaniPas encore d'évaluation

- Bureau D'etude STM32F4Document227 pagesBureau D'etude STM32F4MARWA BEN HAMMOUDA50% (2)

- TD1Document2 pagesTD1Abdelfatah FerhatPas encore d'évaluation

- Report Article 13Document1 pageReport Article 13mezghaniPas encore d'évaluation

- Emploi MP2ERTA - 20-21Document2 pagesEmploi MP2ERTA - 20-21mezghaniPas encore d'évaluation

- Fiche Autorisation Depot2020Document2 pagesFiche Autorisation Depot2020mezghaniPas encore d'évaluation

- PV de Réunion-2 Rania ChtiouiDocument1 pagePV de Réunion-2 Rania ChtiouimezghaniPas encore d'évaluation

- Cours 5 MulticycleDocument8 pagesCours 5 MulticyclemezghaniPas encore d'évaluation

- Monocycle PDFDocument1 pageMonocycle PDFmezghaniPas encore d'évaluation

- Cours CompletDocument69 pagesCours CompletDhafer MezghaniPas encore d'évaluation

- Examen SL 1Document4 pagesExamen SL 1mezghaniPas encore d'évaluation

- TD1 ArchitectureDocument3 pagesTD1 ArchitecturemezghaniPas encore d'évaluation

- Examen SL 3Document2 pagesExamen SL 3mezghaniPas encore d'évaluation

- Examen SL 4Document6 pagesExamen SL 4mezghani100% (1)

- Liste Des Sociétés 2Document12 pagesListe Des Sociétés 2mezghaniPas encore d'évaluation

- TD MulticycleDocument4 pagesTD MulticyclemezghaniPas encore d'évaluation

- Liste Des SociétésDocument9 pagesListe Des SociétésmezghaniPas encore d'évaluation

- Série de Révision Méthodologie de Conception Des ProcesseursDocument6 pagesSérie de Révision Méthodologie de Conception Des ProcesseursmezghaniPas encore d'évaluation

- Cours 2 Les MémoiresDocument5 pagesCours 2 Les MémoiresmezghaniPas encore d'évaluation

- Cours 1 Architectures Des CalculateursDocument12 pagesCours 1 Architectures Des CalculateursmezghaniPas encore d'évaluation

- Architecture de 8086Document7 pagesArchitecture de 8086mezghaniPas encore d'évaluation

- Cours 3 Architectures Des Jeux D'istruction RISCDocument10 pagesCours 3 Architectures Des Jeux D'istruction RISCmezghaniPas encore d'évaluation

- Cours 4 Conception Des Processeurs MonocyclesDocument7 pagesCours 4 Conception Des Processeurs MonocyclesmezghaniPas encore d'évaluation

- WCM Questions and AnswersDocument26 pagesWCM Questions and Answersameer meerPas encore d'évaluation

- Exercices Corrigés de La Comptabilité Des Sociétés PDFDocument7 pagesExercices Corrigés de La Comptabilité Des Sociétés PDFMelle Siham100% (18)

- 2 WebServices 1upDocument86 pages2 WebServices 1updouina arouk100% (1)

- Se chp3 Gestionmemoire 170207132616Document44 pagesSe chp3 Gestionmemoire 170207132616Med Aref100% (1)

- Limite D - Une Suite NumériqueDocument2 pagesLimite D - Une Suite NumériqueSanae SanonaPas encore d'évaluation

- Convocation TCF CANADA - Epreuves Sur OrdinateurDocument1 pageConvocation TCF CANADA - Epreuves Sur OrdinateurBill TaguigPas encore d'évaluation

- Commande-Publique Referentiel 2021-01 V1defDocument41 pagesCommande-Publique Referentiel 2021-01 V1deflecouveyPas encore d'évaluation

- Stages Et Pfe Book Ey 2022 2023Document120 pagesStages Et Pfe Book Ey 2022 2023Saif WarradiPas encore d'évaluation

- CH MemoiresDocument71 pagesCH MemoiresN El kechaiPas encore d'évaluation

- CV 2abderrahim YAHYAOUI PDFDocument1 pageCV 2abderrahim YAHYAOUI PDFhaltreiz SarutobiiPas encore d'évaluation

- Les Déterminants de La Compétitivité de L'entrepriseDocument27 pagesLes Déterminants de La Compétitivité de L'entrepriseDôn PhạmPas encore d'évaluation

- Thèse de DoctoratDocument134 pagesThèse de DoctoratKada BenhamidiPas encore d'évaluation

- IntroductioN Au Système GNU PDFDocument37 pagesIntroductioN Au Système GNU PDFSteve Loïc NGANDAPas encore d'évaluation

- Poly Introduction Programmation de Base F HenniDocument173 pagesPoly Introduction Programmation de Base F HennisowPas encore d'évaluation

- Abc P57 PDFDocument130 pagesAbc P57 PDFOthmane SettariPas encore d'évaluation

- tp1 PersistanceDocument3 pagestp1 PersistancenaasPas encore d'évaluation

- Tchaikovsky 5 II Horn Solo - Score and PartsDocument9 pagesTchaikovsky 5 II Horn Solo - Score and PartsAlisson PedrosoPas encore d'évaluation

- Corrigé Spécialité Génie Meca STIDD GP1 2022Document5 pagesCorrigé Spécialité Génie Meca STIDD GP1 2022kara baPas encore d'évaluation

- CoursDocument93 pagesCoursPrincePas encore d'évaluation

- Rapport Du Mini Projet Algorithme NumériqueDocument7 pagesRapport Du Mini Projet Algorithme NumériqueEya JaouaPas encore d'évaluation

- Contrat ENGIEDocument5 pagesContrat ENGIEbiardPas encore d'évaluation

- Projet Supports de Transmission Sujet D1Document2 pagesProjet Supports de Transmission Sujet D1Nour elhouda cirine BourasPas encore d'évaluation

- Garniture Mécanique Double: Notice de Service ComplémentaireDocument12 pagesGarniture Mécanique Double: Notice de Service ComplémentaireDENOUPas encore d'évaluation

- Audit Energétique ISO 50001 SOCOTEC 30 06 2015Document39 pagesAudit Energétique ISO 50001 SOCOTEC 30 06 2015ESSALIM ABDELHAKIMPas encore d'évaluation

- ÉconométrieDocument24 pagesÉconométrieNicolas KiadivilaPas encore d'évaluation

- Du Fini A Linfini PDFDocument3 pagesDu Fini A Linfini PDFwesh007Pas encore d'évaluation

- Chap 2Document15 pagesChap 2benjunior ahmedPas encore d'évaluation

- Plan de Montage Du Contrepoids - Stacker L21ST01 - Cbmi - 20122022 PDFDocument6 pagesPlan de Montage Du Contrepoids - Stacker L21ST01 - Cbmi - 20122022 PDFHa Kim BJPas encore d'évaluation

- Mini Projet m2 Hu (Assainissementii) 2021Document5 pagesMini Projet m2 Hu (Assainissementii) 2021Amel HydPas encore d'évaluation

- Fiche EnseignantDocument4 pagesFiche EnseignantWulfaPas encore d'évaluation