Académique Documents

Professionnel Documents

Culture Documents

Circuits Séquentiels-2

Transféré par

Aida GueyeTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Circuits Séquentiels-2

Transféré par

Aida GueyeDroits d'auteur :

Formats disponibles

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

Note de COURS

6 : Circuits séquentiels

Circuits séquentiels synchrones

Circuits asynchrones : Les bascules

• Les bascules (aussi appelées verrous) sont les opérateurs élémentaires de mémorisation.

• Leur état présent, déterminé par l'état des sorties, est fonction des entrées et de l'état précédent des sorties.

Bascule RS :

Bascule RS avec activation :

Bascule D (Latch) avec activation :

• ̅ et S=D

Basée sur une bascule RS avec 𝑅 = 𝐷

Circuits synchrones : Les Flip-Flop

• Les flip-flop sont composées d’une bascule avec un signal d’activation et d’un circuit qui détecte les fronts d’horloge.

• La figure suivante repose sur une bascule RS et un circuit détecteur de front d’horloge prenant en entrée un signal d’horloge appelé

‘clock’. Ce signal est une succession de signaux carrés de fréquence fixe.

• Le circuit ‘edge detector’ génère durant une courte période une pulsation sur les fronts montants (ou descendant). Ces signaux

activent durant une courte période la bascule.

• Le comportement d’une flip-flop est semblable à

une bascule qui n’est activée que sur les fronts

d’horloge.

-1- Enseignant : David DEFOUR

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

Classification des Flip-Flop :

Flip-Flop RS Flip-Flop D Flip-Flop T

Sur le front d’horloge : 𝑄𝑡+1 ← 𝐷 𝑄𝑡+1 ← 𝐷 = 𝑇⨁𝑄𝑡

𝑄𝑡+1 ← 𝑆𝑅̅ + 𝑄𝑡 𝑆̅ = 𝑅̅(𝑆 + 𝑄𝑡 𝑆̅)

= 𝑅̅(𝑆 + 𝑆̅)(𝑆

+ 𝑄𝑡 )

= 𝑅̅𝑆 + 𝑅̅𝑄𝑡

Lorsqu’il n’y a pas de front d’horloge

𝑄𝑡+1 = 𝑄𝑡

Flip-Flop JK

̅̅̅𝑡 + 𝐾

𝑄𝑡+1 ← 𝐽𝑄 ̅𝑄𝑡

Circuits synchrones : Les registres

Les registres à n-bits :

• Ce sont des ensembles de n flip-flops D, où chaque flip-flop

stocke 1 bit d’information. Les flip-flops sont connectés en

parallèle, partage les signaux d’horloge (clock) et de remise à

zéro (resetn)

Les registres à décalage à n-bits :

• Ce sont des ensembles de n flip-flops D connectés en série et partagent les signaux d’horloge (clock) et de remise à zéro (resetn).

• din est le signal d’entrée (sériel) et dout de signal de sortie.

• L’ordre des sorties des flip-flops Q0Q1…Qn donne des registres à décalage

o à droite, si les bits se déplacent des bits de poids fort vers les bits de poids faible,

o à gauche, si les bits se déplacent des bits de poids faible vers les bits de poids fort.

Registre à décalage à droite :

-2- Enseignant : David DEFOUR

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

Registre à décalage à gauche :

Chronogramme

Circuits synchrones : Les compteurs

• Les compteurs sont très utilisés car ils permettent de compter les occurrences d’un événements, de réaliser des mesures de temps…

• Les compteurs synchrones changent la valeur de leur sortie sur un signal d’horloge. Chaque flip-flop qui le compose partage le même

signal d’horloge (clock) et de remise à zéro (resetn).

Un Compteur binaire, à n-bit compte de 0 à 2n-1. Exemple de compteur à 2-bit :

-3- Enseignant : David DEFOUR

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

Émulateur de Random Access Memory (RAM)

• Le circuit séquentiel représente une mémoire à 8 adresses, où

chaque adresse stocke 4 bits de donnée. Chaque position est

implémentée à l’aide d’un registre 4-bit. Les données sont

écrites/lues vers/depuis les registres à l’aide du signal

address.

• Écriture en mémoire : (wr_rd=1) les 4 bits de donnée

d’entrée (Din) sont écrites en mémoire. Le signal d’adresse

sélectionne le registre où seront mise les données. Et

l’afficheur 7 segments doit afficher la valeur ’0’.

• Lecture en mémoire : (wr_rd=0) la sortie du MUX est

envoyée à l’afficheur 7 segments (valeur hexadécimale). Le

signal d’adresse sélectionne le registre lu.

Automates à états finis (FSM)

• Les circuits séquentiels sont aussi appelés machines ou automates à états finis (ou Finite State Machines/FSM), car le comportement

fonctionnel de ces circuits peut être représenté à l’aide d’un nombre fini d’état (sortie de flip-flop).

• Supposons que l’on veuille concevoir un circuit qui compte de 0 à 3 et qui envoie un signal d’un cycle d’horloge lorsque la valeur

max est atteinte. Il est possible d’implémenter ce circuit à l’aide d’un compteur et de portes logiques. Comment procéder si l’on veut

un signal de 2 cycles ? Il est toujours possible de concevoir un circuit à l’aide d’un compteur, de flip-flop et de portes logiques,

cependant l’utilisation d’automate à états finis fournie une solution plus élégante.

Modèle FSM

• Les automates sont dits synchrones lorsque le passage d'un état (état présent) à l'état suivant

(état futur) a lieu sur une transition d'un signal appelé horloge commun à toutes les bascules

de l'automate.

• Il existe 2 types d’automate :

o Automate de Moore : l’état futur est fonction de l’état présent et des entrées. Les

sorties sont fonction de l’état présent.

o Automate de Mealy : l’état futur est fonction de l’état présent et des entrées. Les sorties sont fonction de l’état présent et

des entrées.

• Il y a équivalence entre les deux types d'automates : tout automate de Moore peut être transformé en automate de Mealy et

réciproquement. L'automate de Mealy a toujours moins d'états que l'automate de Moore correspondant.

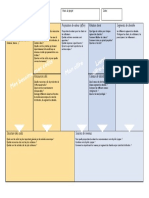

Exemple 1 :

Compteur à 2-bit (valeur 00, 01,10, 11, 00) avec signal d’activation et une sortie ‘z’ prenant la valeur 1 lorsque le compteur est égal à 11.

1. Première étape : Dessiner le graphe de transition et le diagramme de transition. Les valeurs sur les flèches font références aux valeurs

E/z où E correspond à la donnée en entrée et z la sortie telle que décrite précédemment. Les états sont étiquetés S1, S2, S3, S4.

-4- Enseignant : David DEFOUR

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

État État

E Valeur Z

courant suivant

0 S1 S1 00 0

0 S2 S2 01 0

0 S3 S3 10 0

0 S4 S4 11 1

1 S1 S2 01 0

1 S2 S3 10 0

1 S3 S4 11 0

1 S4 S1 00 1

Graphe de transition d’un compteur 2-bits Diagramme de transition d’un compteur 2 bits

2. Deuxième étape : Assignation des états. Il est possible d’attribuer les états (S1, S2, S3, S4) aux flip-flops. Cette assignation est

purement arbitraire, cependant dans un souci d’économie de ressource il est possible d’assigner ces états à la valeur souhaitée et la

sortie du compteur devient la sortie des flip-flops.

S1 : Q=00 ; S2 : Q=01 ; S3 : Q=10 ; S4 : Q=11

3. Troisième étape : Table d’excitation. Elle permet de déterminer quelles valeurs il faut appliquer aux entrées pour faire évoluer la

sortie d’un état vers un autre. Cela consiste à remplacer les étiquettes par celles choisies à l’étape 2.

E État courant État suivant Z

Q1(t) Q0(t) Q1(t+1) Q0(t+1)

0 0 0 0 0 0

0 0 1 0 1 0

0 1 0 1 0 0

0 1 1 1 1 1

1 0 0 0 1 0

1 0 1 1 0 0

1 1 0 1 1 0

1 1 1 0 0 1

4. Quatrième étape : Génération des équations d’excitation et minimisation. Les signaux Q1(t+1) et Q0(t+1) sont connectés aux entrées

des flip-flops. La sortie z dépend uniquement de l’état présent. Les sorties Q1 et Q0 sont les états et dépendent uniquement des états

courants

5. Cinquième état : Implémentation du circuit

Exemple 2 :

Compteur en code de gray à 2-bit (valeur 00, 01,10, 11, 00) avec signal d’activation et une sortie ‘z’ prenant la valeur 1 lorsque le compteur

est égal à 10.

-5- Enseignant : David DEFOUR

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

1. Première étape : Dessiner le graphe de transition et le diagramme de transition. Les valeurs sur les flèches font références aux valeurs

E/z où E correspond à la donnée en entrée et z la sortie telle que décrite précédemment. Les états sont étiquetés S1, S2, S3, S4.

État État

E Valeur Z

courant suivant

0 S1 S1 00 0

0 S2 S2 01 0

0 S3 S3 11 0

0 S4 S4 10 1

1 S1 S2 01 0

1 S2 S3 11 0

1 S3 S4 10 0

1 S4 S1 00 1

Graphe de transition d’un compteur 2-bits Diagramme de transition d’un compteur 2 bits

2. Deuxième étape : Assignation des états. Il est possible d’attribuer les états (S1, S2, S3, S4) aux flip-flops. Cette assignation est

purement arbitraire, cependant dans un souci d’économie de ressource il est possible d’assigner ces états à la valeur souhaitée et la

sortie du compteur devient la sortie des flip-flops.

S1 : Q=00 ; S2 : Q=01 ; S3 : Q=11 ; S4 : Q=10

Une solution alternative consiste à prendre S1 : Q=00 ; S2 : Q=01 ; S3 : Q=10 ; S4 : Q=11. Cette solution bien que plus consistante

avec l’encodage des états ne permets pas de prendre directement la sortie des flip-flops.

3. Troisième étape : Table d’excitation. Elle permet de déterminer quelles valeurs il faut appliquer aux entrées pour faire évoluer la

sortie d’un état vers un autre. Cela consiste à remplacer les étiquettes par celles choisies à l’étape 2.

E État courant État suivant Z

Q1(t) Q0(t) Q1(t+1) Q0(t+1)

0 0 0 0 0 0

0 0 1 0 1 0

0 1 1 1 1 0

0 1 0 1 0 1

1 0 0 0 1 0

1 0 1 1 1 0

1 1 1 1 0 0

1 1 0 0 0 1

4. Quatrième étape : Génération des équations d’excitation et minimisation. Les signaux Q1(t+1) et Q0(t+1) sont connectés aux entrées

des flip-flops. La sortie z dépend uniquement de l’état présent. Les sorties Q1 et Q0 sont les états et dépendent uniquement des états

courants

5. Cinquième état : Implémentation du circuit

-6- Enseignant : David DEFOUR

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

Exemple 3 :

• Circuit avec une entrée x et une sortie z qui prend la valeur 1 lorsque qu’un changement de valeur 1=>0 est détectée en entrée.

• Remarquez que z prends la valeur 1 dès que la transition est détectée indépendamment de l’horloge.

• Une solution pour avoir un beau signal en sortie consiste à inclure une flip-flop avec z en entrée.

• Le premier état S1 permet d’initialiser la sortie z à 0. C’est un automate de MEALY

Exemple 4 :

• Circuit avec une entrée x et une sortie z qui prend la valeur 1 lorsque qu’il détecte la séquence 1011011 en entrée. La valeur d’un bit

est analysée sur le front d’horloge. Après chaque séquence valide, le circuit recherche une nouvelle séquence.

• Le signal E valide l’entrée x. Si E=1, x est valide et invalide sinon. C’est un automate de MEALY.

-7- Enseignant : David DEFOUR

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

-8- Enseignant : David DEFOUR

Composants du processeur David DEFOUR

Licence 1, Université de Perpignan

Représentation algorithmique des automates (ASM) :

Compteur de Gray, z=1 lorsque Q=10 Détecteur de séquence 010011

-9- Enseignant : David DEFOUR

Vous aimerez peut-être aussi

- A propos du Digital!: Le digital pour tous! Le numérique en questions/réponses pour le modélisme ferroviaireD'EverandA propos du Digital!: Le digital pour tous! Le numérique en questions/réponses pour le modélisme ferroviaireÉvaluation : 3.5 sur 5 étoiles3.5/5 (3)

- COMPTE RENDU de FORMATION Initiation en Informatique Et Aux Logiciels de Base Koutiala Du 15 Au 19 Octobre 2012Document5 pagesCOMPTE RENDU de FORMATION Initiation en Informatique Et Aux Logiciels de Base Koutiala Du 15 Au 19 Octobre 2012Mohamed Alimou BarryPas encore d'évaluation

- DVWA Rapport PDFDocument21 pagesDVWA Rapport PDFmedzied haddarPas encore d'évaluation

- Guide Des Procédures DématérialiséesDocument130 pagesGuide Des Procédures DématérialiséesChimène NguPas encore d'évaluation

- Ch5 CI9 I4 Capteur NumDocument12 pagesCh5 CI9 I4 Capteur Numcpommier100% (1)

- Virtual Private Network (VPN) : Encadrer Par: PR - Youness BalboulDocument18 pagesVirtual Private Network (VPN) : Encadrer Par: PR - Youness Balboulismail boudzgzaouinPas encore d'évaluation

- Ch10 CI11 I11 SequentielleDocument8 pagesCh10 CI11 I11 Sequentiellecpommier100% (1)

- Couche Physique Technique Transmission Csma CADocument9 pagesCouche Physique Technique Transmission Csma CAFadhilaCelinePas encore d'évaluation

- CM2: Circuits Séquentiels: Licence STS L1Document29 pagesCM2: Circuits Séquentiels: Licence STS L1YASSINE KERWIPas encore d'évaluation

- Chapitre 5 ElectroniqueDocument30 pagesChapitre 5 ElectroniqueimanesaidytPas encore d'évaluation

- Cours ELN-NUM CH4Document61 pagesCours ELN-NUM CH4Samuel SeriPas encore d'évaluation

- Archi CM08Document16 pagesArchi CM08Àźwű ŠāģhřűPas encore d'évaluation

- Logique SéquentielleDocument70 pagesLogique SéquentielleMerryPas encore d'évaluation

- Circuits SéquentielsDocument29 pagesCircuits Séquentielsmustapha skanderPas encore d'évaluation

- TP 07Document8 pagesTP 07Ilyas BoufermaPas encore d'évaluation

- Chap5 Systèmes Séquentiels NKHAILI Complet-1Document16 pagesChap5 Systèmes Séquentiels NKHAILI Complet-1lodyyy4Pas encore d'évaluation

- Cours de Bascules Numériques 2017-2018Document28 pagesCours de Bascules Numériques 2017-2018Camile SiliaPas encore d'évaluation

- Cours de Bascules Numériques 2021-22Document23 pagesCours de Bascules Numériques 2021-22Manel AsnicarPas encore d'évaluation

- Logique SequentielleDocument28 pagesLogique SequentielleIkram ElaimaPas encore d'évaluation

- Cours Les Circuits Séquentiels (Architecture Des Ordinateurs)Document34 pagesCours Les Circuits Séquentiels (Architecture Des Ordinateurs)momoPas encore d'évaluation

- ch5 CircuitssequentielsDocument14 pagesch5 CircuitssequentielsHicham Edd0% (1)

- ch2 - C - Logiques Séquentiels (Complet)Document85 pagesch2 - C - Logiques Séquentiels (Complet)DønuTsPas encore d'évaluation

- Présentation Logique SequentielleDocument50 pagesPrésentation Logique SequentiellemohPas encore d'évaluation

- Chapitre 1 - Rappel Sur Les Circuits SéquentielsDocument18 pagesChapitre 1 - Rappel Sur Les Circuits SéquentielsTtech hackPas encore d'évaluation

- 6-2-Logique SéquentielleDocument48 pages6-2-Logique Séquentiellelmons saroutPas encore d'évaluation

- Cours 1 4AMRI Circuits ProgrammablesDocument23 pagesCours 1 4AMRI Circuits ProgrammableshamzaPas encore d'évaluation

- Chap 4 Logique Séq 2020Document14 pagesChap 4 Logique Séq 2020Ali DridiPas encore d'évaluation

- Bascule CRDocument5 pagesBascule CRAbdourazak AbouPas encore d'évaluation

- Séquentiel - ENSA - Synthese Asynchrone HuffmanDocument40 pagesSéquentiel - ENSA - Synthese Asynchrone HuffmanAicha LahnoukiPas encore d'évaluation

- 14 SéquentielDocument4 pages14 SéquentielWissal NaciryPas encore d'évaluation

- Fon Ctions Log I QuesDocument5 pagesFon Ctions Log I QuesAdlan MessaoudPas encore d'évaluation

- Chapitre 0 - RDDocument86 pagesChapitre 0 - RDtarek.malloPas encore d'évaluation

- Sol 4Document5 pagesSol 4Nisrine ZAIDAPas encore d'évaluation

- Robotique: Enseignant: Jean-Philippe RobergeDocument45 pagesRobotique: Enseignant: Jean-Philippe RobergerabehvillaPas encore d'évaluation

- Registre 14Document4 pagesRegistre 14khaled fawazPas encore d'évaluation

- Chap 4Document51 pagesChap 4MERYEM LAHBOUBPas encore d'évaluation

- Composants UtilisésDocument7 pagesComposants UtilisésHamidi AbderrhmenPas encore d'évaluation

- Chapitre 2 Architecture 2019 - 2020Document14 pagesChapitre 2 Architecture 2019 - 2020Libasse Laye MbenguePas encore d'évaluation

- BasculesDocument2 pagesBasculesAmine JraifPas encore d'évaluation

- Chap5-Circuits de Decodage Et de MultiplexageDocument6 pagesChap5-Circuits de Decodage Et de MultiplexageAhmed GourinePas encore d'évaluation

- 1-Architecture Chapitre 1-4Document35 pages1-Architecture Chapitre 1-4Mounaim AaouadouPas encore d'évaluation

- Chap6 PDFDocument19 pagesChap6 PDFmohcenPas encore d'évaluation

- TDRevisionDocument4 pagesTDRevisionKatia ChalalPas encore d'évaluation

- PDF LogicseqDocument25 pagesPDF LogicseqYassine FalahPas encore d'évaluation

- Les Circuits SéquentielsDocument14 pagesLes Circuits SéquentielsJOHNE JKPas encore d'évaluation

- Circuitslogiques SequentielDocument64 pagesCircuitslogiques SequentielussamautshihaPas encore d'évaluation

- BasculesDocument18 pagesBasculesRashid LaanayaPas encore d'évaluation

- Chapitre4 BasculesDocument20 pagesChapitre4 BasculeskhlifiPas encore d'évaluation

- 3 Compteur Synchrone 2011 2012Document8 pages3 Compteur Synchrone 2011 2012Mohamed EL MASSOUDIPas encore d'évaluation

- 11 Logique Sequentielle StagiaireDocument17 pages11 Logique Sequentielle Stagiairemerazga ammarPas encore d'évaluation

- CIRA1 - 3) Logique Sequentielle PDFDocument7 pagesCIRA1 - 3) Logique Sequentielle PDFLANGO RICHARD BAMBAPas encore d'évaluation

- 12-Algebre de BooleDocument6 pages12-Algebre de BooleYu XinPas encore d'évaluation

- OscilloscopeDocument5 pagesOscilloscopexyakaxPas encore d'évaluation

- 3 Logique Sequentielle PDFDocument4 pages3 Logique Sequentielle PDFmauricetaPas encore d'évaluation

- Transformateur de PuissanceDocument34 pagesTransformateur de Puissancem.ferfra66Pas encore d'évaluation

- CH03 Cours Systèmes LogiquesDocument11 pagesCH03 Cours Systèmes Logiquesbrix brainPas encore d'évaluation

- Annales D'examensDocument22 pagesAnnales D'examensyassinePas encore d'évaluation

- Les Bascules Et Registres: A.LebrunDocument30 pagesLes Bascules Et Registres: A.LebrunMouhcine ZianeePas encore d'évaluation

- Chapitre 4 CinematiqueDocument19 pagesChapitre 4 CinematiqueAbeka Kader100% (1)

- SYNTHESE DES SYSTEMES SEQUENTIELS doc profDocument10 pagesSYNTHESE DES SYSTEMES SEQUENTIELS doc profNejib JallouliPas encore d'évaluation

- Ensi2 TS S8Document12 pagesEnsi2 TS S8Caroline ElkharratPas encore d'évaluation

- 2020-2021 - Janv - E&D Genie Civil - SCUIO - VFDocument12 pages2020-2021 - Janv - E&D Genie Civil - SCUIO - VFma abdou diopPas encore d'évaluation

- La Classification Des Roches SédimentairesDocument9 pagesLa Classification Des Roches SédimentairesAida GueyePas encore d'évaluation

- Pix DelibDocument9 pagesPix Delibmanel rhPas encore d'évaluation

- Structures - Méthode de CalculDocument1 pageStructures - Méthode de CalculAida GueyePas encore d'évaluation

- Modà Le BMCDocument1 pageModà Le BMCAida GueyePas encore d'évaluation

- Intro Contrà Le de GestionDocument2 pagesIntro Contrà Le de GestionAida GueyePas encore d'évaluation

- Les Roches MetamorphiquesDocument3 pagesLes Roches MetamorphiquesAida GueyePas encore d'évaluation

- Virement Ly AgencyDocument1 pageVirement Ly AgencyLi LiPas encore d'évaluation

- Consignes Rapport Sortie Terrain GéologieDocument2 pagesConsignes Rapport Sortie Terrain GéologieAida GueyePas encore d'évaluation

- Formulaire RDMDocument1 pageFormulaire RDMAida GueyePas encore d'évaluation

- Livre 3Document1 pageLivre 3Schmetterling TraurigPas encore d'évaluation

- Pix EiffelDocument24 pagesPix Eiffelbenji .971Pas encore d'évaluation

- Alluvions LoireDocument3 pagesAlluvions LoireAida GueyePas encore d'évaluation

- La PieDocument6 pagesLa PieAida GueyePas encore d'évaluation

- Gestion de Portefeuille Et Marchés FinanciersDocument48 pagesGestion de Portefeuille Et Marchés FinanciersyoubixPas encore d'évaluation

- TP4 - Validation Des ChampsDocument4 pagesTP4 - Validation Des ChampsGhassen AbdennajiPas encore d'évaluation

- ARCODE Procédure de Réinitialisation de L'entrée enDocument3 pagesARCODE Procédure de Réinitialisation de L'entrée enmicrocheriet100% (1)

- Courrier - Mustapha Massous - Outlook 2Document1 pageCourrier - Mustapha Massous - Outlook 2rihm.massousPas encore d'évaluation

- Cours5 Uml Dcu Exos PDFDocument81 pagesCours5 Uml Dcu Exos PDFilyes adlaPas encore d'évaluation

- How VPN WorksDocument6 pagesHow VPN WorksIldevert Mboutsou BouilaPas encore d'évaluation

- Brochure Système Numérique de Contrôle Commande Deltav FR 57132Document40 pagesBrochure Système Numérique de Contrôle Commande Deltav FR 57132Eric LefrançaisPas encore d'évaluation

- Mahout Machine Learning Pour Hadoop Par Bertrand DechouxDocument33 pagesMahout Machine Learning Pour Hadoop Par Bertrand DechouxAhmedPas encore d'évaluation

- Festo CMMT EMMT PSIplus FR 202204Document12 pagesFesto CMMT EMMT PSIplus FR 202204martaodansleauPas encore d'évaluation

- Subiecte Lucru XDocument12 pagesSubiecte Lucru XBarbu IuliaPas encore d'évaluation

- Presentation ArduinoDocument16 pagesPresentation ArduinotestPas encore d'évaluation

- Compte Rendu TP 2 CSRDocument11 pagesCompte Rendu TP 2 CSRSouad ArrPas encore d'évaluation

- Cours Initiation Android PDFDocument37 pagesCours Initiation Android PDFAbdellah GhoualiPas encore d'évaluation

- Examen 1617Document3 pagesExamen 1617Loic GannoPas encore d'évaluation

- Analyse de DonneesDocument482 pagesAnalyse de DonneesChecourish BabyPas encore d'évaluation

- Rapport K.B 2020 Bon PDFDocument59 pagesRapport K.B 2020 Bon PDFbasile kamdem100% (2)

- 10 Offre CMRDocument30 pages10 Offre CMRMohammed ZizahPas encore d'évaluation

- JAVA ExercicesDocument11 pagesJAVA Exercicesblack disasterPas encore d'évaluation

- Cour Adminstation Reseau Sous LinuxDocument4 pagesCour Adminstation Reseau Sous LinuxAbderrahmane WelePas encore d'évaluation

- Examen_NOSQL_decembre-2021Document6 pagesExamen_NOSQL_decembre-2021amina.mamiPas encore d'évaluation

- Emtiez AKERMI ResumeDocument1 pageEmtiez AKERMI ResumeDhouhaHajjiPas encore d'évaluation

- Ann 1 FRDocument17 pagesAnn 1 FRStephanie YoungPas encore d'évaluation

- 12 Bonnes Raisons de Choisir Un ERPDocument1 page12 Bonnes Raisons de Choisir Un ERPALI JedidiPas encore d'évaluation

- Correction2-WPS OfficeDocument3 pagesCorrection2-WPS OfficeNavi ForcePas encore d'évaluation

- Feuille 13-PsiDocument3 pagesFeuille 13-Psiamo norPas encore d'évaluation