Académique Documents

Professionnel Documents

Culture Documents

3 - Circuits Logiques - Dubois2024

Transféré par

nathanmacxintradingTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

3 - Circuits Logiques - Dubois2024

Transféré par

nathanmacxintradingDroits d'auteur :

Formats disponibles

III- 1

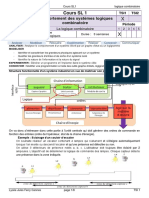

Chapitre III : LOGIQUE BOOLEENE

III.1. DEFINITION

L'algèbre de Boole est la partie des mathématiques qui s'intéresse à une

approche algébrique de la logique, càd aux opérations et aux fonctions sur les

variables logiques.

Elle fut inventée par le mathématicien britannique George Boole. Aujourd'hui, l'algèbre

de Boole trouve de nombreuses applications dans la conception et réalisation des

circuits électroniques en Automatique, Informatique, Télécoms, ...

Une fonction logique est une combinaison de variables logiques reliées par

des opérations logiques. Elle est matérialisée par des portes logiques.

Elle peut être représentée par une table de vérité (TV), une équation logique ou un

logigramme.

III.2. OPERATIONS LOGIQUES & PROPRIETES

3.2.1. Types d’opérations logiques

Toute fonction booléenne peut être décrite à l’aide d’opérations logiques :

a) Opérations logiques fondamentales (de base) :

Complément logique (Inversion logique) Négation (NOT, pas)

Somme logique (addition logique) Disjonction ou Réunion (OR, OU inclusif)

Produit logique (multiplication logique) : Conjonction ou Intersection (AND, Et)

OR AND NOT

DR

b) Opérations logiques dérivées :

Inversion de la somme logique (NOR)

Disjonction exclusive (XOR = OU exclusif);

Inversion du produit logique (NAND) ;

Identité ou égalité (YES);

Equivalence (EQV) ou (XNOR);

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 2

3.2.2. Propriétés et caractéristiques des opérations logiques

Propriétés mono variables Propriétés multi variables

1) Elément neutre 1) Commutativité

2) Elément nul (Elément absorbant) 2) Associativité

3) Idempotence 3) Distributivité

4) Complémentation 4) Absorption

5) Involution 5) Dualité

OR AND

DR

OR AND

Propriétés d’absorption

A+(A.B)= ?

A.(A+B)= ?

Distributivité de la somme et du produit logique

Les opérations « somme logique » et « produit logique » sont distributive l’une par

rapport à l’autre :

Distributivité du produit par rapport à la somme : P/S

P/S A.(B+C)= (A.B)+(A.C) : Admissible aussi en algèbre classique

Distributivité de la somme par rapport au produit : S/P

S/P A+(B.C)=(A+B).(A+C) : inadmissible en algèbre classique

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 3

III.3. ETUDE DES PORTES LOGIQUES

L’opérateur de base de tout circuit numérique est la porte logique. C’est un

circuit, représenté par un symbole, qui exprime une relation d’opération entre ses entrées.

Il existe plusieurs normes de représentation des symboles des portes logiques : la norme

US (américaine) et la norme internationale CEI (commission électrotechnique

internationale), etc.

3.3.1. PORTE « NOT »

La porte NOT (porte ET) est un opérateur logique de l’algèbre de Boole qui a une

seule entrée et une seule sortie. Elle matérialise l’opération INVERSION.

Elle fait passer, la variable binaire à laquelle on l’applique, d’un état logique à un autre.

Cette porte correspond à un Interrupteur ou à un bouton poussoir en position

normalement fermée.

Son chronogramme des signaux est :

Propriétés :

Exemple de circuit intégré pour l’inverseur : 74LS06

Ce numéro peut être décomposé en trois parties.

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 4

74 : Numéro de la série pour la technologie TTL (Transistor Transistor Logic).

LS : Indication de la technologie utilisée : transistor Schottky faible consommation.

6 : Numéro indiquant le contenu de l’IC: 6 inverseurs avec le brochage suivant :

La broche 7 : doit être reliée à la masse électrique GND (Ground, terre, 0 V).

La broche 14 : doit être reliée au VCC, soit +5 V pour la série 76xxxx.

3.3.2. PORTE « OR » (OU inclusif)

La porte « OR » est un opérateur booléen qui matérialise l’opération somme logique

(addition). Elle s’effectue au moins sur 2 variables. La sortie La sortie « S » est au

niveau « 1 », lorsque l’une des variables d’entrée est à « 1 »

Notation : S= A+B ou S = A U B

Cette porte correspond à deux Interrupteurs ou boutons poussoirs en position

normalement ouverts alimentant une lampe électrique en dérivation (mise en

parallèle).

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 5

Application :

Le CI 7432 qui fait partie de la série des circuits

intégrés 7400 utilisant la technique TTL.

Ce circuit est composé de quatre portes logiques

« OR » indépendantes.

Les couples (1,2), (4,5), (9,10), (12,13)

représentent les entrées respectives des sorties 3,

6, 8 et 11.

La broche 14 représente la tension

d’alimentation (+Vcc) et la broche 7 la masse

électrique (GND).

3.3.3. PORTE « AND » (ET)

La porte logique « AND » est un opérateur booléen à plusieurs entrées et/ou sorties,

elle matérialise l’opération produit logique (multiplication).

Cette opération s’effectue au moins sur 2 variables

logiques. La sortie est dans l’état « 1 » si et

seulement si toutes les variables d’entrée sont

dans l’état « 1 ».

On note : S= A.B ou S = AՈB

Cette porte correspond à deux Interrupteurs ou boutons poussoirs en position

normalement ouverts alimentant une lampe électrique en série (mise en cascade).

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 6

Exemple de circuit intégré pour la porte AND : CD4081BE ou 74LS08

EXERCICE

Trouver la table de vérité et le logigramme de ce diagramme équivalent au circuit électrique ci-

dessous :

Interrupteurs : variables

booléennes d’entrées

Lampes : fonctions de sortie :

L1= f (A, B, C, D)

L2= f (E, F)

3.3.4. PORTE « XOR » (OU Exclusif)

La porte logique « XOR » est un opérateur booléen à plusieurs entrées et/ou sorties,

elle matérialise l’opération disjonction logique (dilemme ou la différence).

Cette opération s’effectue au moins sur 2 variables logiques. La sortie est activée à

l’état « 1 » si une seule des entrées est à l’état 1 et l’autre est l’état 0. Pas les 2

simultanément.

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 7

Cette opération s’effectue au moins sur 2

variables logiques. La sortie est activée à

l’état « 1 » si une seule des entrées est à

l’état 1 et l’autre est l’état 0. Pas les 2

simultanément.

A XOR B = A B= (A+B).(A.B)=A.B+A.B

Généralisation de la fonction XOR (OU-Exclusif)

La sortie de la fonction XOR prend l’état

logique « 1 » si un nombre impair des variables

logiques d’entrée est à l’état logique « 1 ».

3.3.5. PORTES DERIVEES

Outre que les portes logiques de base, il existe des portes dérivées appelées portes

logiques universelles telles que les portes NAND (NON ET) et NOR (NON OU).

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 8

Porte NAND (Non ET)

C’est une opération inverse de produit logique.

La sortie est à 1 si l’une des variables logiques

d’entrée est au moins à 0

Pour la porte NAND à 3 entrées on trouve :

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 9

Porte NOR (Non OU = Ni)

Elle est équivalente à une porte logique « OR » suivie d’un inverseur (NOT).

Il s’agit principalement de l’inversion

d’une somme logique (porte OR). Si

toutes les variables logiques en entrée

sont à « 0 », la sortie est au niveau

« 1 ».

Pour la porte NOR à 3 entrées on trouve :

PORTE « YES » (Identité)

C’est l’inverse de la porte « NOT » ; l’Etat de sortie est le même que celui d’entrée.

Elle sert à la compatibilité de charge entre 2 fonctions ; aussi comme dispositif à retard

ou comme un préamplificateur ou encore comme un adaptateur d’impédance

Fonction assimilée à un interrupteur ou à un bouton poussoir normalement ouvert.

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 10

Porte XNOR (NON OU Exclusif)

L’équivalence (EQV) ou Coïncidence est vraie si les 2 entrées ont le même état logique

et fausse si non. Elle est matérialisée par la porte « XNOR ». C’est l’inversion du « OU

exclusif »

Notation : A EQV B = A B= A B = A.B + A.B

VARIABLES FONCTION La porte XNOR ou NON-OU EXCLUSIF a un

D’ENTREE DE SORTIE fonctionnement exactement opposé à celui de la porte

XOR

A B S= A B

0 0 1

0 1 0

1 0 0

1 1 1

Porte IMPLICATION

Dans l’opération implication, la sortie est à 1 lorsque :

- La première entrée est à « 0 »

- La première entrée est à « 1 », toutes les autres sorites doivent être à « 1 »

également :

- Si les 2 variables ont la même valeur.

- Si la 2ème variable est à « 1 » sinon la

sortie est à « 0 ».

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 11

EXERCICE

1-Déterminer la TV, l’équation logique et le logigramme correspondant au schéma

électrique du montage ci-dessous :

2-Réaliser la fonction « NAND » à trois entrées à l’aide des opérateurs « NAND » à

deux entrées ?

3-Déterminer les équations logiques des fonctions de sortie à partir des logigrammes

ci-dessous :

a)

b)

4- Construire des logigrammes des équations logiques ci-dessous :

5- Développer un logigramme muni de 4 variables d’entrée qui donnera une sortie

égale à « 1 » si et seulement si lorsqu’uniquement 3 variables d’entrée sont égales à

«1»

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 12

III.4. THEOREMES ET METHODES DE SIMPLIFICATION

EN ALGEBRE DE BOOLE

3.4.1. Théorème de DeMorgan

Pour effectuer tout calcul Booléen, on utilise, en plus des propriétés, un ensemble de

théorèmes et des méthodes. Ce sont des règles qu'on utilise pour simplifier les

expressions logiques et, par le fait même, les circuits logiques :

NEGATION DE LA SOMME : le complément ou l’inverse d’une somme logique

est égale au produit des compléments (inverses) des termes de la somme.

NEGATION DU PRODUIT : le complément ou l’inverse d’un produit logique est

égale à la somme des compléments (inverses) des termes du produit.

3.4.2. Autres méthodes de simplification

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 13

3.4.3. Universalité des portes NAND et des portes NOR

Toutes les portes logiques de base (AND, OR, NOT) peuvent être réalisées avec des

portes NOR (Non OU) et NAND (Non ET), grâce au théorème de DeMorgan.

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 14

III.5. FORMES GRAPHIQUES DE L’ALGEBRE DE BOOLE

Les règles et propriétés de l’algèbre de Boole permettent de simplifier les

fonctions mais reste une méthode relativement lourde. Elle ne permet jamais de savoir

si l’on aboutit ou pas à une expression minimale de la fonction.

La simplification algébrique des équations booléennes n'est pas toujours

évidente et demande de l'intuition. A l'inverse, les méthodes graphiques ou

géométriques permettent de mettre en évidence les monômes adjacents à l'aide d'un

tableau sans difficulté.

Le but essentiel de ces formes consiste à la minimisation sans tâtonnement d’une

expression booléenne ; il en existe trois formes :

Cercle d’Euler

Tableaux de Karnaugh

Tableaux de Veitch, etc.

3.5.1. Diagramme d’Euler

La méthode consiste en la représentation d’une expression booléenne des variables

logiques par une surface circulaire.

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 15

3.5.2. TABLEAU DE KARNAUGH

Principes

La méthode de cercle d’Euler devient mal commode d’emploi au-delà de 3 variables

logiques; il faut donc le remplacer par un autre système graphique :

Tableau de KARNAUGH jusqu’à 4 à 5 variables ;

Tableau de VEITCH même au-delà de 6 variables.

La méthode du tableau de KARNAUGH permet de visualiser une fonction et d’en tirer

intuitivement une fonction simplifiée. L’élément de base de cette méthode est une

table formée par des lignes et des colonnes

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 16

Règles d’utilisation du tableau de Karnaugh

a) Remplir les cases du tableau par les termes correspondants de la fonction à

simplifier donnée.

b) Grouper les cases symétriques des « 1 » par puissance de 2 (càd 21 22 23 24 …)

en prenant toujours le plus grand nombre possible des cases.

c) Les variables qui changent d’états dans un groupement sont éliminées du terme

considéré donné par ce groupement.

d) La fonction simplifiée sera tirée par la somme des termes issues des

groupements réalisés.

Construction des tableaux de Karnaugh

a) Remplissage du tableau de

Karnaugh pour la TV ci-contre :

b) Groupement des cases symétriques des « 1 » par puissance de 2 (càd 21 22 23 24 …) en

prenant toujours le plus grand nombre possible des cases.

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 17

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

III- 18

EXERCICES

1. Déterminer l’expression de la fonction de sortie après simplification par la méthode de

Karnaugh et élaborer son logigramme

2. A partir de cette table de vérité, appliquer, la méthode de Karnaugh pour déterminer

l’expression de la fonction de sortie et élaborer son logigramme ?

3.

4. Soit les tables de vérité ci-dessous, à l’aide de diagramme de Karnaugh :

a) Réduire et déterminer l’expression de la fonction de sortie ?

b) Elaborer le logigramme de cette expression réduite ?

** ** *

Msc. Ir. KAPULULA MUMBA Dubois Circuits Logiques Numériques UPL_2023-2024

Notes de Cours

Vous aimerez peut-être aussi

- SN1 Chapitre3 Algèbre de Bolole Portes Logiques PDFDocument12 pagesSN1 Chapitre3 Algèbre de Bolole Portes Logiques PDFRamzi DaanounePas encore d'évaluation

- Séquence 3 - Fonctions Logiques Et Algèbre BooléenneDocument11 pagesSéquence 3 - Fonctions Logiques Et Algèbre BooléenneadgjeannePas encore d'évaluation

- Les Circuits Combinatoires Et SéquentielsDocument19 pagesLes Circuits Combinatoires Et SéquentielsADAMA HADJA ALIPas encore d'évaluation

- Chapitre 2 - Cours - s6Document67 pagesChapitre 2 - Cours - s6iuyhukyPas encore d'évaluation

- Chapitre 3Document18 pagesChapitre 3Wissem BaharPas encore d'évaluation

- TP Logique 1Document6 pagesTP Logique 1ÀBdô Rahmên100% (1)

- Algebre de Bool PDFDocument21 pagesAlgebre de Bool PDFgargield63Pas encore d'évaluation

- 2-ELECTRONIQUE NUMERIQUE - Fonctions Et Opérateurs LogiquesDocument36 pages2-ELECTRONIQUE NUMERIQUE - Fonctions Et Opérateurs Logiquesziko9172Pas encore d'évaluation

- Chapitre 3Document56 pagesChapitre 3ismail.moussa100% (1)

- Synthese Logique 18 09 12Document19 pagesSynthese Logique 18 09 12AnasBtPas encore d'évaluation

- TP LCS Énoncés PDFDocument11 pagesTP LCS Énoncés PDFamine sariahmedPas encore d'évaluation

- Chapitre - 03 ElectroniqueDocument9 pagesChapitre - 03 Electroniqueassad4894Pas encore d'évaluation

- Chap 2 s6Document70 pagesChap 2 s6Imad ImadPas encore d'évaluation

- Cours 3 Circuits Logiques Par6Document16 pagesCours 3 Circuits Logiques Par6Philippe KANYIMBUPas encore d'évaluation

- Chapitre 2 1 Corr V2 13Document11 pagesChapitre 2 1 Corr V2 13justicedark6Pas encore d'évaluation

- Initiation ChapitreDocument4 pagesInitiation ChapitreMoussa SanogoPas encore d'évaluation

- Initiation ChapitreDocument4 pagesInitiation ChapitreMoussa SanogoPas encore d'évaluation

- Chapitre1 GMPDocument10 pagesChapitre1 GMPSALEHPas encore d'évaluation

- Main PolycopieDocument50 pagesMain PolycopieRachid BendaoudPas encore d'évaluation

- Cours Algebre Boole GL1 AKWA-1Document15 pagesCours Algebre Boole GL1 AKWA-1oumar cissePas encore d'évaluation

- Electronique Numérique-SMP-S6 Seance 2Document28 pagesElectronique Numérique-SMP-S6 Seance 2imanemaster5Pas encore d'évaluation

- 12-Algebre de BooleDocument6 pages12-Algebre de BooleYu XinPas encore d'évaluation

- DownloadDocument36 pagesDownloadRochdi EngenierPas encore d'évaluation

- Cours Architecture Ordinateurs Chapitre4Document15 pagesCours Architecture Ordinateurs Chapitre4Will AzanguePas encore d'évaluation

- Cours Alg..Document10 pagesCours Alg..Laila LwazaniPas encore d'évaluation

- Algebre de BooleDocument6 pagesAlgebre de BooleBabacar TounkaraPas encore d'évaluation

- TP PDFDocument28 pagesTP PDFAhmed HasbellaouiPas encore d'évaluation

- Les Systemes Logiques ch2Document29 pagesLes Systemes Logiques ch2chourouk hlaouiPas encore d'évaluation

- Cours SL 1 Logique CombinatoireDocument8 pagesCours SL 1 Logique CombinatoireAbdelhadi AZPas encore d'évaluation

- Cours Logique CombinatoireDocument86 pagesCours Logique CombinatoirecisaPas encore d'évaluation

- Livre Tse QuenDocument76 pagesLivre Tse Quenmaitriza09100% (1)

- Cours Dautomatismes 1er Annee Chapitre 2Document37 pagesCours Dautomatismes 1er Annee Chapitre 2Baha JgPas encore d'évaluation

- 3-Les Bases de La Logique BinaireDocument11 pages3-Les Bases de La Logique BinaireJulien THYSPas encore d'évaluation

- Page de GardeDocument7 pagesPage de Gardemustaphakaouci7Pas encore d'évaluation

- CIRCUITS LOGIQUES Bases PDFDocument8 pagesCIRCUITS LOGIQUES Bases PDFyoussefkhairanePas encore d'évaluation

- 7 MathématiquesDocument21 pages7 MathématiquesMouilhi MouilhiPas encore d'évaluation

- Les Fonctions LogiquesDocument4 pagesLes Fonctions LogiquesBsss GghhhPas encore d'évaluation

- 2 - Les Fonctions BinairesDocument3 pages2 - Les Fonctions BinairesRomualdPas encore d'évaluation

- CH 3 Struct Machine 1Document20 pagesCH 3 Struct Machine 1C00LiMoUnPas encore d'évaluation

- Chapitre II Algebre de BooleDocument11 pagesChapitre II Algebre de BooleHyacinthe KOSSIPas encore d'évaluation

- LogiqueDocument9 pagesLogiqueram frPas encore d'évaluation

- AlgebrebooleDocument75 pagesAlgebrebooleSalimDeepSidePas encore d'évaluation

- Chap 2 Algebre de Boole Et Fonctions LogiquesDocument20 pagesChap 2 Algebre de Boole Et Fonctions Logiquessaidibrahim042004Pas encore d'évaluation

- Cours Electronique de Base 5 6Document30 pagesCours Electronique de Base 5 6Allen AymericPas encore d'évaluation

- Algebre de BouleDocument25 pagesAlgebre de BouleMindofdjib SnowPas encore d'évaluation

- Portes Logiques Et Algebre de BooleDocument27 pagesPortes Logiques Et Algebre de Boolejustinngani03Pas encore d'évaluation

- AlgebrebooleDocument79 pagesAlgebrebooleEl Amrani LailaPas encore d'évaluation

- E2 - Electronique LogiqueDocument10 pagesE2 - Electronique LogiqueLeto Van Ruymbeke (OrpiGudyypresent)Pas encore d'évaluation

- 04-2-Fonctions de Logique CombinatoireDocument14 pages04-2-Fonctions de Logique CombinatoireFosseni DialloPas encore d'évaluation

- ELE3311 Ch01Document38 pagesELE3311 Ch01Smart ClassePas encore d'évaluation

- 1 - Fonctions de Logique CombinatoireDocument14 pages1 - Fonctions de Logique CombinatoireYohan RIPOLLPas encore d'évaluation

- Portes Logiques Et Algèbre de BooleDocument26 pagesPortes Logiques Et Algèbre de BooleKhalil SowPas encore d'évaluation

- Chapitre 3 Structure 1Document8 pagesChapitre 3 Structure 1imedbnk23Pas encore d'évaluation

- Logique Combinatoire V PDocument9 pagesLogique Combinatoire V PIbrahima DiarraPas encore d'évaluation

- chp06strmch GuezouliDocument12 pageschp06strmch GuezouliAugustin Tadiamba PambiPas encore d'évaluation

- TP1 LogiqueDocument12 pagesTP1 LogiqueŘî Æđ100% (1)

- Le BossDocument10 pagesLe Bosslebossivan7Pas encore d'évaluation

- Transistors Vers Portes LogiquesDocument7 pagesTransistors Vers Portes LogiquesTom Tuan Kiet HOANGPas encore d'évaluation

- Chapitre 4 ElectroniqueDocument45 pagesChapitre 4 ElectroniqueimanesaidytPas encore d'évaluation

- Drive IP5A LS, 150kwDocument110 pagesDrive IP5A LS, 150kwALI BenkassaPas encore d'évaluation

- CCTP Postes MTDocument27 pagesCCTP Postes MTSakji BéchirPas encore d'évaluation

- Compte Rendu: TP N°5 Analyse, Filtrage Et Acquisition Des Signaux Analogiques Base de La Carte D'instrumentation ELVIS IIDocument5 pagesCompte Rendu: TP N°5 Analyse, Filtrage Et Acquisition Des Signaux Analogiques Base de La Carte D'instrumentation ELVIS IIimane elghchachPas encore d'évaluation

- Calculateur Automatique de - Panneau Solaire, Batterie, Régulateur Et de L'onduleurDocument1 pageCalculateur Automatique de - Panneau Solaire, Batterie, Régulateur Et de L'onduleurMProd Ammo100% (1)

- Batterie de CondensateursDocument49 pagesBatterie de CondensateursrahemPas encore d'évaluation

- Cours ENSEM MesbahiDocument102 pagesCours ENSEM Mesbahifatima-zohra50% (2)

- QCM TechnoDocument15 pagesQCM Technoabdoulazizda42Pas encore d'évaluation

- Programmes D'études de 4ème A ELEQDocument11 pagesProgrammes D'études de 4ème A ELEQNtepp Jean Bosco De La Grâce100% (3)

- CB Groupe-Ozman 2Document2 pagesCB Groupe-Ozman 2yaya sowPas encore d'évaluation

- Fonction FusibleDocument3 pagesFonction Fusiblethe eye patche (aymen djerioui)Pas encore d'évaluation

- TD3 DIC2-Capteurs PDFDocument5 pagesTD3 DIC2-Capteurs PDFsidiPas encore d'évaluation

- Conception Et Realisation D - Un Prototype Smart HomeDocument80 pagesConception Et Realisation D - Un Prototype Smart HomeRodrigue OuedraogoPas encore d'évaluation

- 1 Cours Diode 2021Document62 pages1 Cours Diode 2021is lam100% (1)

- Projet Voiture MatlabDocument19 pagesProjet Voiture MatlabSanhouidi Stephane0% (1)

- Formation RobotiqueDocument15 pagesFormation Robotiqueattiahiba7Pas encore d'évaluation

- Em100tft PDFDocument2 pagesEm100tft PDFAlae DakkakPas encore d'évaluation

- Cna & CanDocument15 pagesCna & CanAk ramPas encore d'évaluation

- AFH - Agence Foncière D'habitation - Recu Demande D'acquisition D'un Lot de TerrainDocument1 pageAFH - Agence Foncière D'habitation - Recu Demande D'acquisition D'un Lot de TerrainMajdi JerbiPas encore d'évaluation

- 63b6dd5b85787 - 02 - ما فاتك شئ - Ampli Linéaires - Devoir n°1 - 2022 - Sé - CoDocument11 pages63b6dd5b85787 - 02 - ما فاتك شئ - Ampli Linéaires - Devoir n°1 - 2022 - Sé - CoBraiki EyaPas encore d'évaluation

- S3.les Generateurs D Energie ElectriqueDocument2 pagesS3.les Generateurs D Energie ElectriqueOussama MabroukPas encore d'évaluation

- Onduleur TriphaséDocument22 pagesOnduleur TriphaséRim Ben RziguePas encore d'évaluation

- Oscillateurs Et Radio Cours - Projection - MASSONDocument276 pagesOscillateurs Et Radio Cours - Projection - MASSONLotfi Haitam100% (1)

- Chapitre 1. Courant Électrique Et Circuit Électrique SimpleDocument5 pagesChapitre 1. Courant Électrique Et Circuit Électrique SimpleELLANI HatemPas encore d'évaluation

- 8979 Epreuve E2 Bac Pro Sen Asi Corrige VFDocument28 pages8979 Epreuve E2 Bac Pro Sen Asi Corrige VFMouad ElmekaouiPas encore d'évaluation

- Les Capteurs de TempératureDocument7 pagesLes Capteurs de TempératureChahre Eddine100% (2)

- BU Notice Moteurs RGDocument29 pagesBU Notice Moteurs RGAngeloPas encore d'évaluation

- Résumé Cours Tech Commande ElecDocument16 pagesRésumé Cours Tech Commande ElecHassan AbushwarebPas encore d'évaluation

- Cours Info1 SIDocument42 pagesCours Info1 SIgredelfarellangouPas encore d'évaluation

- Compte Rendu TP HacheursDocument8 pagesCompte Rendu TP HacheursLemjid YesminePas encore d'évaluation