Académique Documents

Professionnel Documents

Culture Documents

Cours Up Beguenane 8

Transféré par

zied houanebTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cours Up Beguenane 8

Transféré par

zied houanebDroits d'auteur :

Formats disponibles

1/ 15

Chapitre 8 : Le circuit Minuterie ou

‘Timer’ 8253/54

Section 8.1: Description du circuit Timer 8253/54 et

Initialisation

Section 8.2: Programmation du Timer 8253/54 et

interface avec IBM PC

Section 8.3: La forme des signaux de sorties du

Timer 8253/54

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

2/ 15

Objectives

Les objectifs de ce chapitre sont:

- Décrire la fonction de chaque PIN du circuit Timer

8253/54.

- Savoir programmer les 3 compteurs du circuit Timer

8253/54.

- Montrer comment le circuit Timer 8253/54 est connecté

au IBM PC.

- Expliquer les différents modes pour générer le signal

de sortie du Timer 8253/54.

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

3/ 15

Section 8.1: Description du circuit Timer

8253/54 et Initialisation

Pourquoi le Circuit Timer?

Dans un PC il existe une seule horloge (CLK) de très haute fréquence, utilisée notamment par la

CPU, pour synchroniser ses activités avec ses circuits périphériques.

Mais dans un PC il existe des fonctions qui nécessitent des horloges de basse fréquence.

Le Timer 8253/54 PIT (Programmable Interval Timer) est conçu pour satisfaire ce besoin. Il

consiste à générer des basses fréquences à partir de CLK pour des applications diverses comme

jouer de la musique par exemple.

IBM PC/XT (P8088) Timer 8253

IBM PC/AT (P80286) Timer 8254 (il accepte les programmes du Timer 8253)

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

4/ 15

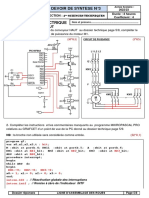

Description du circuit Timer 8253/54 et Initialisation

D7 1 24 VCC CLK0

D6 2 WR GATE0

D5 RD D7 .. D0 OUT0

D4

D3

CS

A1

CLK2

D2

D1

8253 A0

CLK2

P WR

RD

8253 GATE2

OUT2

I/F

D0 OUT2

CLK0 GATE2 CLK1

OUT0 CLK1 A0 GATE1

GATE0 GATE1

A1 OUT1

GND 12 13 OUT1

CS

Circuit Timer 8253

(Même chose que le 8254) CS A1 A0 Port

CLK (1,2,3) <= 2 MHz sinon avec Timer 8254 (jusqu’à 10MHz) 0 0 0 Compteur 0

0 0 1 Compteur 1

La forme du signal OUT (CLK / N) est programmée

0 1 0 Compteur 2

Le signal GATE est utilisé pour (Dés)Activer le compteur. 0 1 1 Registre de Contrôle

État Haut (5V) pour activer et vice-versa. 1 x x 8253/54 n’est pas sélectionné

Le bus données du 8253 D0-D7 est connecté à celui du bus système. Il Les signaux RD/WR sont connectés aux

permet à la CPU d’accéder les registres du 8253 pour les opérations L/E. signaux de contrôle IOR/IOW du bus système.

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

5/ 15

Description du circuit Timer 8253/54 et Initialisation

Initialisation du T8253/54

Les 3 compteurs doivent être programmés séparément. Pour programmer un compteur :

- L’octet de contrôle est écrit dans le registre contrôle (pour, entre autres, indiquer la forme de OUT).

- Le nombre N par qui la CLK est divisée pour générer la fréquence OUT, doit être programmé, via

D7-D0. Puisque le nombre maximum permis est FFFFh (16 bits), ce nombre doit être envoyé en 2

temps, 1 octet à la fois.

D7 D6 ...... D1 D0 BCD Mode

SC1 SC0 RL1 RL0 M2 M1 M0 BCD 0 Compteur Binaire (16-bits)

1 Compteur BCD (4 décades)

Registre de contrôle

M2 M1 M0 Mode

0 0 0 Mode 0

RL1 RL0 Mode SC1 SC0 Mode

0 0 1 Mode 1

0 0 Lecture du compteur (compteur 0 0 Compteur 0 sélectionné

x 1 0 Mode 2 d’avènement)

0 1 Compteur 1 sélectionné

Mode 3 0 1 Lire/Charger LSB seulement

x 1 1 Compteur 2 sélectionné

1 0

Mode 4 1 0 Lire/Charger MSB seulement

1 0 0 / (non permis)

1 1

Mode 5 1 1 Lire/Charger LSB, ensuite MSB

1 0 1

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

6/ 15

Description du circuit Timer 8253/54 et Initialisation

Binaire: 0000 FFFFh CLK / [ 1 (0001h) à 65536 (0000h)]

D7 D6 ...... D1 D0

SC1 SC0 RL1 RL0 M2 M1 M0 BCD

BCD:Registre de contrôle

0000 9999h CLK / [ 1 (0001h) à 10000 (0000h)]

Mode 0 Interruption au compte final

Mode 1 ProgrammableD6 pulse (une seule fois)

...... D0

D7 D1

Mode 2 Générateur de pulses périodiques

SC1 SC0 carré

Mode 3 Générateur signal

RL1 RL0 M2 M1 M0 BCD

Mode 4 Déclenchement

Registre de Logiciel

contrôle

Mode 5 Déclenchement Hardware

Il y’a 3 options possibles, lire

Le nombre qui divise D7la CLK

D6 le MSB, ou LSB, D1ou bienD0

est sur 16-bits (0000FFFFh) les deux (le LSB en premier lieu).

SC1 SC0

RL0 et RL1 sont utilisés pour

RL1 RL0 M2 M1 M0 BCD

La 4eme option est la lecture du

Indiquer la taille de ce nombre. contenu du compteur à n’importe quel

moment.

D7 D6 Ces bits indiquent lequel D1 D0

des 3 compteurs (0, 1, ou 2)

SC1 SC0 RL1 RL0 M2l’octet

est à initialiser par

M1de M0 BCD

contrôle.

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

7/ 15

Description du circuit Timer 8253/54 et Initialisation

Exemple Supposant que la puce 8253/54 est activée par le pin CS à partir des adresses A7-A2 100101.

Dans ce cas Les adresses des ports assignés au T8253/54, sont:

CS A1A0 Port Adresse du port (Hex)

100101 00 Compteur 0 94

100101 01 Compteur 1 95

100101 10 Compteur 2 96

100101 11 Registre de Contrôle 97

Si le registre de contrôle est programmée comme suit:

MOV AL, 36H

OUT 97H, AL

La configuration du T8253/54 est comme suit:

36H = 00110110B

CS0,1= 00 Compteur 0 sélectionné Les 3 compteurs partagent

C’est quoi ce le registre de contrôle mais

RL0,1= 11 LSB est suivi de MSB Nombre diviseur? chacun possède son registre

diviseur (dont l’adresse du

M0,1,2= 110 Mode 3 sélectionné (signal carré) port est celle du compteur

en question).

BCD = 0 Compteur Binaire

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

8/ 15

Description du circuit Timer 8253/54 et Initialisation

Port Adr. Port

Exemple 2 En utilisant les adresses des ports (de l’exemple 1)

Compteur 0 94h

Programmer le compteur 0, dont la fréquence

est CLK0/4282(en BCD) et la forme d’onde est un Compteur 1 95h

Signal carrée (Mode 3). Compteur 2 96h

Registre de 97h

MOV AL, 37H ; Compteur 0, mode 3, BCD 37H Contrôle

OUT 97H, AL ; Envoi au registre contrôle

MOV AX, 4282H ; Charger le nombre diviseur (H pour HEX)

OUT 94h, AL ; Envoi de l’octet LSB au port compteur 0 (82h)

MOV AL, AH

OUT 94h, AL ; Envoi de l’octet MSB au port compteur 0 (42h)

Programmer le compteur 2, qui permet de générer un signal carré de fréquence f OUT2 = 360Hz, sachant

que fCLK2 = 1.8MHz.

MOV AL, B6H ; Compteur 2, mode 3, Binaire B6H

fCLK2 / fOUT2 = 5000 = 1388H (HEX) OUT 97H, AL ; Envoi au registre contrôle

En Binaire

MOV AX, 1388H ; Charger le nombre diviseur (H pour HEX)

= 5000 (BCD) OUT 96h, AL ; Envoi de l’octet LSB au compteur 2 (88h)

MOV AL, AH

Note: En BCD, il suffit de changer

OUT 96h, AL ; Envoi de l’octet MSB au compteur 2 (13h)

MOV AL, B6H par

MOV AL, B7H

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

9/ 15

Section 8.2: Programmation du Timer

8253/54 et interface avec IBM PC

Adresse Compteur0,1,2 = 40H/41/42 Adresse Reg. Controle = 43H

(+haute priorité) le Timer0 est programmée

P LS138 à 0000H 8259

CS A1 A0

8 A5 A CLK0 18.5 Hz interruption TOD (IBM BIOS) IRQ0

OUT0

0 B

C Y2 Vcc GATE0

8 G2B Vcc

8 A9 G2A Compteurs 0 et 1 15 s Rafraîchir DRAMs DREQ0

AEN G1 Activés en OUT1 FF DMA

permanence

DACK 8237

CLK1

Vcc GATE1

8253 Vers le lecteur de cassettes

OUT2

IBM PC Son Beep (897Hz)

Ou bien Musique

1.193 MHz < 2 CLK2

8284 GATE2

FF

Ecouteur EN

PCLK Vers les Ecouteurs

2.383MHz

(1/2 CLK)

Port

PB1

Data

PB0

8255 PPI PC5

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

10/ 15

Section 8.3: La forme des signaux de sorties

du Timer 8253/54

Formes de OUT0, 1, 2

IBM PC a programmé le compteur 0 du Timer8253/54 en mode 3 (signal carré) avec le nombre

maximum 65536 (donc son registre est chargé avec la valeur 0000H), pour obtenir une fréquence de

18.2Hz. Puisque le nombre à charger est pair (65536) le rapport cyclique de OUT0 est de 50% .

1.193MHz TCLK0 = 838ns

CLK0 =

CLK1 =

CLK2

OUT0

18.2Hz Tout0 = 838ns x 65536

IBM PC a programmé le compteur 1 du Timer8253/54 en mode 2 (Générateur de pulses) avec le

nombre 18 (donc son registre est chargé avec la valeur 12H), pour obtenir une fréquence de 66278Hz.

OUT1 reste haut pendant 17 périodes de CLK et s’annule pendant la dernière pulsation.

OUT1

66.278Hz Tout0 = 838ns x 18

IBM PC a programmé le compteur 2 du Timer8253/54 en mode 3 (signal carré) avec le nombre 1331

(donc son registre est chargé avec la valeur 0533H), pour obtenir une fréquence de 896Hz. Puisque le

nombre à charger est impair (1331) le rapport cyclique de OUT0 n’est pas 50% (N+1)/2 pulses à

l’état haut et (N-1)/2 pulses à l’état bas.

OUT2

896Hz Tout0 = 838ns x 1331

11/ 15

La forme des signaux de sorties du Timer 8253/54

Modes d’Opérations du Timer 8253/54

Que s’il y’a un nouveau N ou

MODE 0 : Interruption au compte final Un nouveau Octet de contrôle

A condition GATE = 1

N x TCLK

GATE

X

A condition Gate = 1

OUT

N x TCLK + X

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

12/ 15

La forme des signaux de sorties du Timer 8253/54

MODE 1 : Programmable pulse (1 seule fois) Hardware Triggerable One-Shot

Charger le compteur ENSUITE

GATE

GATE

OUT

N x TCLK

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

13/ 15

La forme des signaux de sorties du Timer 8253/54

MODE 2 : Générateur de pulses (Rate Generator) Charger le compteur de N

A condition GATE = 1

OUT

N x TCLK

1 x TCLK

MODE 3 : Générateur d’un signal carré Charger le compteur de N

A condition GATE = 1

OUT

N/2 x TCLK N/2 x TCLK

Ou bien (N+1)/2 x TCLK (N-1)/2 x TCLK

Si N est

impair

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

14/15

La forme des signaux de sorties du Timer 8253/54

MODE 4 : Programmable pulse par logiciel Software Triggerable Strobe

Charger le compteur de N

A condition GATE = 1

OUT

N x TCLK

1 x TCLK

Note: Ce mode est semblable au Mode 2, seulement Que si le compteur

est chargé à nouveau de N

Ou

Un nouveau Octet de contrôle

est programmé

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

15/ 15

La forme des signaux de sorties du Timer 8253/54

MODE 5 : Programmable pulse par Hardware Hardware Triggerable Strobe (par GATE)

Charger le compteur de N

GATE

OUT

N x TCLK

1 x TCLK

R. Beguenane, UQAC, 2002/2003 Systèmes à microprocesseurs

Vous aimerez peut-être aussi

- Cour 2 Microprocesseur Et Dsp-1Document14 pagesCour 2 Microprocesseur Et Dsp-1Kam ZegPas encore d'évaluation

- Microprocesseurs-Technologie Sem1 2014 Ii2Document3 pagesMicroprocesseurs-Technologie Sem1 2014 Ii2arnaud tchouaniPas encore d'évaluation

- Chap 1 LaDocument15 pagesChap 1 LaAyella Ôë0% (1)

- TD CiDocument17 pagesTD CikoyabePas encore d'évaluation

- (Elec) Elek - DeLPHI Pour Électroniciens 02-10Document4 pages(Elec) Elek - DeLPHI Pour Électroniciens 02-10Madidj_20140% (1)

- Cours Up Beguenane 5Document16 pagesCours Up Beguenane 5zied houanebPas encore d'évaluation

- Unité3Document19 pagesUnité3Emilio del RioPas encore d'évaluation

- Devoir de Synthèse N°1 2011 2012 (Taher Elhaded El Hamma)Document5 pagesDevoir de Synthèse N°1 2011 2012 (Taher Elhaded El Hamma)Youssef CherniPas encore d'évaluation

- Micro-Controleur C51 Support Complet Et TPDocument78 pagesMicro-Controleur C51 Support Complet Et TPSeddik MaarfiPas encore d'évaluation

- Gigabyte Gab75d3v Rev 11Document34 pagesGigabyte Gab75d3v Rev 11diem chauPas encore d'évaluation

- SondeDocument5 pagesSondekaragaine100% (1)

- Bac 2015Document14 pagesBac 2015Junior JuniorPas encore d'évaluation

- Sujet 0Document13 pagesSujet 0YoussefPas encore d'évaluation

- Cfmoti - Ista Ntic - Net - TRI 2015 Fin Formation ThéoriqueDocument11 pagesCfmoti - Ista Ntic - Net - TRI 2015 Fin Formation ThéoriqueEl Amrani LailaPas encore d'évaluation

- Devoir de Synthèse N°1 - Génie Mécanique Cellule Flexible - 3ème Technique (2011-2012) MR Hamdi DTDocument5 pagesDevoir de Synthèse N°1 - Génie Mécanique Cellule Flexible - 3ème Technique (2011-2012) MR Hamdi DTYoussef CherniPas encore d'évaluation

- Logique Séquentielle: Compteurs Intégrés AsynchronesDocument16 pagesLogique Séquentielle: Compteurs Intégrés AsynchronesbejaouiPas encore d'évaluation

- TP Fpga Cyclone2Document3 pagesTP Fpga Cyclone2red-allPas encore d'évaluation

- Microprocesseur 8086Document79 pagesMicroprocesseur 8086AMIRAFORTASPas encore d'évaluation

- DCorrigé FinalDocument4 pagesDCorrigé FinalAbdelfatteh BoukattayaPas encore d'évaluation

- Application À Base de Bascules 3emeDocument4 pagesApplication À Base de Bascules 3emeMed NasrPas encore d'évaluation

- Corigé Type Eln.-num.-Av.-fpgAVHDL M1-InST Électronique NumériqueDocument5 pagesCorigé Type Eln.-num.-Av.-fpgAVHDL M1-InST Électronique NumériqueHala SaimPas encore d'évaluation

- Regitre - Dec Ex TpfpgaDocument8 pagesRegitre - Dec Ex TpfpgaZenache AhlemPas encore d'évaluation

- Uh2C - Enset M TP M: Ohammedia IcrocontroleurDocument3 pagesUh2C - Enset M TP M: Ohammedia IcrocontroleurPaul BonlougouPas encore d'évaluation

- AbdelaaliDocument6 pagesAbdelaaliAero ClubPas encore d'évaluation

- TP3 4 Applications A Base de Circuit NE555Document9 pagesTP3 4 Applications A Base de Circuit NE555hajjiPas encore d'évaluation

- 798315.10 - Matériel Déporté MDXLDocument2 pages798315.10 - Matériel Déporté MDXLefsloug100% (1)

- Gino Aka Akamas2.0 - FRDocument6 pagesGino Aka Akamas2.0 - FRharratmoussa6Pas encore d'évaluation

- Chapitre 1 PLDDocument8 pagesChapitre 1 PLDHAMLA SIEMENCEPas encore d'évaluation

- Partie3 Microcontroleur s4 E2iDocument9 pagesPartie3 Microcontroleur s4 E2iMoha BenmohaPas encore d'évaluation

- TP N°3: Adc/Dac: I. RappelsDocument9 pagesTP N°3: Adc/Dac: I. RappelsMohamed Ali ChebbiPas encore d'évaluation

- Archi2 Chap4 PIC8259ADocument58 pagesArchi2 Chap4 PIC8259AAyoub AbdellaouiPas encore d'évaluation

- Rappel PLSQLDocument54 pagesRappel PLSQLDARSAOUIPas encore d'évaluation

- DSC2 2ste 2019 2020Document8 pagesDSC2 2ste 2019 2020ismail elmoufakirPas encore d'évaluation

- Microcontrolleur: Traiter 1Document32 pagesMicrocontrolleur: Traiter 1farrouj abdelhamidPas encore d'évaluation

- Pia 8255Document8 pagesPia 8255radn23100% (1)

- CH3 Convertisseur AnalogiqueDocument12 pagesCH3 Convertisseur AnalogiqueMohammed AbdiPas encore d'évaluation

- TD 2Document5 pagesTD 2adda chariPas encore d'évaluation

- TP Liaisons SerieDocument7 pagesTP Liaisons SerieImane SaharPas encore d'évaluation

- Arduino Timer 2Document2 pagesArduino Timer 2houdaPas encore d'évaluation

- DS1-COR-Lavage PrepayeDocument4 pagesDS1-COR-Lavage PrepayeMouad MemniPas encore d'évaluation

- Communication I2C Entre 2 PICDocument9 pagesCommunication I2C Entre 2 PICngt881Pas encore d'évaluation

- Cours ArduinoDocument100 pagesCours ArduinoAmil DhafPas encore d'évaluation

- TD N°1Document4 pagesTD N°1Sanda OumarouPas encore d'évaluation

- Travaux Dirigés-Microprocesseur MicrocontroleurDocument18 pagesTravaux Dirigés-Microprocesseur MicrocontroleurFatima BettayebPas encore d'évaluation

- Cours de Conception Et Fabrications Assistées Par OrdiDocument141 pagesCours de Conception Et Fabrications Assistées Par Ordimariereinetherese2Pas encore d'évaluation

- Intel 8051Document27 pagesIntel 8051Benkirane YounesPas encore d'évaluation

- Modulo Memoria Micron MT2LG25664KHG-Xx - DatasheetDocument16 pagesModulo Memoria Micron MT2LG25664KHG-Xx - DatasheetColectivinPas encore d'évaluation

- PIC16F877Document27 pagesPIC16F877Jamila Debaya100% (1)

- Etron Tech IC DatasheetDocument73 pagesEtron Tech IC DatasheetSyed AhmadPas encore d'évaluation

- PIECE V - C13 - Avant Poste BlindéDocument19 pagesPIECE V - C13 - Avant Poste BlindéklmPas encore d'évaluation

- 01 - Séminaire API TELEMECANIQUE - GE-FF-S01Document111 pages01 - Séminaire API TELEMECANIQUE - GE-FF-S01BOURASSPas encore d'évaluation

- 01 - Séminaire API TELEMECANIQUE - GE-FF-S01 PDFDocument111 pages01 - Séminaire API TELEMECANIQUE - GE-FF-S01 PDFLotfi ElaoudPas encore d'évaluation

- PLDsDocument6 pagesPLDsYoussef SadikPas encore d'évaluation

- TD +DOCDocument20 pagesTD +DOCAchrafPas encore d'évaluation

- ATV312 - Premium - Communication ModbusDocument5 pagesATV312 - Premium - Communication ModbusAbel AndradaPas encore d'évaluation

- Chapitre 2Document15 pagesChapitre 2bouchrahebchiPas encore d'évaluation

- Compilateur Graphique Pour Microcontrôleur MCS-51: Table Des MatièresDocument195 pagesCompilateur Graphique Pour Microcontrôleur MCS-51: Table Des Matièrespauloalves1972Pas encore d'évaluation

- Le syndrome périodique associé à la cryopyrine (CAPS)D'EverandLe syndrome périodique associé à la cryopyrine (CAPS)Pas encore d'évaluation

- TD Cours Charge I CSTDocument1 pageTD Cours Charge I CSTzied houanebPas encore d'évaluation

- CorElecE405 406Document1 pageCorElecE405 406zied houanebPas encore d'évaluation

- DL 001051 04 07.01.00Document14 pagesDL 001051 04 07.01.00zied houanebPas encore d'évaluation

- Tdec 2Document2 pagesTdec 2zied houaneb100% (1)

- TP4 Electrocinetique RLCDocument4 pagesTP4 Electrocinetique RLCNobel MponguiPas encore d'évaluation

- 7theoreme GenerauxdepotDocument7 pages7theoreme Generauxdepotzied houanebPas encore d'évaluation

- TD Sinus 2Document4 pagesTD Sinus 2zied houanebPas encore d'évaluation

- Cor Elec E511Document1 pageCor Elec E511zied houanebPas encore d'évaluation

- TD E5: Puissance en Régime Sinusoidal Forcé: Plan Prévisionnel Du ChapitreDocument4 pagesTD E5: Puissance en Régime Sinusoidal Forcé: Plan Prévisionnel Du Chapitrezied houanebPas encore d'évaluation

- ElectrostatiqueDocument64 pagesElectrostatiquesocom100% (6)

- II Filtre D'ordre 1Document5 pagesII Filtre D'ordre 1zied houanebPas encore d'évaluation

- Cours Up Beguenane 5Document16 pagesCours Up Beguenane 5zied houanebPas encore d'évaluation

- TD1 TimerDocument1 pageTD1 Timerzied houanebPas encore d'évaluation

- Cours Up Beguenane 9Document21 pagesCours Up Beguenane 9zied houanebPas encore d'évaluation

- Cours Up Beguenane 10Document23 pagesCours Up Beguenane 10zied houanebPas encore d'évaluation

- Cours Up Beguenane 8Document15 pagesCours Up Beguenane 8zied houanebPas encore d'évaluation

- Exos FCTSTD VHDL SysLog2Document3 pagesExos FCTSTD VHDL SysLog2zied houanebPas encore d'évaluation

- Interface MAX7219 Avec Affichage 7 Segments À 8 Chiffres Et PIC16F877ADocument6 pagesInterface MAX7219 Avec Affichage 7 Segments À 8 Chiffres Et PIC16F877Azied houanebPas encore d'évaluation

- B ArithmDocument147 pagesB Arithmzied houanebPas encore d'évaluation

- Cours Up Beguenane 4Document17 pagesCours Up Beguenane 4zied houanebPas encore d'évaluation

- Cours Up Beguenane 6Document27 pagesCours Up Beguenane 6zied houanebPas encore d'évaluation

- Cours Up Beguenane 3Document53 pagesCours Up Beguenane 3zied houanebPas encore d'évaluation

- Presentation BeamerDocument36 pagesPresentation Beamerzied houanebPas encore d'évaluation

- 1 ErbeamerDocument6 pages1 ErbeamerKhaled OuniPas encore d'évaluation

- AltimètreDocument22 pagesAltimètrezied houanebPas encore d'évaluation

- Abaque SmithDocument8 pagesAbaque Smithuser2014523100% (1)

- Beamer Quick StartDocument4 pagesBeamer Quick Startzied houanebPas encore d'évaluation

- Beamertalk 2Document172 pagesBeamertalk 2zied houanebPas encore d'évaluation

- AnémomètreDocument6 pagesAnémomètrezied houanebPas encore d'évaluation

- Table de Partition MBR GPTDocument3 pagesTable de Partition MBR GPTTaoufiq MerrahiPas encore d'évaluation

- Apple II PDFDocument7 pagesApple II PDFStephan LewisPas encore d'évaluation

- Exercices Commandes Ms Dos PDF CompressDocument2 pagesExercices Commandes Ms Dos PDF CompressAvahouin NicaisePas encore d'évaluation

- Chap 1 - Séance 1 - Le Boot Loader Et InitDocument28 pagesChap 1 - Séance 1 - Le Boot Loader Et InitBarra-brava BravaPas encore d'évaluation

- CH 9 - CH 18 Démarrage Du Système LinuxDocument8 pagesCH 9 - CH 18 Démarrage Du Système LinuxSalah AllouchiPas encore d'évaluation

- Chap 1 - Le Boot Loader Et Initv2 PDFDocument59 pagesChap 1 - Le Boot Loader Et Initv2 PDFAmmar Chebbi100% (1)

- Tutor YandiDocument10 pagesTutor YandiDeddyPas encore d'évaluation

- Boot Camp Guide D'installation Et de Configuration PDFDocument13 pagesBoot Camp Guide D'installation Et de Configuration PDFAlmondPas encore d'évaluation

- TP Installer Ubuntu en Dual Boot Avec WindowsDocument11 pagesTP Installer Ubuntu en Dual Boot Avec Windowshamza100% (1)

- BS DIY PricelistDocument71 pagesBS DIY PricelistHitman GroupPas encore d'évaluation

- Amstrad Mag 03Document62 pagesAmstrad Mag 03jborregoPas encore d'évaluation

- Demarrage Dun OrdinateurDocument20 pagesDemarrage Dun OrdinateurYou Ssëf CHPas encore d'évaluation

- Comment Formater Un PC Windows 7 PDFDocument2 pagesComment Formater Un PC Windows 7 PDFTiffanyPas encore d'évaluation

- Commande - PC Gamer MarocDocument1 pageCommande - PC Gamer MarocHicham El MaatiPas encore d'évaluation

- Cours Sur Le Disque DurDocument11 pagesCours Sur Le Disque DurHabib FayePas encore d'évaluation

- Procédé de Démarrage Du Système LinuxDocument4 pagesProcédé de Démarrage Du Système LinuxZeineb HoumanPas encore d'évaluation

- Cables AutomatismoDocument109 pagesCables AutomatismoGermán Walter RufanachtPas encore d'évaluation

- 2837 - Apple 02.12.21Document12 pages2837 - Apple 02.12.21khayisamPas encore d'évaluation

- Cours Dinformatique - en ArabeDocument19 pagesCours Dinformatique - en ArabeC1rt0uche123 CartouchePas encore d'évaluation

- Cours Sur Le BIOSDocument3 pagesCours Sur Le BIOSHabib FayePas encore d'évaluation

- Chipsets Et BusDocument9 pagesChipsets Et BusSellé GueyePas encore d'évaluation

- Micro-Application 10 Le Livre Du Lecteur de Disquette CPC6128 664 Et 464 (1986) (Acme) PDFDocument423 pagesMicro-Application 10 Le Livre Du Lecteur de Disquette CPC6128 664 Et 464 (1986) (Acme) PDFChipytoPas encore d'évaluation