Académique Documents

Professionnel Documents

Culture Documents

Cours Electronique Convertisseur Numerique Analogique 2

Transféré par

illias28Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cours Electronique Convertisseur Numerique Analogique 2

Transféré par

illias28Droits d'auteur :

Formats disponibles

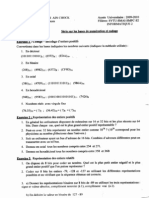

Conversion analoqique-nurnerique et numerique-analoqique

- _. DE ME voi R .~

.~ . $1 /3£~L€ E. N C£ ) ~J MfROIR ...

Formidable. hein ?

---------

OU/J c'est .

Ie mof ...

CNA

- -1

I.- INTERET DES INTERFACES ANALOGIQUES-NUMERIQUES

En g~n~ral, les informations sortant de d~vers capteurs (microphones, sondes, ... ) sont de type analogique, c'est-a-dire que leur va-

leur varie continueMent avec La temps.

Le d~veloppement des techniques num~riques microprocesseurs, transmissions num~riques, circuits int~gr~s, a n~cessit~ l'~tude d'interfaces analogiques-num~riques (convertisseurs) permettant d'~chantillonner et de coder ces signaux analogiques, en signaux num~riques.

L'utilisation de ces techniques concerne d~sormais des domai~es tres vari~s t~l~phonie, acquisition et traitement de donn~es, mesure et instrumentation, son, t~l~vision, etc ...

Ces diff~rentes utilisations possibles imposent des caract~ristiques pr~cises aux convertisseurs :

- Cadence d'~chahtillonnage de plus en plus ~lev~e tuellement 40 MHz

- Faible consommation

- Faible taux d'erreur : pr~cision relative de l'~chantillon meilleure

que 1D- It a 10- 6 •

on atteint ac-

Ce chapitre sera donc une pr~sentation des diff~rents types de convertisseurs existants, 00 l'on pr~cisera leurs domaines d'utilisation.

II.- PRINCIPE DU C.A.N.- CODES UTILISES

A - Role du convertisseur analogique-numerique

Le but du C.A.N. (appel~ aussi codeurl, consiste a traduire

dans un certain code, avec une pr~cision et une r~solution d~t8rmin~es, la grcn,deur analogique a echantillonner, par exemple l'amplitude d'un signal t~l~phonique.

eur analogiquE

chantillonner

A

C.A.N.

tops d'echantillonn Val a e

Echantillon code sur Nbits

age

- 2.

Cette representation se base sur la comparaison de la grandeur analogique ecnantillonee A~ , et d'one grandeor de reference: Vref.

La valeur Vref est divisee en 2N echelons, au N est Ie nombre

de bits du code. Tous les echelons sont de meme largeur egale au "pas de quantification"" .

Le C.A.N. fait correspondre a la valeur A~, Ie numero de l'echeIon (code sur N bits), Ie plus proche dans l'echelle a 2N niveaux.

On voit donc qu'en fonctionnement normal, la valeur du signal a coder A, ne devra pas depasser Vref.

voir fi~u(e. i .

Exemple : Codage d'une tension A comprise entre 0 et 2 volts sur 8 bits en binaire naturel.

On aura V 'f = 2 volts. re

v 'f re

2

Le pas de quantification sera

B mV.

La valeur co dee de la tension 19 mV sera 00000010, soi t Le deuxieme echelon puisque 19 est plus proche de 16 que de 24 dans l'echelle a 256 niveaux.

a

BmV

16mV

24mV

32mV

2V

19mV

a a a a

a a a a

Code a a a a

binaire a 0 a a

a 0 a a

a a a a

0 0 1 1

0 1 a 1

La resolution

Ion pas de quantification. a o a a a 1 o a

du C.A.N. caracterise la largeur de chaque eche-

La precision caracterise la difference entre la valeur codee et la valeur echantillonnee.

La suite de bits en sortie du C.A.N. depend du code choisi ; etudions les plus utilises.

3

t

.. .. ,-

Q,r "0 ::J

-

I I I I I I I I i I

I • I I I I

I I I I I I I I I I

I I I I I I I I I I I I I I I

I I I I I I I I I I

'-

I ....

.

~'" ..

...

.....

,

.....

.....

..

I I I I I I I I I I I II)

::;,

.!l'

C)

ji ..2

e

c:

Q,r e

CI _

to I C

"0 I c:

a

LJ I .~

~~~~g OIl

"0 c:

----- _::;,

co ____ "tJ

---6 II)

--- ~

~

co ""Q

c:

a 8 S

:;: --~

to co --- -------- -5

o~ ~ --- -

..... .... q) ..

+- .--~ II) ::;,

c 0 c: .5r

to ==::---------

::J co .9 ,~

a ~

-.-~ Q,r aE

u ~ ::J .~ ::;,

--- oCT

co °C ~ e .

,Q,r .... -

E c: C

~ ::J C c:

0 ----~ 6-'~

---- c

~

.- . ' ,.' '," to -9 c:

----~ c II)

co ____________ CI ~ ....

co ____

Q,r ...... _-- -------- V) 1::.

CI ..- ---- czi"1I)

to Q,r

C ;;::~ C) ~.

c CC:

.3 ..... --- ------ C:S

..- -- c:

+- ,.S!

c··

to.'·o ~---~ ~

.s: - --- -------

u ~ =:.:.- ------- c:.

w C

..0 ~---~ -5

- --- ------- ~Q)

-=:: ------- _

I ~

OIl

I Q)

Q,r Q,r I .9-

"0 I ~

::J ~ ... ------I .c:

CT

°61 ;;:

.s 0. e;

to E I

c <t:

to "';"l

ro .~

c

CI 1.1..;

V)

to CIJ VI

~

-, I I I

I ....

I -ev I·E· I ~.

~

I III

I ~

1 .~ 101

• ..9

I ~

I ttl

. ... . ~

I e:

~ E

15 ...

C1I > c a W

ttl C

.~ l/)

4'

5

111.- CONVERT1SSEURS ANALOG1QUES NUMER1QUES

A.- Principe du C.A.N.

Comme precedemment indique, un C.A.N. traduit dans un code la valeur echantillonnee du signal A present ~ son entree.

v nH Les nivea.ux de quantification sont distants de a =

- N

2

pas de quantification ( dans Ie cas ou on ne considere que des nombres positifsJ

La resolution est liee au nombre de bits N.

~

En remplaQant la valeur echantillonnee A par une valeur prise

dans une echelle discrete, on commet une erreur de quantification assimilable ~ un bruit qui s'ajoute au signal: c'est Ie bruit de quantification.

Pour minimiser l'influence de cette erreur, on construit ues CAN dans lesquels on associe la valeur discrete : kq (0 ~ k < 2) ~ toute valeur

~ -'

A se trouvant dans l'intervalle L- ~ + kq, ~ + kq]. c en t re sur Le kic!n,'=

echelon.

L'erreur de quantification reste dans ce cas toujours infprieu-

re a q/2.

On trouvera figure 2, la courbe de transfert ideale d'un C.A.~. sur 6 bits, ainsi que l'evolution de l'erreur de quantification.

On montre que l'erreur de quantification est equivalente ~ un

q2 ~. q

bruit d'energie 12 ' (valeur e f f Lc ac e --- J dans Ie cas ou tous les echelcns

t - °do t t t'f' t i l i - .112

son equl lS an s : quan l lca lon lnealre.

Ce bruit conduit ~ un rapport signal sur bruit de quantification, exprime en decibels, valant approximativement : 6 x N.

Plus on utilise de bits, moins ce bruit est important par rapport au signal: en effet, la largeur des echelons diminue.

Par exemple, pour 10 bits, on atteint !

60 dB, qui sera n~-

gligeable par rapport aux perturbations qui pourront etre apportees par une transmission.

Code

111110

/ /

/

/

/

/

/

/

/

/

111111

/

/ /

000001

000100

000011

000010

000000

q I 2q' 3q '4q '5q

! r

RemaJtque

Bruit d'ecretage

II peut superleur a Vref. C'est peut crier au telephone depassee pendant plus de 1 %

1 -

arriver que Ie signal a coder soit momentanement

Ie cas dans Ie systeme telephonique ou Ie locuteur et ou on a fixe Vref a la tension qui n'est pas du temps par 99 % des locuteurs.

Dans ce cas, la valeur du code attribue a l'echantillon, est "11 ... 11", soit tous bits mis a 1.

II y a saturation du codeur. L'erreur introduite s'appelle bruit de saturation ou bruit d'ecretage.

De toutes ces remarques, nous pouvons deduire la structure elementaire d'un C.A.N.

Un comparateur compare l'ech~ntillon A~ a coder, avec la suite des echelons (calcules a partir de Vref et de N), disponibles a la sortie d'un generateur de tension. Un systeme logique elabore Ie code correspondant a chaque echelon. Quand.le comparateur detecte Ie bon echelon, un siBnal de commande stoppe l'incrementation de la tension de comparaison; la suite binaire est alors disponible.

Le debut de la sequence mise a zero du code, rEmise a zero de la tension de compar.aison, est commande par un signal lie a l'horloge connant les "tops" d'echantillonnage.

On trouvera figure 3, Ie schema synoptique elementaire d'un

C.A.N.

On peut realiser de plusieurs fa~ons Ie generateur de tension de comparaison. Nous allons en etudier les differents types.

CODE

MSB LSB

Comparaison

Tension

d'entree

sequence de codage

Logique

Cenerateur de

tension de comparaison

Cde de

reference

Tension de

Pig. 3

Synoptique elementaire d'un convzrtisseur analogique-numerique.

B - C.A.N. a rampe

8

C'est l'un des plus anciens et des plus faciles a realiser.

Le codage est base sur la mesure du temps que met la tension aux bornes d'une capacite C, chargee par un courant constant I, pour passer de o a une valeur egale a la tension a coder.

Voir schema, figure 4.

MSB

Comparateur 1----

I I

r--~ Comp teur 1---.+--"'--

de codage

Horloge eriode e

--I I

~~.__._....._,. RA Z I

r----------- -

I I

L _

It C

I I I I

I

L .... _

Figure 4

Cde

-,

I I I I I I

I

----

Schema synoptique d'un CAN a rampe

La tension aux bornes de la capacit~ est compar~e ~ la tension

~ coder. Le Signal issu du comparateur autorise ou stoppe l'evolution d'un compteur commande par une horloge i~terne.

Le compteur et la tension aux bornes de C, sont remis a zero par un signal lie ~ l'horloge d'echantillonnage.

Soit v la tension aux bornes de la capacite. c

On a

v c

I. t C

SitF est Ie temps nicessaire pour avoir Vc

I. tF

V e

c

M

Pendant ce temps tF ' Ie ccmpteur a enregistre le nombre d'impulsions, ou e est la periods de l'horloge interne.

8

Donc

c

I.e

v ,proportionnel a v

e e

M

e et C peuvent etre stables et connus, la principale cause d'erreur proviendra des fluctuations de I.

On trouvera figure 5, un cicgramme des temps de 1 'evolution de Vc' de la sortie du comparateur, et de la porte ET.

Ce type de convertisseur s'appelle aussi convertisseur tensionduree, puisque l'on mesure Ie temps que Vc met pour atteindre Ve.

Ce convertisseur est lent, [il faut attendre la mantee de Vc)' il sera utilise pour des signaux variant lentement.

Remarquons que Ie temps de mesure sera toujours inferieure

~ la periode d'echantillonnage, et si 'on code Ie signal sur N bits, on aura

tF .

max~mum

e

1

- AD

-------- -- -- ---~

,

/

t

o

t

F max

..

Sortie Comparateur

Compt

~ M impulsions pendant le temps tf

/ ~ "

eur

.. RAZ

Figure 5 CAN a rampe

Evolution en fonction du temps de la tension aux bornes du condensateur C~ des informations en sortie du comparateur et de la porte ET.

C - C.A.N. a rampe numerique

La tension de comparaison generee par Ie comparateur est alors une "rampe en escalier". Elle comporte 2N niveaux. chacun separes du precedent d'une valeur egale au pas de quantification.

On arrete la progression quand la valeur de la rampe devient superieure ou egale a la tension a coder.

La duree de chaque echelon est li§e a~ temps de r~ponse des systemes logiques, du comparateur, et au temps de stabilisation ces echelons Cdisparition des transitoires), d'ou en general un temps de conversion assez long

o

Ve Comparateur J 1 1

r-. 1\ Cde

V Cornpteur -

,-LJ seq PJence

GH H ---

I

I

I

~vru I

V 2N ,

ge

Generateur

- r---

V -f

d'echelons de tensions re Fig. 6

Schema synoptique d "un CAN d rampe numetri.que

Pour realiser Ie g~n6rat8ur de rampe num~rique, on peut utiliser un dispositif ~ charge de condensateu~s et commutateurs analogiques.

On peut aussi utiliser un systeme entierement numerique : bascules, compteurs, commutateur, facile a realiser et precis, d~nt on trouve un exemple, figure 7, sur 4 bits .

. _'

H

RAZ

R

"12- -

(CODE 4 BITS) .......

r

LSB

o

.' .....

'MSB

Comparateur

o

R

--

T

R

o

R

--

T

V ~f re

r - - - f- -- --- --- - - - f- - - - - - - - - - - - - - - - - - - -

CNA

-

I

I

~ I I ,

I

I

I I I I

- , I

L __

•

-

T

o

•

•

RESEAU DE DECODAGE A RESISTANCES

f---i---- .....

I I I I

I I I

I I I I I I I

I I I I I I

-- ---- -.------- J

F-z..gure 7

•

On peut remarquer que la partie: reseau de resistances, commutateurs, joue Ie rale d'un convertisseur numerique analogique, a partir d'un code etabli en sortie des bascules.

D - C.A.N. a double rarnpe

Dans Ie cas du C.A.N. a simple rampe, on a vu que la precision de la mesure depend de la precision de R, de C et de I.

Le C.A.N. a double rampe evita ces problemes, et est utilise en instrumentation.

"_

- 13

On charge dans un

premier temps. to' Ie condensateur ~ Ve· to J

--~~- . puis on Ie decharge.

Re

partir de

Ia tension Ve, (on atteint l e tension Quant ~ I'entree. Ia tension - Vrefo

en app 1 i-

On montre que 1a tension repasse ~ 0 au bout du temps.

t

V e

to °

V 'f re

independant de R et de C.

/

La mesure du temps t suffit ~ coder Ve' puisque etre connus de fa~on precise.

On trouvera figure 8. Ie schema synoptique d'un C.A.N. a double

to et V c peuvent rei

rampe.

c

Ho r loge

5 1

~ ~----~~R~f----L--__,

Comparateur

Integrateur

____ I

Remise a zero

en debut de codage

Compteur

Code

Figure 8

On trouvera figure 9, Ie diagramme des temps de la tension a la sortie de l' integrateur .

o

Temps

RC

"*,.

Figure 9

Le temps de codage est tres long, ce convertisseur sera donc utilise pour les signaux a evolution lente.

La presence d'un integrateur Ie rend peu sensible aux parasites.

.t

'-..

- 15

E - C.A.N. a tension frequence

Principe derive du C.A.N. ~.rampe.

On cherche a obtenir un signal dont la frequence varie avec la tension d'entree a coder.

Pour cela, on utilise un monostable [voir figure 10) qui delivre une suite d'impulsions, et qui servira a la remise a zero de l'ampli inte.grateur R-C.

/

Vers compteur

l1onostable

de I r equen ce

R

I

I ,

, .J

T

t

c

v 5

Fig. 10

CAN tension-jriquence

Si ve est constant pendant 19 temps T d'integration, et Vs 0 en debut de charge de la capacite, on aura:

V 8

T

- 16

Le monos table sera declenche quand

v of re

- V e

R.C

T.

II produira alors une impulsion de remise a zero, qui sera prise en compte par un compteur de frequence.

Si la tension a coder Vest constante pendant un temps long Cplusieurs T), alors Ie monostable deli0rera des impulsions a une frequence :

F

- V e

et un compteur de frequence transformera ces impulsions en une information codee.

La presence d'un integrateur rend ce C.A.N. peu sensible aux perturbations. La stabilite de R, de C et de Vref est essentielle.

Ce convertisseur est lent, et sera utilise en basses frequences.

F - C.A.N. a approximations success;ves

Appele aussi convertisseur a pesee.

Comme pour une pesee, on opere par essais successifs en comparant la tension a coder Ve avec, tout d'abord, la tension Vref : cela deter-

2

mine Ie bit de poids Ie plus fort, MSB ; ensuite, on comparera Ve a la tension

Vref Vref Vref Vref

----- + ---.- au a la tension Csuivant Ie MSB) pour dete~miner

2 4 2 4

Ie 2eme bit; on continuera la mesure en diminuant l'incrementation de la tension de comparaison.

On trouvera sur la figure 11 ci-dessous, un exemple de sequence de codage sur 3 bits. Le codage se fait alors en 3 temps.

\,.>

- 11

-,/

Ier temps

2eme temps

Plus g§n~ralement, ~ chaque cycle d'horloge, correspond la d~termination d'un bit. Pour coder sur N bits, il faudra N cycles d'horloge.

La dur§e totals de la conversicn sera de ce de l'horloge.

N F

ou Fest la f r-equen-

Cette frequence est limitee pee la vitesse de reponse du comparateur et des circuits logiques.

- ·18

La figure 12 montre Ie schema synoptique d'un tel C.A.N

Un registre a decalage de N bits sert a stocker les bits resultant de la comparaison.

Fig. 12 - Schema synoptique d'un CAN

a appro~mations successives.

Comparateur

_Ve ----I~

....-----.V.?---------,

Cde

..

C N A

-

-0

Code

Registre N bits

Logique

-

-0

-

La figure 13 montre une realisation a l'aide de bascules 0, et d'un reseau de decodage a resistances.

Ce C.A.N est particulierement precls et permet des vitesses de conversion tres elevee (inferieure a la micro-seconde) .

C'est de loin Ie plus employe.

,'. -e

Horloge

-

H

"

H , f

Figure 13

~ IMPULSION DE DEPART

, ~1

>~ ~V>--'

Comparateur

'!. Re t ar d

Regist:re

~------~~ ~--~~------~~-------.~--------

rl-/

-

-

o 1

I I

SDRMSB I)

o 1

)

o 1

o

-

1

LSB I)

.,; I

I 1

J I I

- - --- --- -~---l

.j

Reseau

de

o

decodage a

resistances

-------~---

I J I

r I I I

__ ~---..J

CNA

G - C.A.N. parallele

20

Dans taus les codeurs vus precederlJrnent. les bi ts du code n'etaienr. pas determines en rnerne temps. au bien plusieurs operations successiyes de comp ar-at s on etaienr ngeessai res.

l.e C.A.N. p ar aLl e l e erabl:il:" cous l es bits du code au meme momenrt Ie temps de conversion est done tres court.

Ve (MSB)

Fig. 14

----0

Code

CAN parallele a 3 bits

- 21

Avec ce type de C.A.N., en obtient des vitesses de conversion de l'ordre de quelques dizaines de nanosecondes par conversion.

Cette vitesse est limitee essentiellement par la rapidite des

comparateurs.

Cependant, la complexite du circuit croit tres vite avec Ie nombre de bits (il en est de meme du prix ... ).

Ce C.A.N. est surtout utilise pour un faible nombre de bits, au bien on l'associe a un C.A.N a approximations successives.

De plus, son utilisation necessite une tr~s bonn~ adaptation d'imp~dance avec Ie circuit exterieur.

III - CONVERTISSEURS NUMERIQUES-ANALOGIQUES

A - Generalites

Le C.N.A fait co r-r-espondr-s urie tension (OL! un cou ran t ) de s o r> tie correspondant a la valeur codee sur N bits.

On doi t avoir

N

a.

L 1

Vs V ref 2i

i=l ou a1 est Ie bit de plus fort poids (de poids

V 'f re

2

V . et aN est Ie bit de plus faible poids (de poids 2~ef)

Quand tous les bits sont a 1. on obtient la tension

1 V 'f (2N - 1) •

re 2N

V ~ reI

V ref

N 2

On ne pourra donc jamais atteindre V f' re

Les C.N.A les plus simples utiliseront des systemes de sommations de courant, de tension.

La conversion necessite 12 presence de taus les bits dans Ie convertisseur : Le convertisseur est de :ype "para 11 e!le" .

D'oli, l'utilisation de registres a decalage si les bits arriverrt err serie au convertisseur.

( . . J

- '!2 .:

B - C.N.A a soromation de courant

Pour obtenir la tension Vs, on fait passer dans une resistance

1 t I 2I 4I 2(N-1) I· . d ~ ~ t d~

r es couran s , , , ... , ., lSSUS e genera eurs comman es par

les bits, a t ' a2, ... aN·

La tension aux bornes de rest alors

V r

(N-1)

'" + aN.2. I).r

Etudions un exemple de realisation dans laquelle la resistance est remplacee par un amplificateur operationnel : c'est l'exemple de la figure 15 ..

E

R/B

I I I I

I . ,~

R I

R/2

a I

R

Fig. 15

C.N.A. a sommation de courants et ampli-Op.

)

- 23'-

On a

E 2E 4E N-l

i 2 E

avec a1 + a2 + + a3 + + aN

R R R ... R

D'ou Rl [ a 1 N-l aN J

V - E + 2 a2 + 4 a3 + " . + 2

S

R Les principales causes d'erreurs dans ce CNA proviennent de la difficulte de realiser des resistances dans une gamme de R a R/2N-1 avec une precision et une stabilite suffisantes.

~ De plus, les commutateurs analogiques n'ont pas en general des

caracteristiques ideales : resistance nulle ou infinie.

Et aussi, les caracteristiques de l'ampli-op peuvent ne pas etre stables.

C'est pourquoi, dans Ie cas d'un nombre eleve de bits, on prefere utiliser une structure modulaire, comme celIe de la figure 16.

II faut un affaiblissement de 16 pour les 4 bits de plus faible

poids.

On a

V S

- R E

1

R

11 faut done

1

16

o

E

BR

4R

2R

R

BR

4R

2R

(

R

,

\

RJ

Fig. 16 = CNA a sommation de cou~ants ~ modulai~e a ~esistances

o

. ,

~ 5

Convertisseur digitaI-analogique it echelle R12R

Soit X une variable reelle positive dont la valeur en decimal est notee x et dont la valeur en

binaire est notee (X)2 = bn_Ibn_2 ... b, b, ,avec: (Vj) bj E {O,l}.

On code la valeur de x a l'aide de n commutateurs bidirectionne1s (fig. 1) dont les etats sont

decrits par les variables booleennes definies comme suit:

(Vj) b j = ° court-circuit entre B j et la borne 0 du commutateur,

(Vj) b j = 1 court-circuit entre Bj et la borne 1 du commutateur.

L'amplificateur operationnel utilise pour la realisation du convertisseur est parfait et fonctionne en regime Iineaire. La tension de reference E est delivree par une source d'impedance interne nulle.

AO R A1 R

~2RMU • A.t&.

ty-

i

2R 2R 2R J I

I

wk

4: 1'10 Bk o 1

Figure 1

1) On considere I'etat des commutateurs decrits par bk = 1 eet (Vj:j:. k) b j = 0. Montrer, par application du theoreme de Thevenin, que Ie reseau R-2R vu entre I'entree inverseuse et la masse, est equivalente a un generateur de resistance Rk=R et de f.e.m. Ek = EI 2{n-k) (fig.2).

2) L'etat des commutateurs est maintenant code par la variable reelle (X)2 = bn_lbn_2 ... b.b.; Determiner la tension de sortie v en fonction des resistances R, R', de la f.e.m. E et des variables booleennes b j .

3) On considere , pour la suite du probleme, que Ie convertisseur etudie est un convertisseur it 12 bits. Calculer la tension de sortie maximale v max sachant que E=lO Vet R=R'.

QueUe est la valeur du quantum v min ?

QUe! est le nombre de points de me sure de ce convertisseur?

2(;

4) Connaissant les caracteristiques du convertisseur, it savoir le nombre n=12 de cellules, la f.e.rn. E=10 V et les resistances R, R' que I'on prendra egales, proposer un algorithme dormant l 'etat de chacun des convertisseurs en fonction de la valeur de la tension de sortie v.

5) Applications numeriques.

a) On mesure une tension.de sortie v=2,837 V, determiner I'etat des commutateurs.

b) Reciproquement, I'etat des douze commutateurs est code par le nombre binaire (X)2 = (101000110001)2, quelle tension releve-t-on it la sortie?

Solution:

1) Pour calcu1er l'impedance du reseau, i1 nous faut eteindre 1a source de tension E. Alors, quel que soit l' etat des commutateurs, toutes 1es resistances 2R sont reliees it la masse.

En exc1uant la partie du reseau qui se trouve it ladroite du noeud Ao (fig.1), on constate que I'impedance est 2R1/2R=R. Cela etant, si on exc1ut Ia partie du reseau situee it droite du nceud AI' on trouve encore I'impedance R.

En continuant ainsi jusqu'au nceud A 0-1 ' on etablit que I'impedance du reseau, entre I'entree inverseuse et la masse, est R. Remarquons que ce resultat est independant du nombre n de cellules R-2R utilisees.

r---------,

~ Ak

2R 2R

2R

E

,J;

I I

L J

R

R An-1

I I I

I I I I I I I I r I I I

L ..J

Ak .. 1

R

2R

Figure 2

(a)

(b)

( c)

Placons nous maintenant dans les conditions du probleme, a savoir: b k = 1 et ( \fj -::j:. k) b j = O.

Utilisant I' etude precedente, on aboutit facilement au reseau represente figure.Za, dans lequel la partie situee a gauche de A k a ete remplacee par ]a resistance 2R. Par application du theoreme de Thevenin a Ia partie encadree de la figure Za, on aboutit au reseau de Ia figure 2b. Considerons, a son tour, ce dernier reseau, et appliquons une nouvelle fois le theoreme de Thevenin a la partie encadree. On obtient le reseau represente figure 2c.

On constate ainsi que les reductions successives font apparaitre des generateurs de Thevenin possedant toujours la meme impedance interne R et des f.e.m, de valeurs successives E/2, E/4, E/8 ...

Pour aboutir au schema propose figure 3, c'est a dire a une reduction complete du reseau etudie, il fautra appliquer (n-k) fois Ie theoreme de Thevenin, En consequence, on en conc1ut que R k =R et que Ek = E . 2-(n-k) .

Fig. 3. - Gene~1teur equivalent.

Remarquons aussitot que ce generateur debite un courant i=EIR.r(n-k) dans Ia resistance R' puisque Ie nceud An_1 est virtuellement a la masse et qu'aucun courant ne traverse I'entree inverseuse de l'amplificateur operationnel.

2) L'etat des differents commutateurs est maintenant code par la variable (X)2 = bn_Ibn_2·.·blbo .c'est a dire qu'un certain nombre de bomes Bjsont reliees a la masse

( b j = 0) et les autres B j sont reliees a Ia source de tension E ( b j = 1).

Le courant i debite par Ie reseau s' obtient immediatement par application du theoreme de superposition des regimes elestriques:

Comme v=R'i, il vient aussitot:

R' 0-1

V= E-R Lbk.r(n-k)

k=O

(1)

II suffit de connaitre I' etat des differents commutateurs pour calculer effectivement Ia tension de sortie v. Remarquons enfm que le resultat precedent reste valable quel que soit le nombre n de commutateurs utilises, c'est it dire que1 que soit Ie nombre n de bits du convertisseur.

Zi

3) La tension de sortie sera maximale lorsque tous les commutateurs seront dans l 'etat 1, c'est a dire quand toutes les bomes B j sont reliees a la source de tension E. En tenant compte de R=R', il

vient aussitot la relation (1):

~ -(12-k) Ef 1 1 l

V = E. ~2 ="2L 1 + 2+'·'+ 2ll J

La source S de la progression geometrique de raison r= 112 qui se trouve entre crochet est: 1 r12

s= - =2.(1_2-12)

1-1/2

D'ou la valeur maximale v max de la tension de sortie:

V max = E.(I-rI2)

Application numerique: E=10 V, n=12~ v max :::; 9,998 V.

La valeur v min du quantum s'obtient en considerant I'etat pour lequella borne Bo est reliee ala

source de tension ( b 0 = 1) et toutes les autres bomes reliees a la masse : (vk i= 0) b k = 0 .

De la relation (1), on tire immediatement

E

v min = 212

A.N: V min =2,44 mY.

Le nombre de points d'un convertisseur est egal au nombre d'etats distincts de ses commutateurs. Chaque commutateur pouvant avoir deux etats, i1 en resulte que Ie nombre d' etats

distincts d'un convertisseur a n bits est 2 n • En consequence, un convertisseur a n bits est un dispositif a 2 n points de mesure.

A.N: n=12~ 212=4096 points de mesure.

4) En tenant compte de R=R' et apres multiplication des deux menbres de la relation (1) par 2 n, on obtient:

n-I

V n'\' k

-.2 = L.Jbk.2

E k=O

Soit encore, en explicitant Ie deuxieme menbre dans I'hypothese n=12:

(2)

;.2n = bll.211 + blO.2IO + b9.29+ .. .+b1.2+ b,

= (( ... ( (bll.2 + blO).2 + b, ).2+ ... ).2 + bl).2 + b,

On fait apparaitre ainsi dans Ie second menbre l' algorithme de Homer qui montre que:

a) en divisant (vIE) 2 n par 2, on obtient comme premier reste b.,

b) en divisant par 2 Ie quotient precedemment obtenu, on obtient comme reste b.:

c) en poursuivant ainsi jusqu'a obtenir un quotient nul, on obtient comme reste b2, b3 , ... b11

En d'autres termes, l'algorithme propose est celui de la conversion d'un nombre entier decimal en un nombi e entier binaire.

5) Applications numeriques: v

a) E .212 = 1162 done en utilisant l'algorithme precedant:

1162=2x581+0~ bo=O

581=2x290+1~ bl=l

290=2x145+0~ b2=O

145=2x 72+1~ b3=1

72=2x 36+0~ b4=O 36=2x 18+0~ bs=O

18=2x 9+0~ b6=O

9=2x 4+1~ b7=1

4=2x 2+0~ bg=O

2=2x 1+0~ b9=O

1=2x O+l~ b!O=l et par suite bll et bI2=O.

b) Pour ealeuler la tension desortie v, il suffit d'utiliser la relation (1) dans laquelle on fait R=R', puis b, = b, = b, = b, = bl! = 1, etles autres bk = O. Done:

v = 10. [r12 + rg + r7 + z-3 + 2 -I] =6,369 V.

Vous aimerez peut-être aussi

- Convertisseur PDFDocument5 pagesConvertisseur PDFBarhoumi Mourad100% (1)

- Convertisseur Analogique - NumériqueDocument108 pagesConvertisseur Analogique - NumériqueCrystal LopezPas encore d'évaluation

- Conversion Analogique en NumériqueDocument4 pagesConversion Analogique en NumériqueHaryoran100% (2)

- Cours ElectroniqueDocument104 pagesCours ElectroniqueAnna GriffinPas encore d'évaluation

- Modelisation de La MASDocument20 pagesModelisation de La MASsaadbaraa100% (1)

- Cours N°9 - (Monostables)Document6 pagesCours N°9 - (Monostables)gg91100% (2)

- Les Comparateurs NumeriquesDocument4 pagesLes Comparateurs NumeriquesAbdelhadi EnnajihPas encore d'évaluation

- Transfomateur TriphaséDocument7 pagesTransfomateur TriphaséBounegab Youcef100% (1)

- Les Oscillateurs Chap 13 CoursDocument10 pagesLes Oscillateurs Chap 13 Coursdjibrilos100% (3)

- Variateur de Vitesse Pour Moteur À Courant Continu Par PIC16F876 en MLI (PWM) 12V PDFDocument15 pagesVariateur de Vitesse Pour Moteur À Courant Continu Par PIC16F876 en MLI (PWM) 12V PDFcherif slimPas encore d'évaluation

- PDF CoursDocument8 pagesPDF CoursAhmed MohamedPas encore d'évaluation

- Chapitre III Les RedresseursDocument102 pagesChapitre III Les Redresseurshamoud zamel100% (1)

- Cours Can - Cna (Prof)Document8 pagesCours Can - Cna (Prof)Lams Gt100% (1)

- Cours ConditionneurDocument30 pagesCours ConditionneurHmidaPas encore d'évaluation

- Machine Asynchrone ExoDocument3 pagesMachine Asynchrone Exozaki1700100% (1)

- CAN CNA PDFDocument50 pagesCAN CNA PDFInnan AdamPas encore d'évaluation

- Cours - Mas Mon ResumeDocument39 pagesCours - Mas Mon ResumeAZIZ81936Pas encore d'évaluation

- Commande Par PICDocument65 pagesCommande Par PICabfstbmsodPas encore d'évaluation

- Electronique de PuissanceDocument4 pagesElectronique de PuissanceNOURDINE EZZALMADIPas encore d'évaluation

- Affichage MultiplexéDocument9 pagesAffichage Multiplexémustapha3100% (1)

- OnduleurDocument17 pagesOnduleurGrine Salah Eddine100% (1)

- Chap V BasculesDocument13 pagesChap V BasculesoussamamahjourPas encore d'évaluation

- Interruption 16F877Document29 pagesInterruption 16F877Tran Cuong Hung100% (1)

- Boteuil de Gaz PDFDocument66 pagesBoteuil de Gaz PDF10babilionPas encore d'évaluation

- Electronique de Puissance L2 S2Document74 pagesElectronique de Puissance L2 S2Sofiane BePas encore d'évaluation

- Chapitre II MASDocument31 pagesChapitre II MAShawewi100% (1)

- ChapitreV Les HacheursDocument10 pagesChapitreV Les HacheursAnass TaouFik100% (1)

- Moteurs Asynchrones - 2012Document33 pagesMoteurs Asynchrones - 2012Jaouad DiouriPas encore d'évaluation

- Chapitre 2 Applications Des Amplificateurs OperationnelsDocument20 pagesChapitre 2 Applications Des Amplificateurs OperationnelsMarouane TaibiniPas encore d'évaluation

- Amplificateur OperationnelDocument7 pagesAmplificateur OperationnelMarwa BanaouazPas encore d'évaluation

- Ne 555Document2 pagesNe 555lbaizabdo100% (1)

- ContrôleDocument10 pagesContrôleHassan Guenzaouz0% (1)

- BTS Phy 91Document5 pagesBTS Phy 91Still Karim0% (1)

- Exam Machine ElectriqueDocument4 pagesExam Machine ElectriqueAYMEN BOUJEMELPas encore d'évaluation

- Introduction À L'électronique NumériqueDocument36 pagesIntroduction À L'électronique NumériqueGuillaume HaussPas encore d'évaluation

- Moteur Synchrone AutopiloteDocument6 pagesMoteur Synchrone AutopilotebberrehailPas encore d'évaluation

- Machine Synchrone: I. DescriptionDocument1 pageMachine Synchrone: I. DescriptionKawther BenPas encore d'évaluation

- HacheurDocument13 pagesHacheurLTIMKPas encore d'évaluation

- Cours Et TD Électroniques NumériquesDocument60 pagesCours Et TD Électroniques NumériquesOussama Sadki100% (1)

- 03 Machine Asynchrone ÉlèveDocument16 pages03 Machine Asynchrone ÉlèveGhaith Smida100% (1)

- Electrotechnique Cour Complet V DC Et AC B1Document120 pagesElectrotechnique Cour Complet V DC Et AC B1HamzaEdrissi0% (1)

- Projet Pacemaker A Base de MicrocontroleDocument28 pagesProjet Pacemaker A Base de MicrocontroleAnas ErmPas encore d'évaluation

- Transformateur TriphaséDocument7 pagesTransformateur TriphaséWaheb Ard100% (1)

- Comparateur SimpleDocument6 pagesComparateur SimplelotfibouchefiratPas encore d'évaluation

- A Problemes Corriges DelectrotechniqueDocument370 pagesA Problemes Corriges DelectrotechniqueGuy Yannick Moussavou MboulaPas encore d'évaluation

- Conception Des Circuits Logiques CombinatoiresDocument23 pagesConception Des Circuits Logiques CombinatoiresNGOUNE86% (7)

- TD HacheurDocument2 pagesTD Hacheurabou02Pas encore d'évaluation

- Support Cours LGE604 2010 BF CH3 OkDocument5 pagesSupport Cours LGE604 2010 BF CH3 OkSofiane Benseghir100% (1)

- Automatismes Logiques PDFDocument109 pagesAutomatismes Logiques PDFMila z0% (1)

- Oscillateurs SinusoidauxDocument24 pagesOscillateurs SinusoidauxMohammad Hassoun100% (1)

- Grille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesD'EverandGrille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesPas encore d'évaluation

- Le système d'approvisionnement en terres dans les villes d'Afrique de l'Ouest: L’exemple de BamakoD'EverandLe système d'approvisionnement en terres dans les villes d'Afrique de l'Ouest: L’exemple de BamakoPas encore d'évaluation

- Théorie et conception des filtres analogiques, 2e édition: Avec MatlabD'EverandThéorie et conception des filtres analogiques, 2e édition: Avec MatlabPas encore d'évaluation

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesD'EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesPas encore d'évaluation

- TD 2010 + CorrigéDocument6 pagesTD 2010 + CorrigéHamza Samir100% (1)