Académique Documents

Professionnel Documents

Culture Documents

TD monocycle SESAME 2022

TD monocycle SESAME 2022

Transféré par

mezghaniCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TD monocycle SESAME 2022

TD monocycle SESAME 2022

Transféré par

mezghaniDroits d'auteur :

Formats disponibles

Architectures Architectures

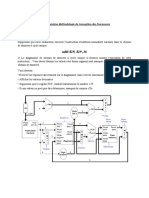

TD Conception Monocycle Recopier ce tableau dans votre feuille d’examen et compléter les valeurs des signaux de commande

pour cette instruction

Exercice 1 :

Supposons que nous souhaitons exécuter l’instruction d’addition immédiate suivante dans le chemin RegDst RegWrite ALUSrc ALUCtr MemWrite MemRead MemToReg PCSr

de données à cycle unique: c

ADDI $29, $29 ,16

1/ Le diagramme de chemin de données à cycle unique ci-dessous montre l'exécution de cette

instruction.. Vous devez fournir des valeurs des signaux de A à M sauf B restants dans le diagramme, Exercice 2

qui sont marqués par le symbole « ? » et ce en recopiant et complétant le tableau ci-dessous dans votre

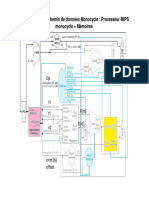

feuille d’examen Nous disposons d’un chemin de données monocycle MIPS (implémentant les instructions de type R,

ORI, lw, sw et beq)

Vous devriez:

• mentionner les valeurs décimales.

• Supposons que le registre $29 contient initialement le nombre 129.

• Si une valeur ne peut pas être déterminée, marquez-la comme «X».

1/ Etant donnée les latences d’exécution suivantes, donner le CPI et la période T qui correspond au

temps d’exécution de l’instruction LW sachant que :

Mémoires de données et d’instructions: 400ps | Banc de registres (READ/Write): 50ps | ALU et

Add: 200ps | Portes logiques et multiplexeurs : 2ps | tout le reste est négligeable.

3/ Nous allons implémenter l’instruction SwPlus rt, rs, (rs), imm dans une architecture monocycle,

cette instruction permet d’effectuer deux opérations en parallèle:

A B C D E F G H I J K L M Opération 1 : elle permet de ranger un mot qui est le contenu de registre de transfert rt dans la

16 mémoire dont l’adresse est donnée seulement par le contenu de registre source rs

Opération 2 : elle ajoute la valeur immédiate du contenu de registre source rs et le résultat sera

2/ Sachant que les valeurs ALUCtr pour chaque opération de l'ALU sont: transférer au banc de registres dont la destination est le registre source rs.

Instruction RTL

M[R[rs]] = R[rt]

SwPlus rt, rs, (rs), imm R[rs] = R[rs] + imm

Dr Dhafer MEZGHANI Page 1 Dr Dhafer MEZGHANI Page 2

Architectures Architectures

1/ Modifier le chemin de données pour implémenter l’instruction SWPlus

Dans le chemin de données, le composant nommée GALU (Greater ALU) joue le rôle de

l’ALU mais possède de plus une sortie « Great » qui est égale à 1 si R[rs]-R[rt]>0 et 0 si

R[rs]=< R[rt]. Comme le cas de zéro, Great est un indicateur vers l’unité de

contrôle. C’est un indicateur de comparaison entre le contenu de deux registres

source et transfert.

2/ justifier brièvement vos choix 1/ Etant donnée les latences d’exécution suivantes, donner le CPI et la durée du cycle de

3/ Recopier et compléter la table des signaux de contrôle qui permettent d’implémenter cette l’horloge T1 pour l’implémentation de l’instruction lw sachant que :

instruction SwPlus :

Memory: 300ps | Banc de registres (READ/Write): 50ps | GALU et Adders: 100ps |

RegDst RegWrite ALUSrc MemWrite MemRead AddrSrc MemtoReg PCSrc

Portes logiques et multiplexeurs : 2ps | tout le reste est négligeable.

CPI =

Exercice 3 T1 =

A/ Nous disposons d’un chemin de données monocycle MIPS (implémentant les

B/ Les concepteurs MIPS ont identifié des instructions supplémentaires que peut

instructions de type R, ORI, lw, sw et beq) réaliser le processeur MIPS (vu dans le cours). Ces instructions sont :

Instructions Description

cs $rd, $rs, $rt Le registre de destination rd reçoit le max (le

plus grand) suite à une comparaison entre le

contenu de rs et celui de rt

cslw $rd, $rs, $rt Le registre de destination rd reçoit la donnée de

la mémoire de données dont son adresse est le

max suite à une comparaison entre le contenu

de rs et celui de rt

cslwcs $rd, $rs, $rt Le registre de destination rd reçoit le max suite

à une comparaison entre le contenu de rs et la

donnée générée par la mémoire de données

Dr Dhafer MEZGHANI Page 3 Dr Dhafer MEZGHANI Page 4

Architectures Architectures

dont son adresse est déterminée aussi par le

maximum entre le contenu de rs et celui de rt

Il est alors clair que les abréviations cs et lw dans les mnémoniques ci-dessus Nouvelle durée du cycle de l’horloge :………………………………………

signifient : compare_select et load word

b-2 éme pseudo-instruction : cslw $rd, $rs, $rt

1/ A partir de la description ci-dessus, donner le niveau RTL des différentes instructions

Instructions RTL

cs $rd, $rs, $rt

cslw $rd, $rs, $rt

cslwcs $rd, $rs, $rt

2/ Nous nous proposons d’apporter des modifications au chemin de donnée et aux

signaux de contrôle, en suivant les consignes suivantes :

- Il est recommandé de minimiser le nombre de matériel à ajouter.

- En ajoutant une nouvelle instruction, il ne faut pas altérer le fonctionnement des

instructions de base.

- Eviter d’ajouter des registres ou des mémoires au chemin de données.

- Il est possible d’ajouter des multiplexeurs, GALU.

Pour chacune des nouvelles instructions mentionnées, nous demandons la modification

du chemin de données, les valeurs des signaux de contrôle ajoutés et existants et la

nouvelle valeur du cycle d’horloge. Il sera tenu compte de l’optimalité de la solution.

a-1 ère pseudo-instruction : cs $rd, $rs, $rt

Points de contrôle :

Nouvelle durée du cycle de l’horloge :………………………………………

Points de contrôle : c-3 éme pseudo-instruction : cslwcs $rd, $rs, $rt

Dr Dhafer MEZGHANI Page 5 Dr Dhafer MEZGHANI Page 6

Architectures

Points de contrôle :

Nouvelle durée du cycle de l’horloge :………………………………………

Dr Dhafer MEZGHANI Page 7

Vous aimerez peut-être aussi

- Defendez VousDocument172 pagesDefendez VousStan BelingaPas encore d'évaluation

- Chap8 - Contrôle Qualité Des TravauxDocument6 pagesChap8 - Contrôle Qualité Des Travauxbahazagoub7100% (1)

- Réparation Et Renforcement Des Fondations Fin-1Document41 pagesRéparation Et Renforcement Des Fondations Fin-1Arij Naily Ep HammamiPas encore d'évaluation

- PL SQLDocument60 pagesPL SQLmuzoxi100% (5)

- Le Harcelement Scolaire - Cpe41Document14 pagesLe Harcelement Scolaire - Cpe41Zy NabPas encore d'évaluation

- DR Kousmine, Qui Était-Elle - Association Kousmine FrançaiseDocument10 pagesDR Kousmine, Qui Était-Elle - Association Kousmine FrançaiseBlandine Belkalem100% (1)

- TD 3 CinemaTiqueDocument15 pagesTD 3 CinemaTiqueMohamed OuladPas encore d'évaluation

- Examen Final MCP Juin 2022 LEEA2Document8 pagesExamen Final MCP Juin 2022 LEEA2Dhafer MezghanniPas encore d'évaluation

- Liste Des Sociétés 2Document12 pagesListe Des Sociétés 2mezghaniPas encore d'évaluation

- 002 Pipeline 1-2Document36 pages002 Pipeline 1-2frankleProfPas encore d'évaluation

- TD2 ArchitectureDocument10 pagesTD2 ArchitecturemezghaniPas encore d'évaluation

- TD 2 Complémentaire SoC MulticyckeDocument10 pagesTD 2 Complémentaire SoC MulticyckeDhafer MezghaniPas encore d'évaluation

- Examen ISE MP2ERTA Janvier 2022Document5 pagesExamen ISE MP2ERTA Janvier 2022Dhafer MezghanniPas encore d'évaluation

- TD3 ArchitectureDocument9 pagesTD3 ArchitectureDhafer MezghaniPas encore d'évaluation

- Examen SOC Session Rattrapage LEEA3 Janvier 2022Document6 pagesExamen SOC Session Rattrapage LEEA3 Janvier 2022Dhafer MezghanniPas encore d'évaluation

- Examen MP1ERTA Janvier 2020 FinalDocument9 pagesExamen MP1ERTA Janvier 2020 FinalDhafer MezghaniPas encore d'évaluation

- 2018chapitre3 6800Document6 pages2018chapitre3 6800lyza DZPas encore d'évaluation

- TD 2Document8 pagesTD 2Nesrine ZouariPas encore d'évaluation

- Examen MCP Juin 2022 LEEA2Document6 pagesExamen MCP Juin 2022 LEEA2Dhafer MezghanniPas encore d'évaluation

- Correction TD2 ArchitectureDocument8 pagesCorrection TD2 ArchitectureDhafer MezghaniPas encore d'évaluation

- 6 - Chapitre 6 Le Langage PL - SQL Leçon1 Introduction Au Langage PL - SQL EEEEDocument5 pages6 - Chapitre 6 Le Langage PL - SQL Leçon1 Introduction Au Langage PL - SQL EEEEsouissi souissiPas encore d'évaluation

- Tdscheduling2020 2021Document3 pagesTdscheduling2020 2021Atashi Tsunagu (“Albedo”)Pas encore d'évaluation

- Examen MR1EEA Janvier 2020 FinalDocument9 pagesExamen MR1EEA Janvier 2020 FinalDhafer MezghaniPas encore d'évaluation

- INF7440 Notions BaseDocument21 pagesINF7440 Notions BaseNana Ben SouaïbPas encore d'évaluation

- Correction Rattrapage 2013Document10 pagesCorrection Rattrapage 2013abir cherifPas encore d'évaluation

- Chap3 ICT104Document8 pagesChap3 ICT104christimimbangPas encore d'évaluation

- PL SQLDocument21 pagesPL SQLakram el hadriPas encore d'évaluation

- Ceg 3556 Devoir 3 SolutionsDocument3 pagesCeg 3556 Devoir 3 SolutionsNadir RhaziPas encore d'évaluation

- 05 Data PathDocument32 pages05 Data Pathbouchra allalouPas encore d'évaluation

- GIF 16116 Examen1 H09 SolutionDocument8 pagesGIF 16116 Examen1 H09 SolutionYassinox kamalPas encore d'évaluation

- TdcommutDocument2 pagesTdcommuthafssahakim2001Pas encore d'évaluation

- Cours ns2Document8 pagesCours ns2informatiquehageryahoo.frPas encore d'évaluation

- TP 2Document9 pagesTP 2soyed mohamedPas encore d'évaluation

- Chapitre 3Document13 pagesChapitre 3Dhafer MezghaniPas encore d'évaluation

- TP Circuits LogiquesDocument3 pagesTP Circuits LogiquesimenessPas encore d'évaluation

- Chapitre 3 - 2020Document6 pagesChapitre 3 - 2020Mahdi MahdiPas encore d'évaluation

- ArchiCtrl 2004-02-12 Correction PDFDocument3 pagesArchiCtrl 2004-02-12 Correction PDFAmineBenali0% (1)

- Rattrapage 2018-2019 + SolutionDocument4 pagesRattrapage 2018-2019 + SolutionHettal AdelPas encore d'évaluation

- Examen IE5 Janvier 2020 FinalDocument14 pagesExamen IE5 Janvier 2020 FinalDhafer MezghaniPas encore d'évaluation

- EX1 PipelineDocument2 pagesEX1 PipelineEMNA KANZARIPas encore d'évaluation

- Examen AO Corrig Univ Guelma 2018Document6 pagesExamen AO Corrig Univ Guelma 2018Siaka Dycosh BertePas encore d'évaluation

- CPIA2 Lahmadi Youssef Prosit4Document8 pagesCPIA2 Lahmadi Youssef Prosit4Youssef LahmadiPas encore d'évaluation

- 01 PilesDocument12 pages01 PilesMYSTÉRESPas encore d'évaluation

- NSY104 TD Pipeline C-2 PDFDocument2 pagesNSY104 TD Pipeline C-2 PDFAnonymous gGnr6a8iyWPas encore d'évaluation

- C2 - Archi - Processeurs - Définitions Et Concept Clefs - 2023Document36 pagesC2 - Archi - Processeurs - Définitions Et Concept Clefs - 2023Saamson StephenPas encore d'évaluation

- NKMAOCh 22020Document41 pagesNKMAOCh 22020Najah KAMMOUNPas encore d'évaluation

- ARM - Variables Et Acces MemoireDocument27 pagesARM - Variables Et Acces MemoireKraiem BrahimPas encore d'évaluation

- RES240 TP ns2Document5 pagesRES240 TP ns2asoubreadPas encore d'évaluation

- Table Des Matières IntroductionDocument18 pagesTable Des Matières IntroductionChaimae ElhaouariPas encore d'évaluation

- Chapitre 2Document17 pagesChapitre 2houda animationPas encore d'évaluation

- Python Pour MathsDocument11 pagesPython Pour Mathsmaxjalabert06Pas encore d'évaluation

- DS Mp1erta 2022Document5 pagesDS Mp1erta 2022Manar BjPas encore d'évaluation

- Archi Chap5Document18 pagesArchi Chap5Bakary CoulibalyPas encore d'évaluation

- Chapitre7 Complexité CPGEDocument22 pagesChapitre7 Complexité CPGEtouresette77Pas encore d'évaluation

- TD3 MicroprocesseurDocument2 pagesTD3 Microprocesseurالقرآن الكريمPas encore d'évaluation

- Assembleur ARM Full (+ Subroutine and Stack)Document60 pagesAssembleur ARM Full (+ Subroutine and Stack)wlabiodPas encore d'évaluation

- DS Corrigé Réseaux 2Document4 pagesDS Corrigé Réseaux 2Wissem Dhaouadi100% (2)

- FSMDDocument74 pagesFSMDdodo19876Pas encore d'évaluation

- ComplexitéDocument6 pagesComplexitéHaitam El FathiPas encore d'évaluation

- SynthDocument16 pagesSynthAZEDDINEPas encore d'évaluation

- Exercice PipelineDocument3 pagesExercice PipelineHamza Rahali100% (1)

- Intro VHDL v2.0 NotesDocument99 pagesIntro VHDL v2.0 NotesJalal RachadPas encore d'évaluation

- ReponsesDocument30 pagesReponses1K subscribers trust me you wont regret itPas encore d'évaluation

- Ccna Routage Et Commutation AvancesDocument4 pagesCcna Routage Et Commutation AvancesdavidPas encore d'évaluation

- Série de Révision Méthodologie de Conception Des ProcesseursDocument6 pagesSérie de Révision Méthodologie de Conception Des ProcesseursmezghaniPas encore d'évaluation

- TD1 Informatique IndustrielleDocument17 pagesTD1 Informatique IndustrielleToto Le boPas encore d'évaluation

- PV de Réunion-2 Rania ChtiouiDocument1 pagePV de Réunion-2 Rania ChtiouimezghaniPas encore d'évaluation

- Décrire un animalDocument2 pagesDécrire un animalmezghaniPas encore d'évaluation

- Report Article 13Document1 pageReport Article 13mezghaniPas encore d'évaluation

- evaluation sons wa et bDocument2 pagesevaluation sons wa et bmezghaniPas encore d'évaluation

- TD5Document2 pagesTD5mezghaniPas encore d'évaluation

- Fiche Autorisation Depot2020Document2 pagesFiche Autorisation Depot2020mezghaniPas encore d'évaluation

- TD1 ArchitectureDocument3 pagesTD1 ArchitecturemezghaniPas encore d'évaluation

- Monocycle PDFDocument1 pageMonocycle PDFmezghaniPas encore d'évaluation

- Emploi MP2ERTA - 20-21Document2 pagesEmploi MP2ERTA - 20-21mezghaniPas encore d'évaluation

- Cours 5 MulticycleDocument8 pagesCours 5 MulticyclemezghaniPas encore d'évaluation

- Examen SL 4Document6 pagesExamen SL 4mezghani100% (1)

- Cours 3 Architectures Des Jeux D'istruction RISCDocument10 pagesCours 3 Architectures Des Jeux D'istruction RISCmezghaniPas encore d'évaluation

- Examen SL 3Document2 pagesExamen SL 3mezghaniPas encore d'évaluation

- Architecture de 8086Document7 pagesArchitecture de 8086mezghaniPas encore d'évaluation

- Liste Des SociétésDocument9 pagesListe Des SociétésmezghaniPas encore d'évaluation

- Série de Révision Méthodologie de Conception Des ProcesseursDocument6 pagesSérie de Révision Méthodologie de Conception Des ProcesseursmezghaniPas encore d'évaluation

- Examen SL 1Document4 pagesExamen SL 1mezghaniPas encore d'évaluation

- Cours 1 Architectures Des CalculateursDocument12 pagesCours 1 Architectures Des CalculateursmezghaniPas encore d'évaluation

- Cours 4 Conception Des Processeurs MonocyclesDocument7 pagesCours 4 Conception Des Processeurs MonocyclesmezghaniPas encore d'évaluation

- Cours 2 Les MémoiresDocument5 pagesCours 2 Les MémoiresmezghaniPas encore d'évaluation

- Construction Métallique ExerciceDocument3 pagesConstruction Métallique ExerciceDjamiou BahogboPas encore d'évaluation

- Sujet MMDocument10 pagesSujet MMJordan TADONBOUPas encore d'évaluation

- Exemple Bulletin Primaire fDocument3 pagesExemple Bulletin Primaire fSeraphin KalambaPas encore d'évaluation

- État de Surface - WikipédiaDocument12 pagesÉtat de Surface - WikipédiaRemy AwomoPas encore d'évaluation

- Échange D'ions - Principe de BaseDocument18 pagesÉchange D'ions - Principe de BaseSoraya BouslahPas encore d'évaluation

- Synthese Nait Dbou AminaDocument3 pagesSynthese Nait Dbou Aminaamina n'aitPas encore d'évaluation

- Guide ENT EtudiantsDocument7 pagesGuide ENT EtudiantsعبداللهبنزنوPas encore d'évaluation

- Feuilletage 3225Document23 pagesFeuilletage 3225remedorguerbyPas encore d'évaluation

- Carnet de Santé Bucco-Dentaire PASO-ADocument28 pagesCarnet de Santé Bucco-Dentaire PASO-ATamtam ZehPas encore d'évaluation

- Syndrome EPEEDocument20 pagesSyndrome EPEEblinPas encore d'évaluation

- 6 Cours Energie ThermiqueDocument2 pages6 Cours Energie ThermiqueAbdo BdaPas encore d'évaluation

- GrammaireDocument2 pagesGrammaireMohamed DahaniPas encore d'évaluation

- Chapitre 1 TSL3Document22 pagesChapitre 1 TSL3farpoghXDPas encore d'évaluation

- Test Initial Clasa A XiaDocument7 pagesTest Initial Clasa A XiaSimion AlexandraPas encore d'évaluation

- Chapter 1: La Structure Des Solides Cristallins: Questions À AdresserDocument29 pagesChapter 1: La Structure Des Solides Cristallins: Questions À AdresserAbdellah MissoumiPas encore d'évaluation

- Pas À Pas Vicidial Injection List 06092019Document6 pagesPas À Pas Vicidial Injection List 06092019Aina Tanjona RandriambolarivoPas encore d'évaluation

- L'exploitation Des Ressources en Eau Dans La Cité Antique de Solonte (Sicile - Italie)Document533 pagesL'exploitation Des Ressources en Eau Dans La Cité Antique de Solonte (Sicile - Italie)desertkatherinePas encore d'évaluation

- Génération Y Et Transition DigitaleDocument3 pagesGénération Y Et Transition DigitalehindabdellaouiPas encore d'évaluation

- Diagrammes de Phases PDFDocument35 pagesDiagrammes de Phases PDFAlemPas encore d'évaluation

- IFACI - Le Contrôle Interne Du SIDocument70 pagesIFACI - Le Contrôle Interne Du SIrassouakPas encore d'évaluation

- TP Machine AsynchroneDocument3 pagesTP Machine AsynchroneOmar Smaili100% (1)

- Installation de COVADIS v13 PDFDocument20 pagesInstallation de COVADIS v13 PDFNacer Assam100% (1)

- 1er Devoir Du 1er Semestre Mathematiques 5ème 2018-2019 Ceg2 N'daliDocument1 page1er Devoir Du 1er Semestre Mathematiques 5ème 2018-2019 Ceg2 N'daliBabs BiPas encore d'évaluation

- Chapitre 2 - Cryptographie ClassiqueDocument11 pagesChapitre 2 - Cryptographie ClassiqueDO UAPas encore d'évaluation