Académique Documents

Professionnel Documents

Culture Documents

Cours 6809 CI

Cours 6809 CI

Transféré par

SoubkiTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cours 6809 CI

Cours 6809 CI

Transféré par

SoubkiDroits d'auteur :

Formats disponibles

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

"Microprocesseur

6809"

Plan du cours

I.1 Introduction

I.2 Architecture du microprocesseur

I.3 Architecture externe

Le schma fonctionnel

LUAL

Laccumulateur

Le compteur d'instructions

Le registre d'adresses

Le registre d'instructions

Le registre d'tat

Les registres temporaires de l'UAL

Les registres gnraux

La logique de contrle

II. Introduction au jeu d'instructions du microprocesseur

Le jeu d'instructions

Le code mnmonique

Les modes d'adressage

la pile

III. Les interruptions

IV. Les interfaces

le P.I.A. (Interface parallle)

Les mmoires

l'A.C.I.A. (Interface srie)

Master en Contrle et instrumentation

Page 1

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Historique

Le microprocesseur est l'aboutissement de progrs technologiques tant dans les

domaines mcanique, informatique et lectronique.

Quelques dates :

1690 : Pascal invente la machine calculer entirement

mcanique (addition et soustraction)

1800 : Jacquart invente le mtier tisser avec cartes

perfores.

1810 : Invention de l'orgue de barbarie (succession de cartes

perfores).

1940 : Premier ordinateur relais mcaniques (Navy)

1946 : Premier ordinateur tubes vide (1800).

1948 : Progrs de la physique quantique avec dcouverte de

l'effet transistor.

1950 : Ralisation des premires mmoires ferrites.

1958 : Dveloppement du premier circuit intgr (4 5 tr/puce).

1964 : Ordinateur transistors ( base de circuits TTL : 50

transistors dans une puce).

1970 : Premiers circuits L.S.I.- naissance du premier

microprocesseur 4 bits avec 1000 transistors sur une puce.

1975 : Naissance du microprocesseur Motorola 6800 (8 bits).

1980 : Apparition du microprocesseur 16 bits avec 50000

transistors sur la puce.

1984 : Apparition du microprocesseur 32 bits avec un million de

transistor sur la puce.

1994 : Apparition du Pentium avec 3,5 millions de transistors.

C'est en 1971 que le premier microprocesseur est sorti des laboratoires d'Intel.

Travaillant sur 4 bits et d'une puissance faible, l'intrt de ce nouveau

composant lectronique ne fut pas vident jusqu' ce que l'ide de le

transformer en calculatrice fut trouve.

Sept ans plus tard, l'arrive du 8088 multiplie dj cette puissance de calcul par

200.

Cette date correspond la naissance des vritables micro-ordinateurs. Arrivent

ensuite les microprocesseurs 68000 et 80286 (16 bits) avec les Macintosh et

P.C. que nous connaissons. Ils ont introduit l'image et le son.

Ensuite, tout n'est plus qu'une question de course la puissance de calcul.

Chaque bond technologique apporte sont innovation. Aujourd'hui, le multimdia

puis le 3 D et le temps rel. Demain, le monde virtuel.

Master en Contrle et instrumentation

Page 2

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Principes de base

Les premiers automatismes taient raliss partir de la logique cble selon le

synoptique suivant :

Les systmes logique cble sont conus l'aide de circuits intgrs logiques.

Certains de ces circuits font appel :

(Les sorties sont dfinies uniquement partir des variables d'entre)

(Les sorties dpendent toujours des entres mais aussi des tats antrieurs)

Master en Contrle et instrumentation

Page 3

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Le fonctionnement n'est plus dfini par un ensemble de circuits logiques, cbls

entre eux, mais par une suite ordonne d'instructions stockes en mmoire et

gres par cet lment.

Nouveau synoptique :

Principe de la logique programme

Illustration partir d'un circuit simple constitu de 3 cases mmoires et

3 portes logique ET, OU et NON.

On se propose de raliser la fonction : A exclusif B

Schma :

Initialisation [M1] = A et [M2] = B

Master en Contrle et instrumentation

Page 4

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Droulement :

Master en Contrle et instrumentation

Page 5

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Le microprocesseur

Dfinition : Le microprocesseur, not aussi M.P.U. (Microprocessor unit) ou

encore C.P.U. (Central Processing Unit) est un circuit intgr complexe

appartenant la famille des VLSI (Very Large Scale Intgration) capable

d'effectuer squentiellement et automatiquement des suites d'oprations

lmentaires.

Son rle : Ce circuit remplit deux fonctions essentielles :

Le traitement des donnes

On parle d'unit de traitement. Cette fonction est ddie l'U.A.L. Elle

concerne la manipulation des donnes sous formes de transfert, oprations

arithmtiques, oprations logiques....

Le contrle du systme

Cette fonction se traduit par des oprations de dcodage et d'excution des

ordres exprims sous forme d'instruction.

Puissance d'un microprocesseur

Dfinition : La notion de puissance est la capacit de traiter un grand nombre

d'oprations par seconde sur de grands nombres et en grande quantit.

Intrinsquement la puissance se joue donc sur les trois critres suivants:

La longueur des mots : donnes et instructions (on parle de largeur du bus

des donnes).

Le nombre d'octets que le microprocesseur peut adresser (on parle de

largeur du bus des adresses).

La vitesse d'excution des instructions lie la frquence de

fonctionnement de l'horloge de synchronisation exprime en MHZ.

Laspect dimensionnel renseigne assez bien de la puissance du composant.

Master en Contrle et instrumentation

Page 6

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

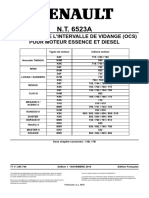

Familles des Microprocesseurs:

Systme base du microprocesseur 6809.

Master en Contrle et instrumentation

Page 7

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Description du microprocesseur 6809 :

Le microprocesseur 6809 est un processeur 8 bits, de haute gamme,

dont l'organisation interne est oriente 16 bits. Il est fabriqu en technologie

MOS canal N et se prsente sous la forme d'un botier DIL 40 broches. Il est

mono- tension (5V). Il existe en deux versions diffrencies par l'horloge.

Le 6809 est rythm par une horloge interne (f=1 MHZ, 1.5 MHZ et 2 MHZ).

Le 6809E est rythm par une horloge externe.

Ce dernier est adapt aux applications multiprocesseur. Il prsente la

particularit de pouvoir tre synchronis par une horloge extrieure.

Compatibilit complte entre les deux versions.

Master en Contrle et instrumentation

Page 8

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Prsentation du brochage :

Lalimentation (Vss - Vcc )

Le bus des donnes 8 bits (Do D7) : Ces huit broches sont

bidirectionnelles. Elles permettent la communication avec le bus des

donnes interne du microprocesseur. Chaque broche peut "piloter" une (1)

Master en Contrle et instrumentation

Page 9

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

charge TTL et 8 entres de circuits appartenant la famille 6800. Le bus

est en logique trois (03) tats.

Le bus des adresses 16 bits (Ao A15) : Ces broches unidirectionnelles

transfrent l'adresse 16 bits fournie par le microprocesseur au bus

d'adresse du systme. Mmes caractristiques lectriques que pour le bus

des donnes. Bus en logique trois tats.

NB : les adresses sont valides sur le front montant de Q.

Le bus de contrle :

des

: Cette broche indique le sens de transfert

donnes sur le bus des donnes. Ligne logique 3 tats.

Cette ligne est valide sur le front montant de Q.

- Les lignes d'tat du bus : BA (Bus Available) et BS (Bus State)

Information qui permet de connatre l'tat du microprocesseur tout

moment.

1er cas :

Le microprocesseur est en fonctionnement normal, il gre les bus d'adresses

et de donnes.

2eme cas :

Le microprocesseur est en phase de reconnaissance d'interruption pendant

deux cycles. Cet tat correspond la recherche des vecteurs d'interruption :

Re set , NMI , IRQ , SW1, 2 et 3.

3eme cas :

Ce signal apparat lorsque le microprocesseur rencontre l'instruction de

synchronisation externe (niveau bas sur SYNC). Il attend alors cette

Master en Contrle et instrumentation

Page 10

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

synchronisation sur une des lignes d'interruption. Les bus sont en haute

impdance pendant ce temps.

4eme cas :

Correspond l'arrt du microprocesseur (niveau bas sur HALT ). Le

microprocesseur laisse la gestion des bus des donnes et des adresses un

circuit annexe (contrleur de DMA). Les bus sont en haute impdance.

La ligne BA au niveau haut indique que les bus sont en haute impdance.

Broche d'initialisation Re set : Un niveau bas sur cette broche entrane

une rinitialisation complte du circuit.

Consquences :

Linstruction en cours est arrte ;

Le registre de pagination (DP) est mis zro ;

Les interruptions IRQ et FIRQ sont masques ;

Linterruption non masquable NMI est dsarme ;

Pour que cette ligne soit active, elle doit tre maintenue un niveau bas

durant un temps suffisamment long (plusieurs cycles d'horloge).

Le schma adopt est gnralement le suivant :

Le P.C. est initialis avec le contenu des vecteurs d'initialisation qui se

Trouvent aux adresses $FFFE et $FFFF. Ce contenu reprsente l'adresse du

dbut du programme qui sera Excut par le microprocesseur.

Master en Contrle et instrumentation

Page 11

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

La broche : HALT (Arrt du microprocesseur).

Un niveau bas sur cette broche provoque l'arrt du microprocesseur (mais

la fin de l'excution de l'instruction en cours). Il n'y a pas perte des donnes.

(BA = BS = 1)

Dans ce cas :

Les demandes d'interruption IRQ et FIRQ sont inhibes

Les demandes d'accs direct (DMA) la mmoire sont autorises.

Les demandes d'interruptions Re set et NMI sont prises en compte mais

leur traitement est diffr.

Les broches d'interruption :

NMI (No Masquable Interrupt)

IRQ (Interrupt Request)

FIRQ (Fast Interrupt Request)

Entres (actives sur un niveau

bas) qui peuvent interrompre le

fonctionnement normal du microprocesseur sur front descendant de Q.

Entres d'horloge XTAL et EXTAL (Extension crystal) :

La frquence du quartz (horloge)

microprocesseur.

est quatre fois la frquence du

Eout : reprsente le signal d'horloge commun au systme. Il permet la

synchronisation du microprocesseur avec la priphrie.

Qout : reprsente le signal d'horloge en quadrature avec Eout.

Les donnes sont lues ou crites sur le front descendant de Eout.

Les adresses sont correctes partir du front montant de Qout.

Master en Contrle et instrumentation

Page 12

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Broches complmentaires du bus de contrle :

MRDY (Memory ready) : Cette broche de commande permet d'allonger la

dure de Eout pour utiliser des mmoires temps d'accs long. Active sur

un niveau bas. l'allongement est un multiple de un quart de cycle et sa

valeur maximale est de 10 cycles.

DMA/BREQ : (Direct Memory Acces/Bus Request), Cette broche permet

de suspendre l'utilisation des bus du microprocesseur, pour faire de

l'accs direct ou du rafrachissement mmoire.

Fonctionnement :

Pendant que Q est au niveau haut (si DMA/BREQ bas) cela entrane l'arrt du

microprocesseur la fin du cycle en cours ... et non de l'instruction.

(BA = BS = 1 ce qui veut dire que tous les bus sont en haute impdance). Le

circuit ayant gnr cette commande dispose de 15 cycles machines avant que

le microprocesseur ne reprenne le contrle des bus.

Broches spcifiques au 6809 E

Entres d'horloge : EIN et QIN, Ce sont deux broches dans

lesquelles on applique des signaux identiques Eout et Qout du 6809.

Ces signaux doivent aussi tre fournis l'ensemble du systme

(signaux de synchronisation).

TSC (Tree States Control) : Cette broche a le mme rle que

l'entre DMA/BREQ prcdente. Possibilit de faire du DMA afin de

raliser des oprations de : rafrachissement

Partage de bus avec un autre microprocesseur

LIC (Last Instruction Cycle) : Cette broche de sortie est l'tat

haut pendant le dernier cycle de chacune des instructions excutes

par le microprocesseur. Le cycle qui suit ce signal est donc toujours un

cycle de recherche de code opratoire dune instruction.

Cette sortie au niveau haut signifie que le microprocesseur utilisera les bus

au cours du cycle suivant. La nature prdictive de ce signal permet

d'amliorer le fonctionnement d'un systme multiprocesseur bus partag.

Elle permet un contrle efficace des ressources communes d'un dispositif

multiprocesseur.

AVMA (Advanced Valid Memory Access) : (Contrle des ressources

communes en multiprocesseur), C'est une broche de sortie qui signale

un prochain accs au bus par le microprocesseur.

Master en Contrle et instrumentation

Page 13

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

BUSY (Occupation des bus) : Sortie mise au niveau haut pendant les

instructions du type : lecture, criture et excution du premier octet

d'un oprande constitu de deux octets (une adresse par exemple).

Dans un systme multiprocesseur, ce signal indique le besoin pour un

microprocesseur de disposer des bus au cours du prochain cycle pour

assurer l'intgrit de l'opration en cours. Cela vite l'adressage

simultan d'une mme zone mmoire par 2 microprocesseurs.

On ne doit pas activer TSC quand BUSY est actif.

Exemple d'application :

Architecture interne du microprocesseur 6809 :

Master en Contrle et instrumentation

Page 14

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Architecture interne du 6809

L'Unit Arithmtique et Logique :

Son rle : Ce circuit permet de traiter et tester les donnes. Toute

instruction qui modifie une donne fait toujours appel l'UAL. L'entre de

L'UAL est connecte au bus interne via un registre "temporaires" et un

registre particulier appel "accumulateur". La sortie de l'UAL est connecte

uniquement l'entre de l'accumulateur.

Noter :

Les deux entres sont prcdes par une mmoire tampon. On les appelle

encore des registres tampons ou verrou. Ces registres permettent de stocker

des octets aux entres de l'UAL. L'UAL tant constitu d'une logique

combinatoire, elle est dpourvue de moyen propre de stockage.

Ce type de registre ne peut tre manipul par le programmeur. Il lui est

totalement transparent.

La logique de contrle :

Appel encore Squenceur ou Unit de Contrle (U.C.)

Son rle : Permet tous les lments constitutifs du microprocesseur de

travailler ensemble et dans l'ordre.

Commentaires : La logique de contrle est pilote par le Registre

d'Instruction via le dcodeur d'instruction. Cette unit joue en quelque sorte

Master en Contrle et instrumentation

Page 15

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

un rle d'intendance puisqu'elle dcide de la disponibilit du bus tel ou tel

lment logique.

La logique de contrle possde une architecture complexe et trs

spcialise. L'lment central est reprsent par le dcodeur d'instructions

qui dcode les informations (premier octet) stockes dans le R.I. pour

gnrer les signaux ncessaires l'excution de l'instruction. La logique de

contrle gnre sur les lignes de contrle des niveaux logiques qui activent

les diffrents circuits environnant tels que mmoires et circuits I/O.

Cette unit fournit, partir d'un signal de rfrence qui est l'horloge,

tous les signaux de synchronisation utiles au bon fonctionnement de

l'ensemble. Cette horloge est cre partir d'un oscillateur interne qui utilise

un signal en provenance d'un quartz externe.

Deux actions complmentaires noter :

Le contrle de mise sous tension du microprocesseur (initialisation

des registres).

Le traitement des interruptions.

Rsum : Dune manire gnrale le rle de lunit de commande est Cherche,

dcode et excute les instructions :

Compose de circuits logiques et de temporisations, elle gre

le

fonctionnement et la synchronisation de tout le systme en gnrant le signal

d'horloge et les signaux internes ou externes (bus des commandes) au

microprocesseur.

Elle permet grer la squence le droulement des instructions

Elle cherche l'instruction dans la mmoire en envoyant l'adresse avec un

signal de lecture la mmoire

Elle dcode l'instruction et dtermine l'opration excuter

Gnre les signaux ncessaires l'excution de l'instruction

Prparation de l'instruction suivante.

Le Registre d'Instructions RI :

Sa tche : Le registre d'instructions contient le premier octet de

l'instruction en cours d'excution.

Commentaires :

Le registre est charg pendant le cycle de base extraction-excution. Il

reoit l'information (octet) grce au bus de donnes auquel il est connect.

L'information qu'il "capture" sur le bus des donnes est utilise par le

dcodeur d'instructions. Suivant le protocole ci-dessous :

La donne extraite de la mmoire est stocke dans le R.I. (c'est la phase

extraction). Ensuite ce contenu est interprt par le dcodeur d'instructions

qui agit alors sur la logique de contrle (c'est la phase excution).

Master en Contrle et instrumentation

Page 16

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Cet octet indique au microprocesseur deux choses :

Une action (une lecture, une criture ou autre ...)

Un lieu d'action (un registre, un accumulateur, une case mmoire...)

Le rsultat de cette interprtation se traduit par des niveaux logiques sur le

bus de contrle.

L'accumulateur :

C'est le registre le plus important du microprocesseur, il sert

systmatiquement lorsque le microprocesseur a besoin de "manipuler" des

donnes. La plupart des oprations logiques et arithmtiques sur les donnes

font appel au couple "UAL - accumulateur" selon la procdure suivante:

Il en est de mme pour les dplacements et transferts des donnes d'un

endroit un autre comme :

De mmoire mmoire.

De mmoire units d'entre-sortie (I/O).

Cette action se fait en deux temps : Source Vers Accumulateur et ensuite

Accumulateur vers destination.

Les instructions supportes par un accumulateur sont trs nombreuses. Au

niveau de la programmation, il reprsente une grande souplesse d'utilisation!

Les autres registres ne permettent que des oprations limites. Certains

microprocesseur, possdent des accumulateurs de longueur double tel D chez

Motorola et HL chez Intel - dissocis en deux et gnralement baptiss

individuellement A et B ou H et L respectivement.

Gros avantage prsent par un microprocesseur possdant plusieurs

accumulateurs : les oprations logiques et arithmtiques se font entre

accumulateurs limitant ainsi les accs (transferts) avec l'extrieur.

Les deux registres A et B sont interchangeables (mme rle/instruction)

sauf pour les instructions ABX et DAA et les oprations sur 16 bits.

Certaines instructions regroupent les registres A et B pour former un seul

accumulateur D de 16 bits. Dans ce cas l'accumulateur A reprsente l'octet

de poids fort et laccumulateur B loctet de poids faible.

Master en Contrle et instrumentation

Page 17

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Le Compteur d'Instructions :

Appel encore Compteur Programme (P.C.) ou Compteur Ordinal (C.O.)

Son rle : Pointer TOUJOURS le premier octet d'une instruction.

Commentaires : Le programme excuter est une succession d'instructions

ordonnes (chaque instruction pouvant prend plusieurs octets!) qui se trouve

rang dans une zone mmoire, gnralement des adresses successives. Le

P.C. "repre" le premier octet de chaque instruction du programme. La taille

du PC a une longueur de 16 bits ce qui lui permet d'adresser 65536 adresses

mmoire soit 64 k octets (le champ mmoire).

A la mise sous tension, une valeur particulire est dpose sur le bus

d'adresses (Dans le cas du 6809, cette valeur est $FFFE). Le contenu des

cases mmoires ($FFFE-$FFFF) reprsente en gnral l'adresse o se trouve

le premier octet de la premire instruction du programme.

Les registres pointeurs :

Les registres d'index (registres de 16 bits) Les registres d'index X et Y

sont utiliss pour les modes d'adressage index. Les donnes - 16 bitscontenues dans ces registres servent de pointeur de donnes (adresses). Ces

adresses "peuvent tre modifies" par une constante, prise comme valeur de

dplacement (offset) qui permet alors de calculer une adresse effective.

[Le pivot + offset] cela revient [X] ou [Y] + le dplacement, le contenu de

ces registres peut-tre incrment ou dcrment pour grer des donnes

stockes sous forme de table.

Les registres S et U (registres 16 bits) :

- Le pointeur de pile S (Systme) est utilis automatiquement par le

microprocesseur pour mmoriser l'tat de tous ces registres internes dans le

cas o il doit excuter un sous programme (d'interruption ou non).

- Le pointeur de pile U (Utilisateur) est gr exclusivement par le

programmeur pour effectuer, avec facilit, le passage des paramtres entre

programmes et sous programmes, (nanmoins, il peut-tre utilis pour

sauvegarder un contexte mais cette fois, ce n'est pas automatique).

Les registre U et S peuvent faire office de pointeurs - registres d'index.

Gestion de ces pointeurs :

Ces registres "pointent" toujours le haut de la zone mmoire qui leur est

attribue, (haut dans le sens adresse la plus grande).

On appelle cette zone une pile. Cette pile fonctionne en mode LIFO (Last In

First Out).

Master en Contrle et instrumentation

Page 18

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Remarque : (Le fonctionnement type premier entr - premier sorti

s'apparente plus au fonctionnement d'un pipeline appel pile FIFO (First In

First Out)).

Le Registre de Codes Condition (CCR) :

Ce registre donne tout instant l'tat des indicateurs (ou Flag) du

microprocesseur. Il y a deux types d'indicateurs : Les indicateurs sur la

nature des rsultats lis aux manipulations des donnes et les indicateurs lis

au fonctionnement en interruption.

Prsentation des diffrents indicateurs :

CCRb0 : (indicateur de retenue baptis : C). Indique l'existence d'une

retenue lors d'une opration arithmtique effectue par l'ALU.

CCRb1 : (indicateur de dbordement baptis : V). Il est mis 1 si le rsultat

en complment 2 d'une opration arithmtique dborde.

CCRb2 : (indicateur de rsultat nul baptis : Z). Il est mis 1 si le rsultat de

l'opration est nul. Cet indicateur est affect par les instructions de

chargement, de stockage, des oprations arithmtiques et logiques.

CCRb3 : (indicateur de rsultat ngatif baptis : N). Il recopie le bit de poids

fort (MSB) de l'octet contenu dans le registre avec lequel on vient de

travailler.

(Un rsultat ngatif en complment 2 positionne ce flag 1).

CCRb4 : (indicateur de masque dinterruption (Interrupt Mask) baptis : I).

cest le bit de masque de linterruption IRQ ; la mise un du bit I masque

linterruption IRQ

Master en Contrle et instrumentation

Page 19

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

CCRb5 : (indicateur de demi-retenue (Half curry) baptis : H). Il reprsente

le bit de demi-retenue. Il est utilis par l'ALU comme indicateur de retenue

entre les bits b3 et b4 (retenue du demi-octet le moins significatif) dans le

cas d'une addition sur 8 bits. Ce flag est pris en compte dans l'instruction

DAA pour raliser l'opration d'ajustement dcimal.

CCRb6 : (indicateur de masque dinterruption FIRQ (Fast Interrupt Mask)

baptis : F). La mise un du bit F masque linterruption FIRQ.

CCRb7 : (indicateur de sauvegarde des registres dans la pile, baptis : E). La

mise un du bit E indique la sauvegarde des diffrents registres dans la pile.

Exemple de sauvegarde de tous les registres avec S :

Registre de page (DP):

Registre de 8 bits, est prvu pour tendre la possibilit dadressage direct

tout lespace mmoire sous contrle du logiciel. Le contenu de ce registre

apparat sur les lignes A15- A8 (poids fort du bus dadresse).

Master en Contrle et instrumentation

Page 20

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Chapitre II :Programmation du 6809

II.1 Introduction :

Une instruction est code gnralement avec deux champ :

- champ d'opration (codeop)

- champ de code oprande

Code d'Instruction :

Code Opration Code Oprande

Une instruction peut tre simple : 1 octet, ou complexe : 4 octets.

La plupart des instructions permettent un traitement ou un dplacement des

donnes se trouvant en mmoire ou dans un registre.

L'ensemble des instructions de base, compris par le Registre d'Instruction, est

constitu de quelques 86 instructions. En tenant compte des variantes (modes

d'adressage) il atteint 1464 instructions.

1

Code opration

Octet1

Donne immdiate ou

Octet2

adresse dire cte /relative

Code opration

Octet1

Adresse sur 2 octets

ou

dplace me nt sur 2 octets

Octet2

Octet3

Octet2

Donne immdiate ou

Octet3

adresse dire cte /relative

Code opration

Octet1

Code opration

{

{

Adresse sur 2 octets

ou

dplace me nt sur 2 octets

Octet1

Octet2

Octet3

Octet4

Les divers modes de codage en mmoire des instructions et modes d'adressage.

Ces instructions font rfrence des donnes ou a des adresses de diverses

faons, ces rfrences tant les modes d'adressage dont dispose le

microprocesseur.

Master en Contrle et instrumentation

Page 21

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Structure d'une instruction :

Octeti

Octeti+1

Octeti+2

Octeti+3

code

post-octet

code oprande

facultatif

adresse

opratoire

ordre

oprations : arithmtique

expression directe ou indirecte

logique et de transfert

(modes d'adressage)

Dure d'une instruction : L'excution complte d'une instruction n'est pas

instantane, l'unit de mesure est la priode de l'horloge : encore appel

Cycle Machine .

Ex: Frquence de l'horloge E= 1 MHz donc T = 1 s.

La dure dpend de la complexit de l'instruction, son expression est :

= .

Mode de fonctionnement d'une instruction :

Excuter une instruction c'est en faite raliser le cycle suivant :

extraction- excution

Extraction : lecture de la donne en mmoire, = . avec priode de

l'horloge E

Il y a autant d'extractions que d'octets (code opratoire et code oprande)

constituant l'instruction.

Si m octets alors = .

Excution : traduction et interprtation de l'octet (code opratoire) une fois

extrait. Un octet donc = .

Master en Contrle et instrumentation

Page 22

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Linterprtation se fait selon le processus suivant :

Registre d'Instructi ons

D codeur d'Instructi ons

logi que de contrle

mi ssi on de si gnaux

vers le s circui ts

R/W

Registre

d'Adre sse s

Registre s

M moi re s Pri phri ques

e xtri eur

Compteur

A.L.U.

d'Instructions

i nt ri eur

Une priode TE supplmentaire est ncessaire pour raliser concrtement

l'opration demande.

La dure totale de l'excution d'une instruction est :

. + . + . ( + ).

Master en Contrle et instrumentation

Page 23

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Le jeu d'Instructions

Les instructions

caractristiques.

sont

rparties

en

groupes

dtermins

par

leurs

Classification :

Instructions de traitement des donnes

Instructions arithmtiques

1. Addition (DAA, ABX, ADC)

2. Multiplication (MUL)

3. Soustraction (SBC, SUB)

Exemples :

ADDD #$1200 avec (A)=$10 et (B)=$01, c--d (D)=$1001

SUB A # $02 avec (A)=$04

Instructions logiques

1. Rotation droite et gauche (ROL, ROR)

2. Dcalage droite et gauche (ASR, LSR et ASL, LSL)

3. Les fonctions logiques de base (AND, OR, EOR)

4. Lincrmentation/dcrmentation et complmentation (COM - NEG NOP - INC - DEC - CLR)

Exemples :

AND B # $55 avec (B)= $AA

Master en Contrle et instrumentation

Page 24

Cours Microprocesseur 6809

ASLA

avec (A)=$80

ASRA

avec (A)= $81

ROLA

avec (A)= $81

Dr. Lachouri Abderrazek

Instruction de transfert de donnes

a) transferts internes entre registres (EXG - TFR)

b) transferts externes avec la mmoire (LD - ST)

Exemples :

EXG A, B avec (A)= $10 et (B)= $01

Master en Contrle et instrumentation

Page 25

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

TFR A, B

LDA #$80

LDX #$1000

LDX $1000 avec ($1000)=$AA et ($1001)=$55

STA $2000 avec ($2000)=$45 et (A)=$60

Instructions de tests et de branchements : ces instructions sont

utilises pour raliser des tests de bits et des comparaisons. Les contenus

mmoires et accumulateurs ne sont pas modifis. Les rsultats de ces

instructions agissent uniquement sur les indicateurs du registre dtat.

a) instructions de tests sur un bit / un octet (BIT, TST)

b) instruction de comparaison (CMP)

c) instruction de branchement conditionnel

(branchement

les indicateurs du CCR sont actifs

Master en Contrle et instrumentation

si

Page 26

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Exemple :

CMPA

BCC

LDA

Loop LDB

END

#$20

Loop

#$10

#$AA

Instructions de branchement inconditionnel et de saut.

(provoquent la rupture de la squence sans condition)

a) saut relatif (BRA, BRN : 1 ou 2 octets)

b) saut absolu (JMP : 2 octets)

Exemple :

Debut CLRA

LDA

$1000

STA

$8000

BRA

Debut

Instructions dappel et de retour de sous-programme

Appel :

a) saut absolu (JSR)

b) saut relatif (BSR)

Retour : RTS

Le contenu (PC) sauvegard dans la pile est restitu dans le registre PC.

Reprise du programme lendroit o il a t interrompu.

Exemple :

CLRA

CLRB

LDA

STA

JSR

LDB

STB

HLT

SP1

LDA

STA

RTS

#$10

$1000

SP1

#$55

$1002

#$55

$2000

Master en Contrle et instrumentation

Page 27

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Instructions oprant sur les pointeurs U, S et X, Y.

a) Load effective adress (in register) : LEA.

Permet de manipuler des donnes sur 16 bits. Ces donnes reprsentent

gnralement des adresses.

Exemple :

LEAX avec (X)=$1010

Instructions oprant sur les pointeurs S et U

a) Empilement des registres dans la pile (PSH)

b) Dpilement des registres de la pile (PUL)

Aprs chaque sauvegarde/extraction,

dcrment/incrment de 1

Exemple :

PSHS A, X

le

pointeur

est

automatiquement

avec (S)= $1008, (A)= $22 et (X)=$2000

Dfinition d'une pile : Zone mmoire RAM gre par des pointeurs qui

permettent de transfrer rapidement des donnes dans des cases mmoires

selon un protocole bien tabli.

Ordre des actions :

Toujours suivie de loprande qui permet de slectionner les registres :

b7

PC U/S

b0

X

DP

CC R

e mpi lem en t

dpile me nt

Master en Contrle et instrumentation

Page 28

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Les modes d'adressage du 6809

Le microprocesseur 6809 possde 59 instructions de base. Combines avec le jeu

des modes dadressage (9 au total), elles fournissent 1464 codes opratoires

diffrents.

(Pour le 6800 ou 6802, on avait 72 instructions de base et 193 codes opratoire)

Les modes d'adressage sont :

ladressage

ladressage

ladressage

ladressage

ladressage

ladressage

ladressage

ladressage

ladressage

inhrent ou implicite

immdiat

tendu

tendu indirect

direct

par registre

index direct

index indirect

relatif

Au moyen des signaux quil gnre sur le bus dadresses, le microprocesseur a la

possibilit dadresser les divers circuits mmoires et interfaces, qui lui sont

connects au travers des bus afin d'accder leur contenu.

Cet accs se traduit par une opration dadressage

Cette opration peut se faire de plusieurs faons grce la prsence de

diffrents modes dadressage.

Remarque : La puissance dun microprocesseur dpend de son jeu dinstructions

mais aussi des ses modes dadressage.

Ladressage inhrent ou implicite

Ladressage inhrent est utilis par les instructions qui agissent seulement sur

les registres internes du microprocesseur. Ici, le code opratoire de linstruction

contient toute linformation dadressage ncessaire (adresse source ou/et

adresse destination).

Exemples :

Adressage par registre :

ABX, ASL, ASR, CLR, INC

Master en Contrle et instrumentation

Page 29

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Le code opratoire est immdiatement suivi dans la mmoire dun octet qui

dfinit un registre ou le jeu de registres devant tre utiliss par linstruction.

Cet octet est appel post-octet.

Le tableau ci-dessous prsente le codage de ce post-octet :

b7

b4

b3

b0

Source

Post-octet transfert/change

Exemple :

Destinataire

code

Registre

0000

0001

0010

0011

0100

0101

PC

1000

1001

1010

CCR

1011

DP

TFR X,Y (transfert de X dans Y).

CCR E F H I N Z V C

D

{AB

7

1F

12

X

Y

S

U

PC

Adr

Adr+1

Adr+2

DP

15

Master en Contrle et instrumentation

Page 30

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Adressage immdiat : La donne se trouve immdiatement aprs le code

opratoire de linstruction. La donne existe sous la forme de 1 ou 2 octets. (le

code opratoire est immdiatement suivi en mmoire de la donne sur laquelle

porte lopration)

Cet adressage concerne tous les registres internes sauf le DP.

Exemples :

LDA #$35

CCR E F H I N Z V C

D

X

Y

S

U

PC

{ AB

DP

35

7

adr

15

86

35

Adr

Adr+1

Adr+2

LDY#$1997

CCR E F H I N Z V C

D

X

Y

S

U

PC

{ AB

10

8E

19

1997

DP

15

97

adr

7

Adr+4

Adr

Adr+1

Adr+2

Adr+3

Adr+4

Adressage direct : On exprime le lieu de l'action par l'expression de l'adresse

effective. Le code oprande indique la partie basse de cette adresse. La partie

haute de ladresse est fournie par le contenu du Registre Direct de Page (DP).

Intrt : Ce mode ncessite moins de place mmoire (1 octet donc taille

mmoire rduite) par consquent lexcution de linstruction est plus rapide.

Master en Contrle et instrumentation

Page 31

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Remarque : Avec ce mode, la mmoire est dcoupe en 256 pages de 256 octets

chacune.

Ce mode est intressant dans le cadre des systmes dexploitation temps rel

multitche, o on alloue chaque tche une page.

Exemples :

LDA $97

Charge l'Accumulateur A avec le contenu dont l'adresse est forme

par [DP] et l'oprande

CCR E F H I N Z V C

D

adr

Adr+2

DP

Adr

Adr+1

X

Y

S

U

PC

96

97

37

A

B

37

1997

19

15

LDY $97

Charge le registre Y avec le contenu sur 16 bits dont les adresses

sont [DP] et partie basse et partie basse+1.

CCR E F H I N Z V C

D

10

9E

97

A

B

X

Y

S

U

PC

Adr

Adr+1

Adr+2

1960

adr

Adr+3

DP

15

19

7

Master en Contrle et instrumentation

19

60

1997

1998

Page 32

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Adressage tendu (direct) : On exprime le lieu de l'action par l'expression de

l'adresse effective. Le contenu des deux octets qui suivent immdiatement le

code opratoire spcifi reprsente ladresse (16bits) de la donne.

L'instruction occupe de 3 4 octets.

Exemples :

LDA $1997

Charge laccumulateur A avec le contenu de ladresse 1997.

CCR E F H I N Z V C

A

B

X

Y

S

U

PC

B6

19

97

37

adr

Adr

Adr+1

Adr+2

Adr+3

Adr+3

DP

15

37

1997

LDY $1997

Charge le registre Y avec le contenu de ladresse 1995.

CCR E F H I N Z V C

D

X

Y

S

U

PC

10

BE

19

A

B

0

97

1960

Adr

Adr+1

Adr+2

Adr+3

Adr+4

adr

Adr+4

DP

15

Master en Contrle et instrumentation

19

60

1997

1998

Page 33

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Adressage tendu indirect : Identique au mode dadressage tendu mais on

accde la donne en passant par une adresse intermdiaire spcifie aprs le

code opratoire. Les deux octets qui suivent le code opratoire pointent une

adresse dont le contenu reprsente ladresse de la donne recherche.

Le code opratoire est form de deux octets - le post-octet est toujours $9F.

Exemples :

LDA [$1997]

Chargement de laccumulateur A avec le contenu dont

ladresse se trouve en 1997-1998.

CCR E F H I N Z V C

D

A

B

A6

9F

19

1960

37

X

Y

S

U

PC

37

97

Adr

Adr+1

Adr+2

Adr+3

Adr+4

adr

Adr+4

DP

15

19

60

1997

1998

LDY [$1997]

Chargement du registre Y avec le contenu dont l'adresse

(partie haute) se trouve en $1997.

CCR E F H I N Z V C

D

{AB

7

X

Y

S

U

PC

37

60

10

AE

9F

1960

1961

3760

adr

19

Adr+2

Adr+3

97

Adr+4

19

60

1997

1998

Adr+4

DP

15

Adr

Adr+1

Master en Contrle et instrumentation

Page 34

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Adressage index

Deux possibilits :

Adressage index direct et indirect

Dans ce mode, les registres pointeurs (X, Y, U, S et PC) sont utiliss pour

effectuer le calcul de ladresse effective de la donne recherche.

Il existe 5 types dadressage index.

Ladressage index avec dplacement nul

Ladressage index avec dplacement constant (non nul).

Ladressage index avec dplacement accumulateur

Ladressage index avec auto-incrmentation/dcrmentation

Ladressage index relatif au Compteur Programme (PC)

Loctet qui suit le code opratoire (le post-octet) spcifie :

La nature de lindexation

Le type dadressage (direct ou indirect)

Le registre pointeur utilis.

Loctet qui suit le code opratoire (le post-octet) spcifie :

1. La nature de lindexation

2. Le type dadressage (direct ou indirect)

3. Le registre pointeur utilis.

Le tableau ci-joint montre le format de ce post-octet.

Master en Contrle et instrumentation

Page 35

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Tableau 1 : Format du registre post octet du mode dadressage index.

Les bits du registre post-octet

Mode dadressage

index

7

6

5

4

3

2

1

0

0

R

R

d

d

d

D

d

EA = R + 5 bits Offset

1

R

R

0

0

0

0

0

,R+

1

R

R

1

0

0

0

1

,R++

1

R

R

0

0

0

1

0

,-R

1

R

R

1

0

0

1

1

,--R

1

R

R

1

0

1

0

0

EA = R + 0 Offset

1

R

R

1

0

1

0

1

EA = R + ACCB Offset

1

R

R

1

0

1

1

0

EA = R + ACCA Offset

1

R

R

1

1

0

0

0

EA = R + 8 bits Offset

1

R

R

1

1

0

0

1

EA = R + 16 bits Offset

1

R

R

1

1

0

1

1

EA = R + D Offset

1

X

X

1

1

1

0

0

EA = PC + 8 bits Offset

1

X

X

1

1

1

0

1

EA = PC + 16 bits Offset

1

R

R

1

1

1

1

1

EA = [, Adresse]

Champ du mode dadressage

Champ indirect (bit signe B7=0)

Champ du registre RR

00=X

01=Y

10=U

11=S

X= dont care

0 not indiretc1

D=Offset

1 indirect

Index a offset constant:

5 bits (-16 +15) ;

8 bits (-128 127) ;

16 bits (-32768 +32767) ;

Constitution du post-octet.

b7=1

b4 : indicateur d'indirection o non

b4 = 1 : mode indirect

b4 = 0 : mode direct

b7=0

b4 reprsente le signe

b5 et b6 reprsente le registre concern

b0,b1,b2 et b3 indiquent le mode dadressage.

Master en Contrle et instrumentation

Page 36

Cours Microprocesseur 6809

Non indirect

Assembler

Postbyt

form

opcode

Type

Forms

Constant offset from R

(2s complement

offsets)

No Offset

5-bits off

8-bits off

16-bits off

A reg offset

B reg offset

Dreg offset

Incr by 1

Incr by 2

Decr by 1

Decr by 2

8-bits offset

16-bits off

16-bits adr

Accumulator offset

from R (2s complement

offsets)

Auto

increment/decrement

R

Constant offset from

PC (2s complement off)

Extended indirect

Dr. Lachouri Abderrazek

,R

n,R

n,R

n,R

A,R

B,R

D,R

,R+

,R++

,-R

,--R

n,PCR

n,PCR

-

1RR00100

0RRnnnnn

1RR01000

1RR01001

1RR00110

1RR00101

1RR01011

1RR00000

1RR00001

1RR00010

1RR00011

1xx01100

1xx11100

-

+

#

indirect

Assembler

Postbyt

form

opcode

0

1

1

4

1

1

4

2

3

2

3

1

5

-

0

0

1

2

0

0

0

0

0

0

0

1

2

-

[,R]

1RR10100

Defaults to 8-bits

[n,R]

1RR11000

[n,R]

1RR11001

[A,R]

1RR10110

[B,R]

1RR10101

[D,R]

1RR11011

Not allowed

[,R++]

1RR10001

Not allowed

[,--R]

1RR10011

[n,PCR]

1xx11100

[n,PCR]

1xx11101

[n]

10011111

+

#

4

7

4

4

7

1

2

0

0

0

6

4

8

5

0

1

2

2

R= X, Y, U or S

X= dont care

RR

00=X

01=Y

10=U

11=S

Adressage index dplacement nul

Le registre pointeur contient ladresse effective (A.E.) de la donne.

Un chargement pralable du registre est impratif.

Exemple : LDA O,X ou LDA ,X

CCR E F H I N Z V C

D

X

Y

S

U

PC

A

B

A6

84

37

7

Adr+2

1997

adr

Adr+1

DP

15

Adr

Adr+1

37

1997

Lgende de la valeur $84 soit 1 00 0 0100 du post-octet (ligne numro 6 du

tableau).

Adressage index dplacement constant

Master en Contrle et instrumentation

Page 37

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Ladresse effective de la donne est la somme du dplacement (constante en

complment deux) et du contenu du registre nomm pris comme base.

A.E. = [Registre nomm] + expression du dplacement.

Le contenu du registre nest pas modifi.

Syntaxe :

Un code opratoire + un post-octet + un oprande.

Trois formes sont possibles selon l'expression de la valeur de la constante qui

suit le post-octet.

Le dplacement s'exprime sur 4 bits + un bit de signe.

Le dplacement est compris dans l'intervalle [-161O 151O]

Le post-octet suffit.

Exemple : LDA -2, X

Code

A6

1E soit 0 00 1 1110

Le dplacement s'exprime sur 7 bits + un bit de signe. Le dplacement est

compris dans l'intervalle [-1281O 1271O]. Un octet supplmentaire aprs le

post-octet est ncessaire.

Exemple : LDA 53,X

Code

A6

88 soit 1 00 0 1000

35 (5316)

Le dplacement s'exprime sur 15 bits + un bit de signe.Le dplacement est

compris dans l'intervalle [-327681O +327671O]. Deux octets supplmentaires

aprs le post-octet sont ncessaires.

Exemple : LDA $997,X

Code

A6

89 soit 1 00 0 1001

09

97

Adressage index avec dplacement accumulateur.

Ce mode est semblable au mode prcdent except que la valeur du dplacement

(exprim en complment 2) se trouve dans un accumulateur afin dtre ajout

au contenu du registre pointeur nomm pour former lA.E. de la donne.

Les contenus de laccumulateur et du pointeur ne sont pas modifis par cette

addition.

Master en Contrle et instrumentation

Page 38

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Cest le post-octet qui spcifie laccumulateur utilis (pas doctet

supplmentaire).

Intrt : la valeur du dplacement est calcule par le programme en cours

dexcution, en fonction des vnements.

Exemples :

LDA B,X

avec post-octet = $85 soit 1 00 0 0101.

Chargement du registre A avec le contenu se trouvant l'adresse

exprime par la somme des contenus des registres B et X.

CCR E F H I N Z V C

D

A

B

A6

85

00

37

X

Y

S

U

PC

Adr

Adr+1

Adr+2

1960

+

adr

adr+2

00

1997

DP

15

LDX D,Y

avec post-octet = $AB soit 1 01 0 1011.

Charge le registre X avec le contenu se trouvant l'adresse exprime par

la somme des contenus des registres D et X ainsi que D+1 et X.

CCR E F H I N Z V C

D

A

B

X

Y

S

U

PC

AE

AB

09

97

0

2000

1000

Adr+2

adr

adr+2

DP

15

Adr

Adr+1

20

00

1997

1998

Master en Contrle et instrumentation

Page 39

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Adressage index avec auto-incrmentation/dcrmentation

Le registre concern contient ladresse de la donne. En plus de l'utilisation en

mode index avec dplacement nul, il est possible de modifier le contenu du

registre selon le mcanisme suivant :

La pr-dcrmentation

Le pointeur est dcrment de un ou deux avant utilisation.

La post-incrmentation : Le pointeur est incrment de un ou de deux aprs

utilisation. Dans tous les cas, le contenu du registre est modifi.

Intrt : Une incrmentation/dcrmentation permet de grer des tables de

donnes 8 bits (octets).

Deux incrmentations/dcrmentations permettent de grer des tables de

donnes de 16 bits (mots ou adresses).

Les aspects pr-dcrmentation et post-incrmentation sont trs utiles pour

crer des piles logicielles supplmentaires dont le comportement est identique

celui des piles S et U (hardware). (gestion efficace de blocs-mmoire organiss

en donnes 8 bits ou 16 bits)

Exemples :

LDA 0,-X

Code

A6

82 soit 1 00 0 0010

Chargement de l'accumulateur A avec le contenu se trouvant l'adresse

exprime par le contenu de X dcrment de 1.

LDY 0,--X

Code

10

AE

83 soit 1 00 0 0011

Chargement du registre Y avec le contenu se trouvant l'adresse exprime par

le contenu de X dcrment deux fois.

LDA 0,X+

Master en Contrle et instrumentation

Code

A6

80 soit 1 00 0 0000

Page 40

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Chargement de l'accumulateur A avec le contenu se trouvant l'adresse

exprime par le contenu de X. Aprs le chargement, le contenu de X est

incrment de 1.

LDD 0,X++

Code

EC

81 soit 1 00 0 0001

Chargement de l'accumulateur D avec le contenu se trouvant l'adresse

exprime par le contenu de X. Aprs le chargement, le contenu de X est

incrment deux fois.

Adressage index relatif au compteur-programme (PC)

Un programme qui contient des instructions exprimes dans le mode tendu ou

direct, faisant rfrence des adresses situes lintrieur de sa zone

dimplantation en mmoire ne pourra pas tre excut si lon transfre son code

objet dans une autre zone mmoire.

On dit, dans ce cas, que le programme nest pas translatable.

Cet inconvnient peut-tre vit en utilisant le mode dadressage index avec

dplacement relatif au PC.

Syntaxe :

code opratoire destination-(adr+4), PC

l'expression de "destination-(adr+4)" est code en complment 2.

Exemples :

Chargement du registre A avec le contenu se trouvant l'adresse $1997.

Code

$1000

adr

adr+1

adr+2

adr+3

A6

8D

09

93

soit 1 00 0 1101

Justification :

Si adr=$1000 alors destination ($1997) est gale $1997-$1004 soit $993.

Master en Contrle et instrumentation

Page 41

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Il faut tenir compte de la longueur de l'instruction puisque le PC pointe toujours

l'instruction suivante.

LDA $FO,PC

Chargement de laccumulateur A avec le contenu mmoire dont ladresse est la

valeur de PC + $FO.

Code

adr

adr+1

adr+2

A6

8C

F0

soit 1000 1100

La donne se trouve l'adresse (adr+3)-$10 donc en amont du programme.

Avantage du mode index relatif au PC :

Si lensemble du programme est charg une autre adresse, le mme code objet

permet toujours de retrouver la donne dans le corps du programme et dobtenir

ainsi une excution correcte.

Le mme traitement appliqu lensemble des instructions du programme, le

rendra entirement translable et totalement indpendant de son implantation

physique dans la mmoire. Les adresses des donnes tant toutes refrences

par rapport la valeur relle du PC au moment de lexcution.

Lutilisation dune tiquette facilite l'emploi de ce mode.

Illustration :

LEAX ETIQ, PC

Chargement du registre X avec le contenu dont l'adresse est exprime par la

valeur issue de l'opration ETIQ-(adr+4).

Code du post-octet : $8D soit 1 00 0 1101

Master en Contrle et instrumentation

Page 42

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

CCR E F H I N Z V C

D

30

A

B

X

Y

S

U

PC

8D

00

11

1122

adr

Adr = $1000

Adr+1

Adr+2

Adr+3

Adr+4

adr+4

DP

15

11

12

ETIQ = $2015

Dplacement = $2015 -($1000+4) soit 11

Adressage index indirect.

Dans ce mode, lAdresse Effective est contenue lemplacement indiqu par le

contenu du registre dindex utilis auquel on additionne le dplacement.

Ici, lA.E. transite par une adresse intermdiaire.

Syntaxe :

A.E(H)={[Registre] + expression du dplacement}.

A.E(L)={[Registre] + expression du dplacement+1}.

Tous les modes dadressage index peuvent travailler en indirection sauf les

modes :

auto-incrmentation/dcrmentation par 1

dplacement constant cod sur 5 bits

Illustration :

LDA [$960,X]

Chargement de A avec le contenu mmoire dont ladresse est le contenu de

[X+960, X +961].

Master en Contrle et instrumentation

Page 43

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

CCR E F H I N Z V C

D

X

Y

S

U

PC

A6

99

09

60

37

A

B

1OOO

adr

Adr

Adr+1

Adr+2

Adr+3

Adr+4

adr+4

DP

15

19

97

1960

1961

37

1997

Quelques exemples :

Adressage index indirect avec dplacement nul.

LDA [0,X]

Chargement de A avec le contenu mmoire dont ladresse est [X, X +1].

Adressage index indirect avec dplacement constant.

LDA [$35,X]

Chargement de A avec le contenu mmoire dont ladresse est [X+$35, X +$36].

Adressage index indirect avec dplacement accumulateur.

Le dplacement exprim en complment deux est contenu dans A, B ou D.

LDU [D, Y]

Chargement du registre U avec le contenu mmoire dont ladresse est

[Y+D] et [Y+D+1]

Adressage index indirect avec double auto-incrmentation/dcrmentation.

ADDA [ , U++]

Master en Contrle et instrumentation

Page 44

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Addition du contenu de A et du contenu-mmoire dont ladresse est [U] et [U+1],

suivi de deux incrmentations.

Adressage index indirect relatif au compteur programme.

Les dplacements sont cods sur 8 ou 16 bits en complment 2.

LDA [$1997, PC]

Chargement de A avec la valeur dont ladresse est la valeur issue de

l'opration PC + $1997.

Adressage relatif

Technique dadressage utilise avec les instructions de branchement conditionnel

ou non.

Constitution :

adr. relatif court

adr. relatif long

code opratoire

1 octet

1 octet + $10

code oprande

1 octet

2 octets

Le code opratoire reprsente le test et le type de branchement (court ou long :

$10) raliser. Le code oprande reprsente le dplacement sign qui est ajout

au contenu du PC. Dans le mode d'adressage relatif court, le dplacement est

exprim sur un octet en complment deux : -128 dplacement +127

Dans le mode d'adressage relatif long, le dplacement est exprim sur deux

octets en complment deux : -32768 dplacement +32767

Ralisation de l'Adresse Effective : Adresse Effective = PC +2(4) + dplacement

(PC+2)- valeur dplacement (PC+2)+ valeur

Dans la syntaxe assembleur il faut rajouter un (L) comme prfixe dans le cas

d'un saut long.

Master en Contrle et instrumentation

Page 45

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Quelques exemples :

Adressage relatif court avec un dplacement positif.

BEQ LOOP

branchement si Z=1

?

CCR E F H I N 1 V C

D

27

A

B

33

0

X

Y

S

U

PC

Adr = $1960

Adr+1

Adr+2

+35

adr

op

Adr+2

$1997

DP

15

Valeur = $1997-($1960+2) soit $35

Adressage relatif long avec un dplacement positif.

?

CCR E F H I N 1 V C

D

10

A

B

X

Y

S

U

PC

26

16

7B

adr

Adr+2

Adr+3

Adr+4

+1675

Adr+4

DP

15

Adr = $1997

Adr+1

op

7

$3010

Valeur = $3010-($1997+4) soit $1675

Master en Contrle et instrumentation

Page 46

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Principe de fonctionnement :

Cellules mmoires

code opratoire

Compteur ordinal

Registre d'Instruction

Dcodage

Logique de contrle

Squenceur

de commandes

Excution

Fonctionnement squentiel

La ralisation de toute instruction s'effectue selon le cycle extractionexcution qui se dcompose comme suit :

1er temps : Phase d'extraction

Recherche de linstruction suivie du dcodage

2me temps : Phase d'excution

Excution du code opratoire

Cette tape est plus ou moins longue suivant la complexit de l'instruction.

Master en Contrle et instrumentation

Page 47

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Chaque opration lmentaire constituant ce cycle est valide par un signal

dhorloge.

Illustration :

Extraction

(fetch)

Excution

Horloge E

cycle machine

dpot de

l'adresse

puis

stockage

du code

dans le R.I.

dcodage

du code

ralisation de

l'action

demande

Simulations :

Premier exemple :

$0000

$0002

LDA

ADDA

#$10

#$29

$0004

NOP

12

86

8B

10

29

Deuxime exemple :

$0000

$0003

$0006

LDA

ADDA

STA

$0014

$0016

$0018

#

3

3

3

$0009

$000C

$000F

$0012

LDA

ADCA

STA

BRA

$0015

$0017

$0019

$FE

3

3

3

2

Master en Contrle et instrumentation

~

5

5

5

5

5

5

3

Page 48

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Commentaire :

PC

00

0C

registre interne

intermdiaire

registre

des

adresses

00

00

00

15

0A

0B

Bus des adresses

Apport du 6809 dans la famille des microprocesseurs 8 bits :

Son architecture et ses diffrents modes dadressage permettent daborder des

concepts logiciels tels que :

La gnration de programmes translatables, rentrants et structurs.

Prsentation de ces concepts :

1- Dfinition d'un programme translatable

Ce type de programme fonctionne quelque soit ladresse laquelle il est implant

en mmoire. Ce ci est possible grce aux modes dadressage relatif (BSR, BRA)

et index par rapport au PC (LDA valeur, PC).

L'avantage de ce mode de programme est qu'il est utilisable dans n'importe

quelle application.

Le principe du programme relogeable existe aussi. Dans ce cas, ( la diffrence

du cas prcdent) les adresses relatives sont transformes en adresses absolues

aprs dition des liens.

Master en Contrle et instrumentation

Page 49

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

2- Dfinition d'un programme rentrant.

Un programme rentrant est un programme qui peut-tre utilis nimporte quel

niveau de priorit (Pour cela il doit tre interruptible).

Dans ce cas, le programme dinterruption peut utiliser la mme squence de

programme que celle quil vient dinterrompre. Il ne doit pas perturber les

informations et rsultats de la tche interrompue. ncessit dutiliser deux

zones de sauvegarde des donnes.

Le concept de rentrance est possible avec un microprocesseur possdant

plusieurs pointeurs de pile pour grer plusieurs zones de sauvegarde.

Rendu possible avec l'existence des instructions de manipulation de pile

hardware PSH et PUL et logicielle STA, -X et LDA, X+.

Equivalence :

LDX

STX

,U++

,--U

quivalent

quivalent

PULU

PSHU

X

X

LDA

STA

,U+

,-U

quivalent

quivalent

PULU

PSHU

A

A

Illustration :

Sauvegarde

du contexte

dans la pile U

Procdure

Appel

procdure

Programme

d'interruption

Sauvegarde

du contexte

dans la pile S

Master en Contrle et instrumentation

Page 50

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Les langages de programmation :

Un langage est un ensemble de rgles ou commandes utilises par un

programmeur afin de raliser un programme crit tout d'abord sous la forme

d'un algorithme et ensuite traduit par un organigramme.

Le langage volu

Les critres pris en compte lors du choix dun langage sont :

le temps de programmation

la maintenance

la transportabilit

Un programme crit dans un langage volu donn peut tre implant

"facilement" sur diverses machines sans rcriture. (compilateurs appropris)

Un programme crit dans un langage volu est traduit en binaire de deux

manires diffrentes.

En faisant appel soit un interprteur soit un compilateur.

Tous deux sont des programmes puissants de traduction.

Un interprteur agit pendant lexcution du programme. Chaque ligne du

programme est traduite en instruction binaire juste avant son excution.

A mesure quune ligne est excute, la traduction de la ligne suivante commence.

Un compilateur traduit dabord le programme en langage hexadcimal et ensuite

le code gnr est sauvegard sous la forme dun nouveau programme binaire.

(ressemble beaucoup un assembleur).

Le compilateur prsente linconvnient par rapport linterprteur, de ncessit

beaucoup plus de mmoire mais par contre il est beaucoup plus rapide

lexcution.

Lapprentissage dun langage volu ne rapporte strictement rien en ce qui

concerne la connaissance de larchitecture fondamentale dun microprocesseur.

Par contre la programmation langage machine ou assembleur ncessite une bonne

connaissance de larchitecture du microprocesseur.

Quelles sont les raisons pour lesquelles on choisit un langage moins volu?

Deux raisons cela :

Master en Contrle et instrumentation

Page 51

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Gain en place mmoire : Le langage volu ncessite pour effectuer la

mme tche beaucoup plus dinstructions machines.

Exemple : une simple instruction du type WRITELN peut faire appel une

centaine dinstruction. Ainsi plus despace-mmoire est ncessaire.

Gain de temps lexcution : Plus dinstructions de base implique un temps

dexcution plus lent moins de disposer de microprocesseur puissant

(rapide) avec un grand champ mmoire.

Le langage dassemblage

Ce langage est lintermdiaire entre un langage volu comme C ou Pascal et le

langage machine. Le langage dassemblage est li au microprocesseur. Chaque

processeur possde son propre ensemble dinstructions.

Ses avantages :

minimise le code

meilleur contrle sur le matriel.

[bien adapt lcriture des routines dentres/sorties]

Lassembleur est un petit compilateur. Ce langage sappuie sur labrviation de

terme anglais pour chaque instruction.

Exemple de la fonction de remise zro (CLEAR) : CLR

Vocabulaire

Le langage dassemblage : C'est un langage constitu dinstructions et de

pseudo-instructions. Un programme crit dans ce type de langage est une

suite de lignes symboliques crites dans un ordre logique.

Lassembleur : Cest un programme de traduction qui traite chaque ligne du

programme source pour fournir le code machine. Il dtecte les erreurs. Le

rsultat de son travail sappelle le programme objet.

Macro-assembleur : Cest un assembleur qui permet de traiter des macroinstructions : ensemble dinstructions regroupes sous formes de fonction.

Cross-assembleur : Cest un assembleur qui permet de dvelopper en

langage dassemblage, une application utilisant un microprocesseur donn

Master en Contrle et instrumentation

Page 52

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

laide dun systme possdant un microprocesseur diffrent. Le systme,

dit hte, engendre du code machine pour le microprocesseur cible.

Intressant pour les petits systmes car dans ce cas, on bnficie des

avantages dun systme plus important : Editeur, Systme dexploitation,

etc...

Dsassembleur : C'est un logiciel qui travaille linverse de lassembleur. A

partir dun programme machine, il construit le langage mnmonique.

Exemple : $86 traduction de LoaD accumulateur A.

Lassembleur 6809 : Le langage dassemblage est un langage de

programmation utilise dans les systmes de dveloppement, dispositifs daide

lcriture de programmes. Il permet de traduire un programme source crit en

langage symbolique (ou mnmonique) en un langage binaire.

Cette opration appele "Assemblage" est ralise par un programme appropri

appel "Assembleur".

Il gnre directement un programme excutable par le microprocesseur encore

appel "programme objet".

Comme tout langage, ce dernier possde une syntaxe et un vocabulaire propres

quil est indispensable de connatre afin dtablir le programme source.

Syntaxe du langage assembleur : Chaque ligne dinstruction du programme

comporte quatre parties appeles "champs". Chaque champ est spar par un

blanc (espace).

Illustration :

Etiquette

Code

Code

Commentaire

opratoire

oprande

_________________________________________

Master en Contrle et instrumentation

i+2

j+2

Page 53

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Dfinition des diffrents champs :

Etiquette : Ce champ nest pas obligatoire.

Une tiquette est un symbole dau plus 6 caractres alpha-numriques,

commenant obligatoirement par une lettre de lalphabet.

Dans le cas, o le champ tiquette est vide au moins un blanc doit prcder le

champ suivant. Si le 1er caractre de la ligne est une *, la ligne est alors

considre comme un commentaire.

Le rle de ltiquette est de permettre de reprer la position dune instruction

dans le programme.

Le champ opration : Il contient soit un code mnmonique de lopration

effectuer soit une directive dassemblage.

Le champ oprande : Il complte le champ opration et contient la "donne"

ncessaire lexcution de linstruction.

Sa syntaxe est varie et dpend du mode dadressage attribu linstruction.

On trouve :

des tiquettes (des noms)

des symboles (nom de registre)

des nombres

des expressions : Combinaison des 3 lments ci

dessus.

Les nombres peuvent tre reprsents dans diffrentes bases dcimale,

octale(@), hexadcimale ($) et binaire (%).

Lidentificateur de la base seffectue grce un suffixe ou un prfixe dans le

cas de certain assembleur (H).

Sans indication particulire, un nombre est interprt comme un dcimal.

Les expressions : Elles se composent dune suite de nombres et de symboles

spars par des oprateurs logiques, arithmtiques et des parenthses.

Elles servent spcifier une valeur selon les rgles de la logique et de

larithmtique.

Master en Contrle et instrumentation

Page 54

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Le champ commentaire : facultatif, il permet de documenter le programme.

Tous les caractres dcriture disponibles dans l'diteur sont utilisables.

Les directives dassemblage :

Une directive dassemblage (ou pseudo-instruction) est une commande que le

programmeur utilise pour donner des directives lassembleur et qui agit sur le

processus dassemblage. On distingue 5 catgories de directive.

Affectation de symboles : EQU et SET

Gestion de lespace mmoire : ORG et RMB

Inscription de constantes en mmoire : FCB, FDB et FCC

Assistance la programmation : END et OPT

Prsentation des listings : TITLE et PAGE

EQU : affectation dune valeur un symbole ou tiquette

Syntaxe :

Symbole

EQU Expression

Rle :

Cette directive affecte au symbole situ dans le champ tiquette la valeur

(8 ou 16 bits) de lexpression place dans le champ oprande.

Les symboles utiliss avec EQU ne peuvent pas tre redfinis dans la suite du

programme.

SET : affectation temporaire dune valeur un symbole.

Rle :

SET est semblable EQU except que laffectation est temporaire. Les

symboles dfinis avec cette directive peuvent tre nouveau dfinis par la suite

dans le mme programme.

Exemples :

ARG

ARG

ARG

SET

SET

SET

$2

ARG*$2

ARG*ARG

ARG=$2

ARG=$4

ARG=$10(1610)

ORG : Origine (initialisation du compteur programme)

Syntaxe :

ORG Expression

Master en Contrle et instrumentation

Page 55

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Rle :

Dfinition dune adresse dorigine.

Charge le PC la valeur spcifie par lexpression situe dans le champ oprande.

Remarque : Plusieurs ORG peuvent-tre utiliss dans un mme programme

source.

On structure ainsi lespace mmoire en blocs :

le programme principal

les sous programmes

la gestion des interfaces

Chaque bloc est initialis par un ORG.

RMB : Reserve Memory Bytes (Rservation doctets en mmoire)

Syntaxe :

Symbole

RMB

Expression

Rle :

Provoque lors de lassemblage un "saut" du PC, dun nombre doctets gal

la valeur de lexpression.

Le but tant de rserver une zone mmoire pour un usage particulier.

FCB : Form Constant Byte (dfinition dune constante dun octet)

Syntaxe :

Symbole

FCB expr1, expr2...

Rle :

Inscrit la valeur exprime sur 8 bits des expressions du champ oprande

dans les cases mmoires dfinies par la valeur du PC.

Pour chaque criture en moire : PC = PC+1

Remarque : Les expressions peuvent tre numriques ou alphanumriques. Le

symbole ' plac devant le caractre, le dsigne comme tant alphabtique, dans

ce cas, le code ASCII est mis en mmoire.

Master en Contrle et instrumentation

Page 56

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Exemples :

DATA

DIX

ORG

FCB

FCB

FCB

FCB

EQU

LDX

END

$4000

1,$62+$48,'A,'B

$FF

'4,$4

DIX+2

$A

DATA

$4000

01

AA

41

42

FF

34

04

0C

8E

40

00

FDB : Form Double Byte Constant (dfinition dune constante de deux octets)

Syntaxe :

Symbole

FDB

Exp1, Exp2,...

Rle :

Identique FCB mais cette fois, lexpression (valeur numrique et

symbole) reprsente une valeur sur 16 bits.

Le PC est incrment de 2 pour chaque mot crit.

Exemples :

DATA

DIX

FIN

ORG

FDB

FDB

FDB

FDB

FDB

FDB

EQU

$4000

$1997,$5432+$ABCD

'A,'B

'5,$5

10,$10

FIN

0

4

$4000

19

97

FF

FF

00

41

00

42

00

35

00

05

00

0A

00

10

00

04

00

00

FCC : Forme Constant Character string (dfinition dune constante chane de

caractres

Syntaxe :

Symbole

FCC

Master en Contrle et instrumentation

dlimiteur chane dlimiteur

Page 57

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Rle :

Inscrit en mmoire le code ASCII des caractres situs dans le champ

oprande entre les dlimiteurs. Et PC = PC+1 pour chaque caractre inscrit.

Remarque :

Les deux dlimiteurs doivent tre identiques et peuvent tre n'importe lequel

des caractres imprimables (on prend en gnral //).

L'expression

FCC /A/

est quivalent

FCB 'A

Illustration :

MESS

FCC

FCC

FCC

FCC

/FIN/

'LUNDI'

#MARDI#

252

$2000

46

49

4E

4C

55

4E

44

49

4D

41

52

44

49

35

END : fin d'assemblage

Syntaxe :

END

Rle :

Cette directive marque la limite du programme source.

Les lignes situes aprs cette directive sont ignores par l'assembleur.

PAGE : Saut de page

Syntaxe :

PAGE

Rle :

Fait avancer le papier de l'imprimante au dbut de la page suivante.

NAME : nom du programme

Syntaxe :

Master en Contrle et instrumentation

NAME PMAK

Page 58

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Rle :

Cette directive permet de donner un nom au programme qui apparait en

tte de page.

OPT : Option d'assemblage

Syntaxe :

OPT

ABS

Rle :

Cette directive fournit des complments d'informations lors de

l'assemblage. Les options sont crites dans le champ oprande et sont spares

par des virgules.

Diffrentes options :

ABS : ABSolu, le programme est crit avec un adressage absolu.

REL : RELogeable, le programme est crit avec un adressage relatif.

CRE : permet d'obtenir la table dite des rfrences croises.

L : demande l'impression du listing aprs opration d'assemblage termin.

Lopration dassemblage :

Elle seffectue gnralement en deux tapes (2 passes).

1re passe :

Consiste en une lecture de lensemble du programme source.

Au cours de cette phase, 3 analyses sont effectues :

Analyse lexicographique :

Compare le code opratoire une table interne (fichier comprenant les codes).

Analyse syntaxique :

Cette analyse dtecte :

Master en Contrle et instrumentation

les tiquettes manquantes

les codes opratoires errons

les oprandes manquants

Page 59

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Analyse smantique :

Cette analyse permet de dire si une ligne syntaxiquement correcte un sens.

Dtecte un symbole non dfini par ailleurs.

Lassembleur construit la table des symboles employs. Il regroupe tous les

symboles dfinis par le programmeur en leur donnant une valeur chacun deux

(Cration de la table des rfrences croiss).

Il gnre un code intermdiaire qui servira au second passage.

Les directives dassemblage sont galement interprtes.

2me passe :

Lassembleur gnre le code objet en tenant compte des adresses et des

donnes relles qui figurent dans la table des symboles.

3me passe :

Cette phase fournit le listing avec son code objet.

Master en Contrle et instrumentation

Page 60

Cours Microprocesseur 6809

Dr. Lachouri Abderrazek

Plan adopt pour l'criture d'un programme

OPT

ABS

Dfinition des variables

DEBUT

EQU

$4000

TIRQ

EQU