Académique Documents

Professionnel Documents

Culture Documents

TD Cna Can

Transféré par

YOUNESS KARAMITitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TD Cna Can

Transféré par

YOUNESS KARAMIDroits d'auteur :

Formats disponibles

TD-Chapitre 2 : CNA-CAN Cours : Électronique Analogique

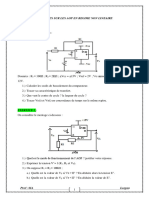

EXERCICE 1 :

On considère le montage du Convertisseur Numérique Analogique (CNA) suivant :

si ai = 0, l’interrupteur est relié à la masse

si ai = 1, l’interrupteur est relié à Uref.

1) Calculer les courants Ii en fonction des ai, Uref et R.

2) Appliquer le théorème de superposition pour exprimer le courant I en fonction des ai, Uref et R.

3) Donner l’expression de US en fonction de ai et Uref.

4) Pour Uref = -12 V, calculer le quantum Q de ce convertisseur.

Quel mot binaire faudra-t-il mettre en entrée pour avoir en sortie la tension la plus proche de 5 V.

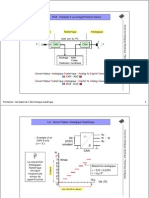

EXERCICE 2 On considère le convertisseur à comparaison directe de la figure ci-dessous :

Le signal analogique ue est comparé au signal uCNA(t) qui est l’image de N en en sortie du compteur.

L’étendue de mesure du signal d’entrée est définie par 0 ≤ ue < 10V

1) Quelle est la résolution q0 du CNA ? On donne : n = 8 bits.

2) Quelle est l’expression de uCNA pour un nombre N ?

En déduire la valeur Ne affichée en fin de comptage pour ue = 8 V.

3) Calculer le temps de conversion pour convertir la tension ue = 5 V. On donne : fH = 1 Mhz.

4) Quelle modification doit-on apporter au montage, pour obtenir une résolution q1 ≈ 1mV sans

changer le CNA ?

5) Afin de résoudre le problème précédant, uCNA est réduite avant d’être injectée sur le comparateur.

Calculer le coefficient A0 d’atténuation ainsi que la nouvelle tension maximale que pourra

convertir le CAN.

LST-GT FSTM Page 1

TD-Chapitre 2 : CNA-CAN Cours : Électronique Analogique

6) Calculer le nombre de bits nécessaires pour conserver une étendue de mesure de 10 V avec

q1≈1mV.

EXERCICE 3 Bloc de décodage pour un Convertisseur Analogique-Numérique parallèle (CAN Flash)

L’objectif de cet exercice est la synthèse du décodeur d’un convertisseur analogique-numérique

parallèle 3 bits. La structure complète du convertisseur est illustrée dans la figure suivante :

Décodage

Le convertisseur comprend une échelle de résistances définissant des niveaux de références (0.5V,

1V, 1.5V, 2V, 2.5V, 3V, 3.5V), des étages de comparaison pour chaque niveau de référence et un

décodeur. Le décodeur permet de passer des résultats de comparaison au mot de n = 3 bits

(S2S1S0) représentant la valeur d’entrée.

1) Quel est le pas de quantification Q ?

2) Compléter sa fonction de transfert dans le tableau suivant ;

Ve S2 S1 S0 N(10)

3) Compléter la table de vérité correspondant au bloc logique décodeur ;

Entrées Sorties

G F E D C B A S2 S1 S0

4) A partir de la table de vérité, établir les équations logiques du décodeur.

5) Quel est l’avantage et l’inconvénient de ce convertisseur ?

LST-GT FSTM Page 2

Vous aimerez peut-être aussi

- Cna Et Can - CoursDocument9 pagesCna Et Can - Courslohoma0% (1)

- TD 7: Convertisseur CAN Et CNADocument1 pageTD 7: Convertisseur CAN Et CNAMouad BRKPas encore d'évaluation

- Chapitre 6 Les Convirtisseurs CAN Et CNADocument12 pagesChapitre 6 Les Convirtisseurs CAN Et CNAAymane Fahmi100% (1)

- Exercices CAN CNADocument2 pagesExercices CAN CNAyoussefPas encore d'évaluation

- TD Convetisseurs NA AnDocument11 pagesTD Convetisseurs NA Anminzo9479100% (2)

- Can & CnaDocument19 pagesCan & CnaRiham abPas encore d'évaluation

- Forces Et Champs 4Document5 pagesForces Et Champs 4Emie JumboPas encore d'évaluation

- Can & CnaDocument2 pagesCan & CnaAYOUB RIADPas encore d'évaluation

- TP Can CnaDocument8 pagesTP Can CnaEdward Adounvo100% (1)

- TD N°1Document1 pageTD N°1Rebhi AchrefPas encore d'évaluation

- Cna & CanDocument15 pagesCna & CanAk ramPas encore d'évaluation

- TD HacheurDocument2 pagesTD HacheurSoufian JaafarPas encore d'évaluation

- Corrigé-Dexaman - Capteurs Et Instrumentation ELMDocument2 pagesCorrigé-Dexaman - Capteurs Et Instrumentation ELMnuit_claire002Pas encore d'évaluation

- Aop Ex1Document9 pagesAop Ex1onzpr0325Pas encore d'évaluation

- EC3 RLC Serie PDFDocument10 pagesEC3 RLC Serie PDFOussama ZnPas encore d'évaluation

- Exerxices Sur Les Aop en Regime Non Lineaire Elo2Document4 pagesExerxices Sur Les Aop en Regime Non Lineaire Elo2seniorblaisotPas encore d'évaluation

- Serie de TD 4 Hacheurs Serie Alimentant Un MCC1Document1 pageSerie de TD 4 Hacheurs Serie Alimentant Un MCC1حسام الدينPas encore d'évaluation

- Ampli Op en Régime N.L - Problème 2Document1 pageAmpli Op en Régime N.L - Problème 2Mbaira LeilaPas encore d'évaluation

- TP2 MCC PrepaDocument6 pagesTP2 MCC PrepaAlfredho ShactarPas encore d'évaluation

- FiltreDocument19 pagesFiltrelamilouch6498Pas encore d'évaluation

- TD CAN À Approximation - CorrectionDocument9 pagesTD CAN À Approximation - CorrectionRachid Hamiani100% (1)

- EC3 RLC SerieDocument10 pagesEC3 RLC SeriejihenePas encore d'évaluation

- Exo2 - CAN CNADocument8 pagesExo2 - CAN CNAYounes Raache67% (3)

- TD CAN A Rampe CorrectionDocument9 pagesTD CAN A Rampe CorrectionGxfhjjPas encore d'évaluation

- Chapitre 1 Transistor JFET Ver1 11.05.23Document28 pagesChapitre 1 Transistor JFET Ver1 11.05.23AZIL AMINPas encore d'évaluation

- CHAPITRE II Circuits Séquentiels PDFDocument35 pagesCHAPITRE II Circuits Séquentiels PDFTimble PuteurPas encore d'évaluation

- TD RedresseurDocument2 pagesTD RedresseurMohamed Oulad100% (1)

- Td2 Trans StatiqueDocument5 pagesTd2 Trans Statiquesara100% (1)

- TD1 HacheursDocument3 pagesTD1 HacheursMoez YoussefPas encore d'évaluation

- Devoir TSI GE HacheursDocument4 pagesDevoir TSI GE HacheursSaid Oujja100% (1)

- ForwardDocument9 pagesForwardmagnetik_66Pas encore d'évaluation

- Concours LP 2017-2018Document8 pagesConcours LP 2017-2018soufianePas encore d'évaluation

- Chap6 - Les Registres Et CompteursDocument12 pagesChap6 - Les Registres Et CompteursMOHAMED AIT HADDOUCHPas encore d'évaluation

- Instrumentation Et Mesure-Lic PGDocument59 pagesInstrumentation Et Mesure-Lic PGBilbon SacketPas encore d'évaluation

- Serie CapteursDocument1 pageSerie CapteursMohamed Habib100% (2)

- 2-CAN DiaDocument22 pages2-CAN DiaHoussineElGhazouaniPas encore d'évaluation

- TP1 Len62 PDFDocument5 pagesTP1 Len62 PDFbengheniaPas encore d'évaluation

- TD CAN Serie Parallele - CorrectionDocument5 pagesTD CAN Serie Parallele - CorrectionRachid Hamiani67% (3)

- Le RedressementDocument22 pagesLe Redressementanes bendjemaiPas encore d'évaluation

- DS N 1 Atc 2steDocument5 pagesDS N 1 Atc 2steAyoub Shait100% (1)

- Exercice Oscillateur À RelaxationDocument1 pageExercice Oscillateur À Relaxationminzo9479100% (2)

- Can Cna td1Document2 pagesCan Cna td1Hyacinthe KossiPas encore d'évaluation

- Ci13 TD 3 Can eDocument3 pagesCi13 TD 3 Can eCapteurs InstrumentationPas encore d'évaluation

- Travaux Dirigés - AOP - NL - ET2Document6 pagesTravaux Dirigés - AOP - NL - ET2Paulin TCHUEGUEMPas encore d'évaluation

- TD RedressementDocument3 pagesTD RedressementCatherine Comme La VillePas encore d'évaluation

- 5-Facteur de Qualite Et Ciecuit ResonnantDocument9 pages5-Facteur de Qualite Et Ciecuit ResonnantAFAFPas encore d'évaluation

- Filtre Actif 1Document2 pagesFiltre Actif 1Juba HamichePas encore d'évaluation

- TD 3 230917 220150Document2 pagesTD 3 230917 220150salah fcbPas encore d'évaluation

- Série 3+corrigéDocument4 pagesSérie 3+corrigéAli AyadPas encore d'évaluation

- Transistor BipolaireDocument5 pagesTransistor BipolaireZH HamzaPas encore d'évaluation

- CnacanDocument11 pagesCnacanben boubakerPas encore d'évaluation

- TP/TD - Conditionnement D'un Capteur de TempératureDocument3 pagesTP/TD - Conditionnement D'un Capteur de TempératureoussamaPas encore d'évaluation

- Corriges 22 10 2013Document15 pagesCorriges 22 10 2013Ndeye Rokhaya NDOYEPas encore d'évaluation

- TD2 - Chaîne DacquisitionDocument3 pagesTD2 - Chaîne DacquisitionMootez ZouariPas encore d'évaluation

- Conversion PDFDocument25 pagesConversion PDFLam NovoxPas encore d'évaluation

- td1 Cna CanDocument2 pagestd1 Cna CanBinte Ahmed Gaye100% (1)

- Mem o 2Document3 pagesMem o 2loashPas encore d'évaluation

- Cna Et Can - CoursDocument9 pagesCna Et Can - CoursLam NovoxPas encore d'évaluation

- Matière Electronique Systèmes PDFDocument71 pagesMatière Electronique Systèmes PDFYassine BelhmerPas encore d'évaluation

- Volatilité de Taux de Change Et Son Impact Sur Les Investissements ÉtrangersDocument21 pagesVolatilité de Taux de Change Et Son Impact Sur Les Investissements ÉtrangersIssam KatouiPas encore d'évaluation

- Support de Formation EcologiqueDocument25 pagesSupport de Formation EcologiqueOstine Erold100% (1)

- 10 Intrebari ComuneDocument4 pages10 Intrebari ComuneGeorge Holostencu100% (1)

- Chapitre II BM GHODBANEDocument19 pagesChapitre II BM GHODBANESennaoui LaraPas encore d'évaluation

- SolidworksDocument127 pagesSolidworksBram's U Yafelman100% (2)

- Techniques D'irrigation - GME&EM (1èrep-2015Document164 pagesTechniques D'irrigation - GME&EM (1èrep-2015El Amine Bniaiche100% (6)

- PPP Et HDLCDocument15 pagesPPP Et HDLCimanePas encore d'évaluation

- Annexe 5 - Révisé - Modèle de Rapport NarratifDocument6 pagesAnnexe 5 - Révisé - Modèle de Rapport NarratifabdelkrimkhouloudPas encore d'évaluation

- P2 Encadré - Normes Pers OMSDocument2 pagesP2 Encadré - Normes Pers OMSAlberto GeorgePas encore d'évaluation

- 1492 In098 - Mu e PDFDocument6 pages1492 In098 - Mu e PDFjesusortegavPas encore d'évaluation

- Loi N 003 2006 Du 25 Avril 2006 Relative A La Declaration Des Biens Et AvoirsDocument6 pagesLoi N 003 2006 Du 25 Avril 2006 Relative A La Declaration Des Biens Et AvoirsCFP PROFISCAL SARLPas encore d'évaluation

- Rapport de StageDocument15 pagesRapport de StageYounes Nassir100% (1)

- Correction Du Sujet de Finance D'entreprise MMADocument3 pagesCorrection Du Sujet de Finance D'entreprise MMAKevin NguemaPas encore d'évaluation

- Cinétique Chimique Pour L3 Genie Des Procédés - Genie ChimiqueDocument452 pagesCinétique Chimique Pour L3 Genie Des Procédés - Genie ChimiqueMOUSSADEK Yahia Abdel Illah100% (1)

- XP Cen Iso-Ts 17892-10Document19 pagesXP Cen Iso-Ts 17892-10Kouassi JaurèsPas encore d'évaluation

- Calcul Préstations RéciproquesDocument2 pagesCalcul Préstations RéciproquesSwelLuvsYou100% (2)

- M1 - Gestion Des Processus Et de La Qualité - TDDocument15 pagesM1 - Gestion Des Processus Et de La Qualité - TDdtlnl889Pas encore d'évaluation

- CSC Computer Sciences International S.À R.L. 2015Document18 pagesCSC Computer Sciences International S.À R.L. 2015LuxembourgAtaGlancePas encore d'évaluation

- ProsecaDocument5 pagesProsecafidelASPas encore d'évaluation

- S7.5 Compactage CoursDocument14 pagesS7.5 Compactage CoursNakoulma FaridatouPas encore d'évaluation

- NT 007Document14 pagesNT 007Sofiane AoudiaPas encore d'évaluation

- Chapitre 2 - Notion de BilanDocument29 pagesChapitre 2 - Notion de BilanMaàma Traoré100% (1)

- SDG 28538 Broch Certif WEB 2023 2024Document12 pagesSDG 28538 Broch Certif WEB 2023 2024Coulibaly Youssouf n'goloPas encore d'évaluation

- Ouvrage Performance 0702Document194 pagesOuvrage Performance 0702sosi2020Pas encore d'évaluation

- Tutoriel Pstage Pour Les EtudiantsDocument16 pagesTutoriel Pstage Pour Les EtudiantsmessiliadjoPas encore d'évaluation

- Feuille de Route Vers L Industrie Electronique Du FuturDocument140 pagesFeuille de Route Vers L Industrie Electronique Du FuturJourdan MbappePas encore d'évaluation

- TP - 4 Mach - HydrDocument3 pagesTP - 4 Mach - HydrIsmail EzzaraaPas encore d'évaluation

- Les Secrets de Lautomatisation YoutubeDocument35 pagesLes Secrets de Lautomatisation Youtubekbcyf8nj6dPas encore d'évaluation

- BiomassDocument15 pagesBiomassAleaPas encore d'évaluation

- Cours de MacroéconomieDocument35 pagesCours de MacroéconomieCaroline Baillez100% (1)

- Hacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandHacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Hacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersD'EverandHacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersPas encore d'évaluation

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Manuel de fabrication du savon: Je fabrique mes savons facilementD'EverandManuel de fabrication du savon: Je fabrique mes savons facilementÉvaluation : 5 sur 5 étoiles5/5 (4)

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- Création d'une start-up à succès de A à Z: Réussir votre Start-up 2.0 Web et MobileD'EverandCréation d'une start-up à succès de A à Z: Réussir votre Start-up 2.0 Web et MobileÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- La communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseD'EverandLa communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseÉvaluation : 5 sur 5 étoiles5/5 (1)

- Explication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumD'EverandExplication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumPas encore d'évaluation

- Piraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéD'EverandPiraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéPas encore d'évaluation

- NFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueD'EverandNFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueÉvaluation : 5 sur 5 étoiles5/5 (5)

- Marketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxD'EverandMarketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxPas encore d'évaluation

- Kali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.D'EverandKali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.Évaluation : 5 sur 5 étoiles5/5 (1)

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- Blockchain: Applications et compréhension du monde réel: Comment appliquer la Blockchain dans votre mondeD'EverandBlockchain: Applications et compréhension du monde réel: Comment appliquer la Blockchain dans votre mondePas encore d'évaluation

- Créer Son Propre Site Internet Et Son Blog GratuitementD'EverandCréer Son Propre Site Internet Et Son Blog GratuitementÉvaluation : 5 sur 5 étoiles5/5 (1)

- Le guide du hacker : le guide simplifié du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandLe guide du hacker : le guide simplifié du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 5 sur 5 étoiles5/5 (2)

- 101 idées pour travailler à domicile: Plus tous les conseils pour bien démarrerD'Everand101 idées pour travailler à domicile: Plus tous les conseils pour bien démarrerÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Apprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationD'EverandApprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationPas encore d'évaluation

- Dark Python : Apprenez à créer vos outils de hacking.D'EverandDark Python : Apprenez à créer vos outils de hacking.Évaluation : 3 sur 5 étoiles3/5 (1)