Académique Documents

Professionnel Documents

Culture Documents

DS2 2022 2023

Transféré par

tadlaouianouar44Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

DS2 2022 2023

Transféré par

tadlaouianouar44Droits d'auteur :

Formats disponibles

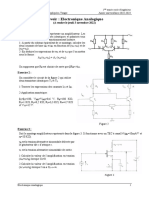

Electronique analogique LST_IEEA 2022/2023

Contrôle n°2 d’électronique analogique

Le 19 novembre 2022 : Durée 2h00

Exercice 1 : on se propose d’étudier l’amplificateur à transistors bipolaires de la

figure 1 ci-dessous. Les transistors ont un gain en courant β1=β2=β=180. On

suppose IC=βIB et IC=IE. Ce et Cs sont des condensateurs de liaison et CE un

condensateur de découplage. RC=10kΩ ; R3=1.2kΩ ; RE=2.2kΩ;

R2=75kΩ; Ru=22kΩ et VCC=20V.

VCC

RC C2

R1 B2

C1 T2

Ce

T1 E2 Cs

B1 E1 vs(t)

ve(t) R2 R3 CE Ru

RE

Figure 1

1. Etude statique : On impose VBE1=VBE2=0.7V et VCE1=VCE2=VCC/2.

1.1. Donner le schéma du montage pour l’étude statique.

1.2. Calculer le potentiel VE2 de l’émetteur du transistor T2 par rapport à la masse.

Calculer le courant IC2. En déduire le courant IB2.

1.3. Calculer le potentiel VB2 du point B2 par rapport à la masse. En déduire le

courant IRC dans la résistance RC.

1.4. Exprimer le courant IRC en fonction de IC1 et IB2. Calculer IC1. En déduire IB1.

1.5. Calculer le potentiel VE1 du point E1 par rapport à la masse. Calculer en suite

le potentiel VB1 du point B1 par rapport à la masse.

1.6. Calculer le courant I2 dans la résistance R2. En déduire le courant I1 dans R1.

1.7. Calculer alors la valeur de R1.

1.8. Calculer r1=h11 pour le transistor T1 et r2=h11 pour le transistor T2.

2. Etude dynamique moyennes fréquences : Les transistors sont modélisés

par le schéma équivalent utilisant β et r = h11. On posera R0=RE//Ru,

RB=R1//R2 et RL=RC//Re2.

Pour ces fréquences on suppose que les réactances des condensateurs Ce, Cs

et CE sont nulles.

2.1. Donner le schéma équivalent en dynamique du montage complet.

2.2. Donner le schéma équivalent en dynamique du 2ème étage en pointillé sur la

figure 1.

2.3. Calculer le gain en tension A2 de cet étage et sa résistance d’entrée Re2.

2.4. En remplaçant le l’étage 2 par Re2, donner le schéma équivalent en dynamique

du 1er étage.

2.5. Calculer le gain en tension A1 du 1er étage et sa résistance d’entrée Re.

2.6. Le gain du montage complet étant A = A1.A2. Montrer que :

R0 RC

A = −β 2 .

r1 (r2 + RC + βR0 )

2.7. En déduire le gain de l’amplificateur à vide A0.

Université Cadi Ayyad Faculté des Sciences et Techniques Guéliz 1

Electronique analogique LST_IEEA 2022/2023

2.8. A partir du schéma équivalent donné dans 2.1, tracer le schéma pour calculer la

résistance de sortie Rs (ve=0).

2.9. Calculer Rs.

3. Etude dynamique basses fréquences : On modélise le montage complet par

ses paramètres A0 (gain à vide) et Re (résistance d’entrée). On supposera que

Rs=0 et que seuls le condensateur Cs intervient alors que Ce et CE sont

considérés comme des courts-circuits.

3.1. Donner le schéma du montage pour cette étude.

3.2. Calculer le gain en tension Ab et le mettre sous la forme :

ω

j

ωs

Ab = A0 Donner l’expression de ωs.

ω

1+ j

ωs

3.3. Calculer la fréquence de coupure basse fcb.

3.4. Tracer le diagramme de Bode relatif au gain Ab.

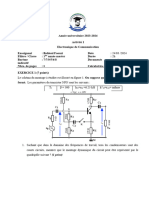

4. Etude dynamique hautes fréquences. On suppose que seul l’effet du

transistor T1 intervient en hautes fréquences (HF). Le schéma équivalent en

HF pour T1 est donné sur la figure 2 avec Cbc=13.6pF. T2 étant toujours

modélisé par le schéma équivalent utilisant β et r2. On remplace donc le 2ème

étage par Re2.

4.1. En remplaçant le l’étage 2 par Re2, donner le schéma équivalent en dynamique

en HF du 1er étage.

4.2. Appliquer le théorème de Miller pour remplacer Cbc par deux

condensateurs Cje en parallèle sur l’entrée et Cjs en parallèle sur la sortie.

Donner les expressions de Cje et Cjs.

4.3. Exprimer le gain en tension du premier étage Ah et le mettre sous la forme :

1

Ah = Ac . Donner les expressions de Ac et ωh.

ω

1+ j

ωh

4.4. Calculer la valeur de la fréquence de coupure haute fch.

4.5. Tracer le diagramme de Bode relatif au gain Ah.

Cbc

B C

Vbe r gmVbe

Cbe

Figure 2

Université Cadi Ayyad Faculté des Sciences et Techniques Guéliz 2

Vous aimerez peut-être aussi

- 05 TD 5Document1 page05 TD 5Maryam YammPas encore d'évaluation

- Exercices d'optique et d'électromagnétismeD'EverandExercices d'optique et d'électromagnétismeÉvaluation : 5 sur 5 étoiles5/5 (1)

- Série 3ensaDocument3 pagesSérie 3ensa3freefire 3gamePas encore d'évaluation

- Transistor Etude Dynamique Exercices ResolusDocument8 pagesTransistor Etude Dynamique Exercices ResolusHerman Darrel LITOUKI YOUBI0% (1)

- Annales de Mathématiques, Baccalauréat C et E, Cameroun, 2008 - 2018: Sujets et CorrigésD'EverandAnnales de Mathématiques, Baccalauréat C et E, Cameroun, 2008 - 2018: Sujets et CorrigésÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- 2tr 4res 1capDocument6 pages2tr 4res 1capMounaim MatiniPas encore d'évaluation

- 2 Etage741a PDFDocument4 pages2 Etage741a PDFYoussef RagraguiPas encore d'évaluation

- 1 Examen 2006 ElectroniqueDocument2 pages1 Examen 2006 ElectroniqueCharaf Leo100% (1)

- Rattrapage EA S5 2017-2018-1Document2 pagesRattrapage EA S5 2017-2018-1Mohamed NaciriPas encore d'évaluation

- H H Et H K H: 2-Etude DynamiqueDocument1 pageH H Et H K H: 2-Etude Dynamiqueinky miss pawsPas encore d'évaluation

- TD 1 Electronique AnalogiqueDocument4 pagesTD 1 Electronique AnalogiqueMarouan ZahriPas encore d'évaluation

- Controle 2015 - 2016Document4 pagesControle 2015 - 2016Mohamed Ben talebPas encore d'évaluation

- Controle Electronique SMPS5 2019 Avec BarémeDocument2 pagesControle Electronique SMPS5 2019 Avec BarémeMohamed Ben talebPas encore d'évaluation

- TD2 TransistorDocument3 pagesTD2 TransistorIntissar Annebi100% (1)

- Tp2bis PDFDocument2 pagesTp2bis PDFNihale QasmiPas encore d'évaluation

- TD2 Tor Bipolaire 21-22Document2 pagesTD2 Tor Bipolaire 21-22Baamrane MouadPas encore d'évaluation

- TD 4Document4 pagesTD 4Sky MarPas encore d'évaluation

- TD01 2023-24 AmpliDiffDocument2 pagesTD01 2023-24 AmpliDiffYousra AboussaidPas encore d'évaluation

- TD6-MIP-Corr-2016-17 - EnseignantDocument8 pagesTD6-MIP-Corr-2016-17 - EnseignantBattata JamaPas encore d'évaluation

- TD Pf3acDocument7 pagesTD Pf3acsenamdvs60Pas encore d'évaluation

- Ampli A Transistor Par SPICEDocument8 pagesAmpli A Transistor Par SPICEta geule100% (1)

- 04 TD 4Document1 page04 TD 4Maryam YammPas encore d'évaluation

- Fiche TDDocument6 pagesFiche TDRebecca NgaryinanPas encore d'évaluation

- Capture D'écran . 2024-01-29 À 21.06.42Document69 pagesCapture D'écran . 2024-01-29 À 21.06.42achraf.elmahjourPas encore d'évaluation

- TD Ampli À Transistor BipolaireDocument28 pagesTD Ampli À Transistor BipolaireYahya YahyaPas encore d'évaluation

- TD - Electronique - TIT-1.pdf Version 1 PDFDocument10 pagesTD - Electronique - TIT-1.pdf Version 1 PDFsiwar ben salemPas encore d'évaluation

- TP1 OscillateursDocument12 pagesTP1 OscillateursRaghadPas encore d'évaluation

- Mirroir de CourantDocument7 pagesMirroir de CourantdodomarocPas encore d'évaluation

- TD Ea PDFDocument19 pagesTD Ea PDFالغزيزال الحسن EL GHZIZAL HassanePas encore d'évaluation

- CF 2020-2021-Corrigé ElectDocument6 pagesCF 2020-2021-Corrigé ElectAli brahim MahamatPas encore d'évaluation

- Compléments D'exercices Corrigés D'electronique de Communication - INDP1 - 2014-2015Document23 pagesCompléments D'exercices Corrigés D'electronique de Communication - INDP1 - 2014-2015Titah Ibrahim100% (1)

- TD Ampli À Transistor BipolaireDocument28 pagesTD Ampli À Transistor Bipolairezale100% (2)

- TD4 Transistors BipolairesDocument3 pagesTD4 Transistors Bipolaireshamza khattabi100% (1)

- Transistor (Bi Et TEC) (Statiqueet Dynamique) + Amplificateur (Puissance Et Différentiel)Document15 pagesTransistor (Bi Et TEC) (Statiqueet Dynamique) + Amplificateur (Puissance Et Différentiel)Sabrina BenghenamePas encore d'évaluation

- Merged 20200616 020431Document3 pagesMerged 20200616 020431Sawat SiwarPas encore d'évaluation

- Série 2 TransistorDocument6 pagesSérie 2 TransistorYoussra DjePas encore d'évaluation

- Travaux Pratique 3 2324-1Document14 pagesTravaux Pratique 3 2324-1orsiny clinton TCHAPTCHETPas encore d'évaluation

- Poly TP 2020 2021Document13 pagesPoly TP 2020 2021معاذ طويرPas encore d'évaluation

- TD AmplificateursdepuissanceDocument3 pagesTD Amplificateursdepuissancemutrace100% (1)

- TD Amplificateursdepuissance PDFDocument3 pagesTD Amplificateursdepuissance PDFmutracePas encore d'évaluation

- SERIE12345 Semestre 2Document15 pagesSERIE12345 Semestre 2Sabrina BenghenamePas encore d'évaluation

- DevoirDocument2 pagesDevoirSimohammed Dahman100% (1)

- TD 1 Gim2 S2-2020-2021Document3 pagesTD 1 Gim2 S2-2020-2021Ťå Ř ÏqPas encore d'évaluation

- Ass EC CCDocument3 pagesAss EC CCOtman NassiriPas encore d'évaluation

- Exercices Amplificateur Emetteur Commun Avec 2Document7 pagesExercices Amplificateur Emetteur Commun Avec 2TaoufikElKanouni100% (3)

- TD 3 CPS2Document3 pagesTD 3 CPS2lmons saroutPas encore d'évaluation

- TD4 MultivibrateursDocument1 pageTD4 MultivibrateursDoha BenhibaPas encore d'évaluation

- Exerc 9Document3 pagesExerc 9Karim TahiryPas encore d'évaluation

- Devoir Electronique AnalogiqueDocument1 pageDevoir Electronique AnalogiqueImane ayiPas encore d'évaluation

- TP2 Montages FondamentauxDocument2 pagesTP2 Montages FondamentauxHorea BâlcPas encore d'évaluation

- Activit 2Document5 pagesActivit 2mwinkeudelrioPas encore d'évaluation

- Exam 2017 AnalogieDocument2 pagesExam 2017 AnalogieMohamed BelbarakaPas encore d'évaluation

- Travaux Diriges Fondamentaux de L'Electronique Analogique: EXERCICE N°1: Le Transistor À Effet de ChampDocument5 pagesTravaux Diriges Fondamentaux de L'Electronique Analogique: EXERCICE N°1: Le Transistor À Effet de ChampAlex FezeuPas encore d'évaluation

- TD3-MIP-Corr-2016-17 - EnseignantDocument6 pagesTD3-MIP-Corr-2016-17 - EnseignantBattata JamaPas encore d'évaluation

- Travaux Dirigés DElectronique Analogique 5Document4 pagesTravaux Dirigés DElectronique Analogique 5omar benani100% (1)

- Container MaritimeDocument11 pagesContainer Maritimeabdou8616Pas encore d'évaluation

- Management Stratégique Notes PersoDocument10 pagesManagement Stratégique Notes PersoKi ChanPas encore d'évaluation

- L'Évolution Du Paiement Électronique en Algérie Pendant La Pandémie Du COVID-19Document16 pagesL'Évolution Du Paiement Électronique en Algérie Pendant La Pandémie Du COVID-19faroudja ait hamouPas encore d'évaluation

- OrgueDocument1 pageOrgueLalotte RedPas encore d'évaluation

- Créer Un Site FTP Avec Isolation Des UtilisateursDocument9 pagesCréer Un Site FTP Avec Isolation Des UtilisateursBayina felixPas encore d'évaluation

- Réseaux Sans FilsDocument16 pagesRéseaux Sans FilsGhalia djerroudPas encore d'évaluation

- TP 2: Le Compteur NumériqueDocument8 pagesTP 2: Le Compteur NumériqueBenoit rousseauPas encore d'évaluation

- Gestion de MagasinDocument3 pagesGestion de MagasinImed Mahdhaoui100% (2)

- TP3 - Atelier Info IndustrielleDocument2 pagesTP3 - Atelier Info IndustrielleNadia Mars HenchirPas encore d'évaluation

- CP FittingsDocument151 pagesCP FittingsFouquetPas encore d'évaluation

- Chapitre 3 Organisation Du Service Maintenance PDFDocument5 pagesChapitre 3 Organisation Du Service Maintenance PDFbenadda makhloufPas encore d'évaluation

- Reseaux QCM CorrDocument2 pagesReseaux QCM Corrsonia100% (2)

- cv08 12Document1 pagecv08 12HMILAPas encore d'évaluation

- HistsysDocument307 pagesHistsysGabriel PatrascuPas encore d'évaluation

- TD Tournage Des Pieces MecaniquesDocument6 pagesTD Tournage Des Pieces MecaniquesAmin's LifestylePas encore d'évaluation

- C02 Diagramme CUDocument19 pagesC02 Diagramme CUdazai azouzePas encore d'évaluation

- Ge CssaDocument1 pageGe CssaImen MgaidiaPas encore d'évaluation

- CV Amajoud Soufian PDFDocument1 pageCV Amajoud Soufian PDFSalmaPas encore d'évaluation

- DocumentationDocument18 pagesDocumentationStacey Ware100% (2)

- API StifDocument40 pagesAPI StifGuillaume CarretPas encore d'évaluation

- Sujet Po Delf B2Document7 pagesSujet Po Delf B2myriamPas encore d'évaluation

- UtilisationMultimetre Le MultimetreDocument2 pagesUtilisationMultimetre Le Multimetreroyce974Pas encore d'évaluation

- XBT MagelisDocument6 pagesXBT Magelisvvalentin2Pas encore d'évaluation

- DEMBOYDocument10 pagesDEMBOYgiovanni ramarosonPas encore d'évaluation

- Brochure Energie IndustrieDocument58 pagesBrochure Energie IndustriepopaminoPas encore d'évaluation

- Cours - Régulation Automatique AnalogiqueDocument276 pagesCours - Régulation Automatique Analogiqueautsi100% (1)

- MR 23Document52 pagesMR 23Mohammed Reda AitbellaPas encore d'évaluation

- Aprilia Mana 850 GT ABS (2009) MotorcycleDocument199 pagesAprilia Mana 850 GT ABS (2009) MotorcycleLeopoldoPas encore d'évaluation

- Sbin S.A Avis de Recrutement Global OfficielDocument57 pagesSbin S.A Avis de Recrutement Global OfficielCredo DukemPas encore d'évaluation

- Telecom-Reseaux Telecom (Programme - S1&S2) VFDocument51 pagesTelecom-Reseaux Telecom (Programme - S1&S2) VFdjimy_dzPas encore d'évaluation

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- Secrets ancestraux d'un maître guérisseur: Un sceptique occidental, un maître oriental et les plus grands secrets de la vieD'EverandSecrets ancestraux d'un maître guérisseur: Un sceptique occidental, un maître oriental et les plus grands secrets de la vieÉvaluation : 5 sur 5 étoiles5/5 (2)

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- Améliorer votre mémoire: Un Guide pour l'augmentation de la puissance du cerveau, utilisant des techniques et méthodesD'EverandAméliorer votre mémoire: Un Guide pour l'augmentation de la puissance du cerveau, utilisant des techniques et méthodesÉvaluation : 5 sur 5 étoiles5/5 (2)

- 20 Véritables remèdes de nos grands-mères pour maigrir vite et enfin perdre du poidsD'Everand20 Véritables remèdes de nos grands-mères pour maigrir vite et enfin perdre du poidsÉvaluation : 5 sur 5 étoiles5/5 (1)

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation

- Dark Python : Apprenez à créer vos outils de hacking.D'EverandDark Python : Apprenez à créer vos outils de hacking.Évaluation : 3 sur 5 étoiles3/5 (1)

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- L'Art de la guerre: Traité de stratégie en 13 chapitres (texte intégral)D'EverandL'Art de la guerre: Traité de stratégie en 13 chapitres (texte intégral)Évaluation : 4 sur 5 étoiles4/5 (3032)

- La vie des abeilles: Prix Nobel de littératureD'EverandLa vie des abeilles: Prix Nobel de littératureÉvaluation : 4 sur 5 étoiles4/5 (41)

- Explication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumD'EverandExplication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumPas encore d'évaluation

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- Hacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandHacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- L'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.D'EverandL'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.Évaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Piraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéD'EverandPiraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéPas encore d'évaluation

- Électrotechnique | Pas à Pas: Bases, composants & circuits expliqués pour les débutantsD'EverandÉlectrotechnique | Pas à Pas: Bases, composants & circuits expliqués pour les débutantsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Transformez votre vie: Utilisez le pouvoir créateur qui est en vous pour construire votre vie à l'image de ce que vous voulez qu'elle soitD'EverandTransformez votre vie: Utilisez le pouvoir créateur qui est en vous pour construire votre vie à l'image de ce que vous voulez qu'elle soitÉvaluation : 4 sur 5 étoiles4/5 (14)

- Kali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.D'EverandKali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.Évaluation : 5 sur 5 étoiles5/5 (1)

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- NFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueD'EverandNFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueÉvaluation : 5 sur 5 étoiles5/5 (5)

- Semer avec succès pour rassembler avec abundance. Jardin organique et synergique: Calcul des meilleurs jours pour l'ensemencement de chaque légumeD'EverandSemer avec succès pour rassembler avec abundance. Jardin organique et synergique: Calcul des meilleurs jours pour l'ensemencement de chaque légumePas encore d'évaluation

- La communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseD'EverandLa communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseÉvaluation : 5 sur 5 étoiles5/5 (1)

- Marketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxD'EverandMarketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxPas encore d'évaluation