Académique Documents

Professionnel Documents

Culture Documents

Upload-Série D'exercices N°2-4tech-Compteur-2014-2015 PDF

Transféré par

Rached DouahchuaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Upload-Série D'exercices N°2-4tech-Compteur-2014-2015 PDF

Transféré par

Rached DouahchuaDroits d'auteur :

Formats disponibles

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 1 /14

FICHES TECHNIQUES DE QUELQUES CIRCUITS INTEGRES

Compteur binaire asynchrone 4 bits 7493 - 74293

7493 74293

R0(1) 2 CTR R0(1) 12 CTR

R0(2) 3 CT=0 R0(2) 13 CT=0

14 DIV 2 12 QA 10 DIV 2 9 QA

CKA + CKA +

DIV 8 0 9 QB DIV 8 0 5 QB

1 8 11 4

CKB + CT QC CKB + CT QC

11 8

2 QD 2 QD

Botier DIL 14 Botier DIL 14

VCC 5 GND 10 VCC 14 GND 7

Le fonctionnement de ces deux compteurs est identique seul le brochage est diffrent

Le Schma interne du compteur 7493 est comme suit

QA QB QC QD

12 9 8 11

J J J J

Q Q Q Q

14 CKA Clock Clock Clock Clock

K K K K

Clear Clear Clear Clear

2 R0(1)

3 R0(2)

CKB

1

N.B Les entres J et K sont ltat logique 1 une fois que le circuit est aliment

Compteur binaire asynchrone 4 bits 7492

R0(1) 6 CTR

R0(2) 7 CT=0

14 DIV 2 12 QA

CKA +

DIV 3 11 QB

0

1

CKB + CT

9

1Z4 QC

DIV 2 8

4 + QD

Le Schma interne du compteur 7492 est comme suit

QA QB QC QD

12 11 9 8

J J J J

Q Q Q Q

14 CKA Clock Clock Clock Clock

K K K Q K

Clear Clear Clear Clear

6 R0(1)

7 R0(2)

CKB

1

N.B Les entres J et K sont ltat logique 1 une fois que le circuit est aliment

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 2 /14

Compteur asynchrone 4 bits 7490 - 74290

Le fonctionnement de ces deux compteurs est identique seul le brochage est diffrent

R0(1) 2 CTR R0(1) 12 CTR

R0(2) 3 CT=0 R0(2) 13 CT=0

6 1

R9(1) R9(1)

R9(2) 7 Z3 R9(2) 3 Z3

14 DIV 2 10 DIV 2 9

CKA 12 QA CKA QA

3CT=1 3CT=1

DIV 5 9 QB DIV 5 5 QB

0 0

1 11

CKB CKB

CT 8 CT 4

QC QC

3CT=4 3CT=4

11 8

2 QD 2 QD

Botier DIL 16 Botier DIL 16

VCC 5 GND 10 VCC 16 GND 8

Le Schma interne du compteur 7490 est comme suit

QA QB QC QD

12 9 8 11

J Preset J J S Preset

Q Q Q Q

14 CKA Clock Clock Clock Clock

K K K R Q

Clear Clear Clear Clear

6 R9(1)

7 R9(2)

2 R0(1)

3 R0(2)

7 CKB

N.B Les entres J et K sont ltat logique 1 une fois que le circuit est aliment

Tables de fonctionnement communes aux deux

compteurs 7490 - 74290

Table de fonctionnement des

Pour Comptage BCD,relier Pour Comptage biquinaire (5-2) Resets

la sortie QA lentre CKB relier la sortie QD lentre CKA

Compte

Sortie Compte

Sortie Entres Reset Sorties

QD QC QB QA QA QD QC QB R0(1) R0(2) R9(1) R9(2) QD QC QB QA

0 0 0 0 0 0 0 0 0 0 1 1 0 X 0 0 0 0

1 0 0 0 1 1 0 0 0 1 1 1 X 0 0 0 0 0

2 0 0 1 0 2 0 0 1 0 X X 1 1 1 0 0 1

3 0 0 1 1 3 0 0 1 1 X 0 X 0 Compte

4 0 1 0 0 4 0 1 0 0 0 X 0 X Compte

5 0 1 0 1 5 1 0 0 0 0 X X 0 Compte

6 0 1 1 0 6 1 0 0 1 X 0 0 X Compte

7 0 1 1 1 7 1 0 1 0

8 1 0 0 0 8 1 0 1 1 N.B X : Quelque soit le niveau logique 0 ou 1

9 1 0 0 1 9 1 1 0 0

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 3 /14

Compteur dcompteur BCD synchrone 74190

LOAD

E N T R E E S

B

CTEN (4)

G1 CTR DIV 10

D/U (5) (12) MAX/MIN C

M2 [DOWN] 2(CT=0)Z6

M3 [UP] 3(CT=9)Z6 D

CLK (14)

1,2- / 1,3+ (13) RCO CLK

G4 6,1,4

LOAD (11) D/U

C5

CTEN

A (15) (3) QA

5D [1] +-

B (1) (2) QB QA

[2]

S O R T I E S

C (10) (6) QC

QB

[4]

D (9) (7) QD

[8] QC

QD

MAX/MIN

RCO

7 8 9 0 1 2 2 2 1 0 9 8 7

Compte Bloqu Dcompte

LOAD

Compteur dcompteur binaire synchrone 4 bits avec 2 horloges et RAZ

74193

Entre de chargement

Mot binaire charger

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 4 /14

Compteur dcompteur BCD

4510

CP

CE

CTR DIV 10

U/D

4510

MR 9 CT=0

10 TC 7 MR

U/D M1

CE 5 G

2

PL 14 C PL

3

CP 15 C 1,2 +/ C 1,2

P0

P1

P0 4 3D (1) 6 Q0

(2) P2

P1 12 11 Q1

P2 13 (4) 14 Q2 P3

P3 3 (8) 2 Q3

Q0

Q1

Q2

Q3

TC

0 1 2 3 4 5 6 7 8 9 8 7 6 5 4 3 2 1 0 0 9 6 7 0

Compteur dcompteur binaire synchrone 4 bits

Programmable 74169

C7 agit sur 7D et permet

de faire un chargement sur

front dhorloge lorsque M1

est active.

Compteur prpositionnable 74ALS169 (chargement synchrone)

Remarque : Le fonctionnement de la remise zro peut tre aussi quelque fois synchrone.

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 5 /14

74160, 74162, 74LS160A, 74LS162A, 74S162 DECADE COUNTERS 74LS160A

Typical clear, preset, count, and inhibit sequences

Illustrated below is the following sequence:

CTRDIV 10

(1) Clear outputs to zero (74160 and 74LS160A are asynchronous; 74162, 74LS162A and 74S162 are synchronous) CLR (1)

(2) Preset to BCD seven CT = 0

LOAD (9) (15) RCO

(3) Count to eight, nine, zero, one, tow, and three M1 3CT = 9

(4) Inhibit

M2

ENT (10)

G3

ENP (7)

G4

CLK (2)

C5/2,3,4+

A (3) (14) QA

1,5D [1]

B (4) (13) QB

[2]

C (5) (12) QC

[4]

D (6) (11) QD

[8]

74LS162A, 74S162

CTRDIV 10

CLR (1)

5CT = 0

LOAD (9) (15) RCO

M1 3CT = 9

M2

ENT (10)

G3

ENP (7)

G4

CLK (2)

C5/2,3,4+

A (3) (14) QA

1,5D [1]

B (4) (13) QB

[2]

C (5) (12) QC

[4]

D (6) (11) QD

[8]

74LS161A

CTRDIV 16

CLR (1)

CT = 0

LOAD (9) (15) RCO

M1 3CT = 15

M2

ENT (10)

G3

ENP (7)

G4

CLK (2)

C5/2,3,4+

A (3) (14) QA

1,5D [1]

B (4) (13) QB

[2]

C (5) (12) QC

[4]

D (6) (11) QD

[8]

74LS163A, 74S163

CTRDIV 16

CLR (1)

5CT = 0

LOAD (9) (15) RCO

M1 3CT = 15

M2

ENT (10)

G3

ENP (7)

G4

CLK (2)

C5/2,3,4+

A (3) (14) QA

1,5D [1]

B (4) (13) QB

[2]

C (5) (12) QC

[4]

(1) Clear outputs to zero D (6) (11) QD

(2) Reset to binary twelve [8]

(3) Count to thirteen, fourteen, fifteen, zero, one and two

(4) Inhibit

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 6 /14

Fiche technique du compteur 4029

06

X : Etat indiffrent

H : 1 logique

L : 0 logique

BIN : Mode de comptage binaire

DEC : Mode de comptage dcimal

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 7 /14

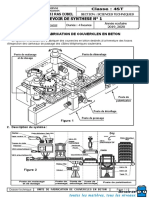

Exercice N1 : (Compteurs asynchrones en Circuits intgr) (voir dossier technique du CI 7493)

Complter les deux schmas de cblage afin de raliser un compteur modulo 12 en indiquant chaque fois le

bit de faible poids par (LSB) et le bit de fort poids par (MSB).

a - 1re solution : Le signal dhorloge est appliqu lentre CLKA:

7493

R0(1) 2 CTR

R0(2) 3 CT=0

CKA 14 DIV 2 12

QA

9

QB

DIV 8 0

CKB 1 8 QC

CT

2 11 QD

b - 2me solution : Le signal dhorloge est appliqu lentre CLKB:

7493

R0(1) 2 CTR

R0(2) 3 CT=0

CKA 14 DIV 2 12

QA

9

QB

DIV 8 0

CKB 1 8 QC

CT

2 11 QD

Exercice N2 : (Compteurs asynchrones en Circuits intgr)

(voir dossier technique du CI 7490)

1) Quel est le comptage ralis par ce circuit.

7490

R0(1) 2 CTR

R0(2) 3 CT=0

6

R9(1)

R9(2) 7 Z3

14 DIV 2

CKA 12 QA

3CT=1

DIV 5 9 QB

0

CKB 1

CT 8

QC

3CT=4

11

2 QD

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 8 /14

2) Raliser un compteur modulo 9 avec le CI 7490

7490

R0(1) 2 CTR

R0(2) 3 CT=0

6

R9(1)

R9(2) 7 Z3

14 DIV 2

CKA 12 QA

3CT=1

DIV 5 9 QB

0

CKB 1

CT 8

QC

3CT=4

11

2 QD

3) Soit le circuit suivant ralis avec le CI 7490 complter les chronogrammes

H

7490 t

R0(1) 2 CTR

CT=0

QA

R0(2) 3

R9(1) 6

t

R9(2) 7 Z3 QB

CKA 14 DIV 2 12 QA t

3CT=1 QC

DIV 5 9 QB

0

CKB 1

8 t

CT QC

3CT=4

11

QD

2 QD

t

4) Quel est le comptage ralis par ce circuit :

7490 7490

R0(1) 2 CTR R0(1) 2 CTR

R0(2) 3 CT=0 R0(2) 3 CT=0

6 6

R9(1) R9(1)

R9(2) 7 Z3 R9(2) 7 Z3

H 14 DIV 2 14 DIV 2

CKA 12 QA CKA 12 QA

3CT=1 3CT=1

DIV 5 9 QB DIV 5 9 QB

0 0

CKB 1 CKB 1

CT 8 CT 8

QC QC

3CT=4 3CT=4

11 11

2 QD 2 QD

5) Donner le schma dun compteur qui ralise 0-1-2-3-4-8-9-0 avec le CI 7490

QB est le L.S.B, QA est le M.S.B

7490

R0(1) 2 CTR

R0(2) 3 CT=0

6

R9(1)

R9(2) 7 Z3

14 DIV 2

CKA 12 QA

3CT=1

DIV 5 9 QB

0

CKB 1

CT 8

QC

3CT=4

11

2 QD

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 9 /14

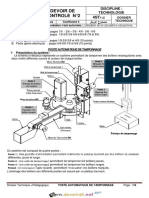

Exercice N3 : (Circuit intgr 74390)

1- Complter le schma structurel ci-dessous pour avoir un compteur modulo 14, prvoir un bouton Init

Donner lquation de CLR en fonction des sorties des compteurs et le bouton Init

CLR = .

Vers Vers

dcodeur 2 dcodeur 1

74390 74390

CTR CTR

2CLR 14 1CLR 2

CT = 0 CT = 0

2CKA 15

+

DIV2 13 2QA 1CKA 1

+

DIV2 3 1QA

11 5

2CKB 12

DIV5 0

2QB

1CKB 4

DIV5 0

1QB

+ 10 2QC + 6 1QC

1

CT CT

+Vcc 9 2QD 7 1QD

2 2

Init

Dizaine Unit

R

(Horloge)

Exercice N4 :

En utilisant le circuit intgr 4510(voir dossier technique) raliser un compteur modulo 6.Prvoir un bouton

dinitialisation. tat initial 0

CTR DIV

. MR 10

9 CT=0

4510

U/D 10 M1

TC 7

CE 5 G2

PL 1 C3

C 15 C 1,2 +/ C 1,2

P

P0 4 3D (1) 6 Q0

P 12 1 Q1

(2)

1 1

P2 13 (4) 1 Q2

4

P3 3 2 Q3

(8)

Exercice N5 :

En utilisant le circuit intgr 4510(voir dossier technique) raliser un dcompteur modulo 9. Prvoir un

bouton dinitialisation 8

CTR DIV 10

MR 4510

9

CT=0

U/D 10 M1

TC 7

CE 5 G

2

PL 1 C

3

CP 15 C 1,2 +/ C 1,2

P0 4 3D (1) 6 Q0

P1 12 11 Q1

(2)

P2 13 (4) 14 Q2

P3 3 2 Q3

(8)

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 10 /14

Exercice N6 :

En utilisant 2 C.I. 4510 raliser un compteur qui compte de 3 78. Prvoir un bouton dinitialisation 3

(cascade synchrone) puis cascade asynchrone.

CTR DIV 10 CTR DIV 10

4510 4510

MR 9 MR 9

CT=0 CT=0

U/D 10 M1 U/D 10 M1

CE 5 G

TC 7

CE 5 G

TC 7 Cascade

2 2 synchrone

PL 1 C3

PL 1 C3

CP 15 C 1,2 +/ C 1,2

CP 15 C 1,2 +/ C 1,2

P0 4 3D (1) 6 Q0 P0 4 3D (1) 6 Q0

P1 12 11 Q1 P1 12 11 Q1

(2) (2)

P2 13 (4) 14 Q2 P2 13 (4) 14 Q2

P3 3 2 Q3 P3 3 2 Q3

(8) (8)

Unit Dizaine

CTR DIV 10 CTR DIV 10

4510 4510

MR 9 MR 9

CT=0 CT=0

U/D 10 M1 U/D 10 M1

TC 7 TC 7

CE 5 G2 CE 5 G2

PL 1 C3

PL 1 C3 Cascade

CP 15 C 1,2 +/ C 1,2

CP 15 C 1,2 +/ C 1,2 asynchrone

P0 4 3D (1) 6 Q0 P0 4 3D (1) 6 Q0

P1 12 11 Q1 P1 12 11 Q1

(2) (2)

P2 13 (4) 14 Q2 P2 13 (4) 14 Q2

P3 3 2 Q3 P3 3 2 Q3

(8) (8)

Exercice N7 : Unit Dizaine

a- Raliser un dcompteur modulo 7 avec le CI 74193 (Voir dossier technique). Prvoir une entre

dinitialisation 6.

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 11 /14

b- Raliser un compteur qui compte de 2 200 avec les CI 74193 .Prvoir une entre dinitialisation 2

(cascade asynchrone)

Circuit I Circuit II

c- Raliser un dcompteur modulo 60 avec les CI 74193 .Prvoir une entre dinitialisation.(cascade

asynchrone)

Circuit I Circuit II

Exercice N8 :

Complter le schma de cblage dun compteur modulo 42 en utilisant 2 circuits 74190 (voir dossier

technique) monts en cascade asynchrone et des portes NAND. Prvoir un bouton Raz .

CTEN CTEN

G1 CTR DIV 10 MAX/MIN G1 CTR DIV 10 MAX/MIN

D/U D/U

M2 [DOWN] 2(CT=0)Z6 M2 [DOWN] 2(CT=0)Z6

M3 [UP] 3(CT=9)Z6 M3 [UP] 3(CT=9)Z6

CLK CLK

1,2- / 1,3+ RCO 1,2- / 1,3+ RCO

G4 6,1,4 G4 6,1,4

LOAD LOAD

C5 C5

A QA A QA

5D [1] 5D [1]

B QB B QB

[2] [2]

C QC C QC

[4] [4]

D QD D QD

[8] [8]

Circuit I Circuit II

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 12 /14

Exercice N9 :

En se basant sur la notice technique du CI 74161 et le circuit 74162, complter le tableau suivant :

1)

Entre CLR Entre LOAD

Vraie au niveau Asynchrone Vraie au niveau Asynchrone

bas ou haut ou synchrone bas ou haut ou synchrone

74161

74162

2) Raliser un compteur modulo 8 avec le circuit intgr 74161 proposer deux mthodes

1re mthode

74LS161A

CTRDIV 16

CLR (1)

CT = 0

LOAD (9) (15) RCO

M1 3CT = 15

M2

ENT (10)

G3

ENP (7)

G4

CLK (2)

C5/2,3,4+

A (3) (14) QA

1,5D [1]

B (4) (13) QB

[2]

C (5) (12) QC

[4]

D (6) (11) QD

[8]

2me mthode

74LS161A

CTRDIV 16

CLR (1)

CT = 0

LOAD (9) (15) RCO

M1 3CT = 15

M2

ENT (10)

G3

ENP (7)

G4

CLK (2)

C5/2,3,4+

A (3) (14) QA

1,5D [1]

B (4) (13) QB

[2]

C (5) (12) QC

[4]

D (6) (11) QD

[8]

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 13 /14

Exercice N10 : En se rfrant au dossier technique du Circuit intgr 4029 ,

1) Complter le circuit de cblage pour avoir un compteur binaire modulo 13 de cycle :

1-2-3-4-5-6-7-8-9-10-11-12-13

Avec un bouton dinitialisation

CTR DIV 10/16

9 7

4029

10

5

1

15

4 6

VCC (1)

12 11

(2)

R 13 14

Init (3)

3 2

(4)

2) Complter le circuit suivant pour avoir un dcompteur binaire de cycle 12-11-10-9-8-7-6-5-4-3-2-1-0

avec un bouton dinitialisation

CTR DIV 10/16

9 7

4029

10

5

1

15

VCC

4 6

(1)

R 12 11

Init (2)

13 14

(3)

3 2

(4)

Exercice N11 :

Le circuit suivant est ralis avec les CI 4510 et le CI 7483 (voir dossier technique). Quel est le comptage

ralis par les circuits U1 et U2 ?

Comptage ralis par U1 ..

Comptage ralis par U2 ..

VCC

U1

U1(CLK) 4 6

A1 Q1

12 11

A2 Q2

13 14

A3 Q3

3 2

A4 Q4

15 U3

CLK

5 7 10 9

CI CO A1 S1

10 8 6

U/D A2 S2

1 3 2

PE A3 S3

9 1 15

MR A4 S4

4510 11

B1

7

B2

4

B3

16

U2 B4

4 6 13 14

A1 Q1 C0 C4

12 11

A2 Q2

13 14 7483

A3 Q3

3 2

A4 Q4

15

CLK

5 7

CI CO

10

U/D

1

PE

9

MR

4510

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Laboratoire gnie lectrique 4Stech Srie dexercices N2 Compteurs Page 14 /14

Exercice N12 :

En se rfrant au dossier technique du CI 74190 et pour D C B A = 0 0 1 1

Complter les chronogrammes suivants :

1

Clk

0

1

CTEN

0

1

D/U

0

1

LOAD

0

1

QA

0

1

QB

0

1

QC

0

1

QD

0

Valeur du compteur

en dcimal N(10)

1

RCO

0

Prof : Borchani hichem et Hammami mourad www.seriestech.com

Vous aimerez peut-être aussi

- Série D'exercices N°2 - Génie Électrique - Compteur À Base Des Circuits Intégrés - Bac Technique (2015-2016) MR Raouafi AbdallahDocument12 pagesSérie D'exercices N°2 - Génie Électrique - Compteur À Base Des Circuits Intégrés - Bac Technique (2015-2016) MR Raouafi Abdallahfehmi001100% (1)

- Devoir de Synthèse N°1 2019 2020 (MR Ben Aouicha)Document10 pagesDevoir de Synthèse N°1 2019 2020 (MR Ben Aouicha)Piere EbrahimPas encore d'évaluation

- 19 VHDLDocument15 pages19 VHDLAmina GhardallouPas encore d'évaluation

- R R 1) - CKA: Entrée D'horloge (DIV2) - CKB: Entrée D'horloge (DIV8) - Q Q Q QDocument50 pagesR R 1) - CKA: Entrée D'horloge (DIV2) - CKB: Entrée D'horloge (DIV8) - Q Q Q QAndy TchuisseuPas encore d'évaluation

- CompteurDocument2 pagesCompteurBrahamChaoucheFethallahYacinePas encore d'évaluation

- A2 1 Compteurs Integrés 17 18Document11 pagesA2 1 Compteurs Integrés 17 18Oumayma Ben MoussaPas encore d'évaluation

- Logique Séquentielle: Compteurs Intégrés AsynchronesDocument16 pagesLogique Séquentielle: Compteurs Intégrés AsynchronesbejaouiPas encore d'évaluation

- DC1 4T Dpe 17 CorrectionDocument4 pagesDC1 4T Dpe 17 Correctiontakecoin767Pas encore d'évaluation

- Activites Microcontroleur 16f84aDocument8 pagesActivites Microcontroleur 16f84aHichem HamdiPas encore d'évaluation

- DT 2Document5 pagesDT 2Rami AliPas encore d'évaluation

- Devoir de Synthèse N°1 - Génie Électrique - Bac Technique (2011-2012) MR Raouafi AbdallahDocument4 pagesDevoir de Synthèse N°1 - Génie Électrique - Bac Technique (2011-2012) MR Raouafi AbdallahFethi BenmassoudePas encore d'évaluation

- Serie1 Combinatoire 2022 2023Document13 pagesSerie1 Combinatoire 2022 2023Fares BouzidiPas encore d'évaluation

- TRAVAUX DIRIGES EN ETUDE DE SYSTEME TECHNIQUE OkDocument3 pagesTRAVAUX DIRIGES EN ETUDE DE SYSTEME TECHNIQUE Okjosias zinsou100% (1)

- TP No 03 Les Afficheurs 7 SegmentsDocument2 pagesTP No 03 Les Afficheurs 7 Segmentsmustapha skanderPas encore d'évaluation

- Devoir de Synthèse N°1 2012 2013 (Dhahri Salah)Document6 pagesDevoir de Synthèse N°1 2012 2013 (Dhahri Salah)Youssef CherniPas encore d'évaluation

- Auto - 1 - 2023 OkDocument8 pagesAuto - 1 - 2023 OkfjosephfabricePas encore d'évaluation

- Serie MCCDocument7 pagesSerie MCCrzougarzougaPas encore d'évaluation

- Le Circuit Integre Ne555Document4 pagesLe Circuit Integre Ne555Sami Mahjoubi100% (1)

- Série N - 6 Ali 2015 FinaleDocument14 pagesSérie N - 6 Ali 2015 FinaleHichem HamdiPas encore d'évaluation

- Upload - Série D'exercices N°4-3tech-Bascules-2013-2014-CorrectionDocument5 pagesUpload - Série D'exercices N°4-3tech-Bascules-2013-2014-CorrectionchediPas encore d'évaluation

- Grafcet Synchronisé: I - Description Du SystèmeDocument4 pagesGrafcet Synchronisé: I - Description Du SystèmeNou Ha BenabdallahPas encore d'évaluation

- 2015-16 DE Correction Sysnum PDFDocument5 pages2015-16 DE Correction Sysnum PDFRoland KambirePas encore d'évaluation

- 4 Logique Sequentielle PDFDocument24 pages4 Logique Sequentielle PDFkhocinePas encore d'évaluation

- Correction DS1 Bac 2021 2022Document4 pagesCorrection DS1 Bac 2021 2022Kadri MongiPas encore d'évaluation

- Correction Bac Blanc FINALDocument3 pagesCorrection Bac Blanc FINALAh MédPas encore d'évaluation

- Devoir de Synthèse N°1 - Technologie - 3ème Technique (2010-2011) MR Abdallah RaouafiDocument4 pagesDevoir de Synthèse N°1 - Technologie - 3ème Technique (2010-2011) MR Abdallah RaouafiOthman TmarPas encore d'évaluation

- Compteur DecompteurDocument7 pagesCompteur DecompteurAzed RhouatPas encore d'évaluation

- 02 Logiques SequentiellesDocument8 pages02 Logiques SequentiellesMohamed aziz ben sassiPas encore d'évaluation

- Cours Lycée Pilote - Technologie Le GRAFCET - 2ème Sciences (2014-2015) MR Rafik Ben AmorDocument10 pagesCours Lycée Pilote - Technologie Le GRAFCET - 2ème Sciences (2014-2015) MR Rafik Ben AmorHana KhemissiPas encore d'évaluation

- Système À Étudier - Carton PréforméDocument14 pagesSystème À Étudier - Carton PréforméESSOME ESSOME OLIVIER STEPHANEPas encore d'évaluation

- 02 - Système Automatique de Marquage de Boîtiers (DR)Document4 pages02 - Système Automatique de Marquage de Boîtiers (DR)FM HELSENKI0% (2)

- Pic 16 F 877Document10 pagesPic 16 F 877Youssef Boughallad100% (1)

- SERIE12345 Semestre 2Document15 pagesSERIE12345 Semestre 2Sabrina BenghenamePas encore d'évaluation

- EMD0203Document11 pagesEMD0203FouadHbPas encore d'évaluation

- Devoir de Contrôle N°1 - Génie Électrique Distributeur de Boisson Chaude - Bac Technique (2011-2012) MR Ben JaballahDocument5 pagesDevoir de Contrôle N°1 - Génie Électrique Distributeur de Boisson Chaude - Bac Technique (2011-2012) MR Ben JaballahHichem Hamdi67% (3)

- SERIE - 2 - TDs - Logique CombinatoireDocument5 pagesSERIE - 2 - TDs - Logique CombinatoireAnge nolwenPas encore d'évaluation

- Simulation Des Fonctions Logiques de BaseDocument2 pagesSimulation Des Fonctions Logiques de Basemekki100% (1)

- Électronique TsaDocument21 pagesÉlectronique TsaadamsclovisherbertsPas encore d'évaluation

- Lecon A2-3 - Circuits Combinatoires-1Document5 pagesLecon A2-3 - Circuits Combinatoires-1Ahmed Belhadj100% (2)

- DS34STDocument7 pagesDS34STZaraki RiodaPas encore d'évaluation

- Contrôle Microcontrôleur EHTP 2016 2017Document4 pagesContrôle Microcontrôleur EHTP 2016 2017zinebPas encore d'évaluation

- Logique CombinatoireDocument9 pagesLogique CombinatoireRouaissi Ridha100% (1)

- Transformateur Monophase RoneDocument8 pagesTransformateur Monophase RoneBabacar TounkaraPas encore d'évaluation

- Mas Serie 1Document4 pagesMas Serie 1Mbairassem IsidorePas encore d'évaluation

- Automates Programmables Industriels (A.P.I)Document26 pagesAutomates Programmables Industriels (A.P.I)Hayet BechedliPas encore d'évaluation

- Serie9 Asservissement PDFDocument8 pagesSerie9 Asservissement PDFHichem HamdiPas encore d'évaluation

- TD 2Document5 pagesTD 2adda chariPas encore d'évaluation

- TD 2 MesureDocument2 pagesTD 2 MesureChaouki GuesmiPas encore d'évaluation

- Serie D'exercices 4 BASCULES 2021-2022Document3 pagesSerie D'exercices 4 BASCULES 2021-2022Manel AsnicarPas encore d'évaluation

- Convertisseurs CorrigeDocument4 pagesConvertisseurs Corrigeahmed100% (1)

- Partie Genie Electrique: Nom: ... Prénom: . . N°: . . 4STDocument4 pagesPartie Genie Electrique: Nom: ... Prénom: . . N°: . . 4STHakim SaidiPas encore d'évaluation

- Devoir de Contrôle N°2 - Génie Mécanique - Mécanisme D'entrainement Du Plateau Tournant - Bac Technique (2017-2018) MR MR GHORBEL MamdouhDocument8 pagesDevoir de Contrôle N°2 - Génie Mécanique - Mécanisme D'entrainement Du Plateau Tournant - Bac Technique (2017-2018) MR MR GHORBEL MamdouhAmira JebaliPas encore d'évaluation

- STI Genie Electronique ESTIDocument35 pagesSTI Genie Electronique ESTILetudiant.fr100% (2)

- Présentation Du SujetDocument2 pagesPrésentation Du SujetMohsen Saidi100% (1)

- TD Trie de Caisses ElevDocument2 pagesTD Trie de Caisses ElevNabilPas encore d'évaluation

- Chapitre 2 Les Compteurs 2016 2017 (MR Azzem Mohamed) (Metlaoui Gafsa)Document8 pagesChapitre 2 Les Compteurs 2016 2017 (MR Azzem Mohamed) (Metlaoui Gafsa)Azerty QsdfghPas encore d'évaluation

- 4ST ComptDocument7 pages4ST ComptRouaissi RidhaPas encore d'évaluation

- slntp4 PDFDocument2 pagesslntp4 PDFRastatePas encore d'évaluation

- Annexe: Extrait de La Fiche Technique Du Circuit 7490Document2 pagesAnnexe: Extrait de La Fiche Technique Du Circuit 7490takecoin767Pas encore d'évaluation

- 01 Exercice n01 SujetDocument3 pages01 Exercice n01 SujetMohamed aziz ben sassi0% (1)

- Comp Asy Elev 2017Document10 pagesComp Asy Elev 2017Hayet BechedliPas encore d'évaluation

- Sis-2 0Document5 pagesSis-2 0Rached DouahchuaPas encore d'évaluation

- Étape 1Document2 pagesÉtape 1Rached DouahchuaPas encore d'évaluation

- STEG - Paiement FactureDocument1 pageSTEG - Paiement FactureRached DouahchuaPas encore d'évaluation

- CV Kamel ZaianeDocument2 pagesCV Kamel ZaianeRached DouahchuaPas encore d'évaluation

- Trakker Euro 6 Edition DuDocument14 pagesTrakker Euro 6 Edition DuRached Douahchua100% (1)

- Logimot Gestion de Parc de VéhiculesDocument31 pagesLogimot Gestion de Parc de VéhiculesRached Douahchua100% (1)

- ET Cat Electronic Technician Manual Del Usuario EF CATERPILLARDocument82 pagesET Cat Electronic Technician Manual Del Usuario EF CATERPILLARRached Douahchua100% (6)

- Manuel TechniqueDocument515 pagesManuel TechniqueRached Douahchua100% (4)

- Cifa 10152 K2 X PA 1506 909 F8 PDFDocument9 pagesCifa 10152 K2 X PA 1506 909 F8 PDFRached Douahchua100% (3)

- Upload-Série D'exercices N°2-4tech-Compteur-2014-2015 PDFDocument14 pagesUpload-Série D'exercices N°2-4tech-Compteur-2014-2015 PDFRached Douahchua100% (1)

- Variateur de Vitesse YASKAWA: Manuel de Mise en Route RapideDocument136 pagesVariateur de Vitesse YASKAWA: Manuel de Mise en Route RapideRached DouahchuaPas encore d'évaluation

- W Brochure SP15-SP15i-World 0216 FR PDFDocument44 pagesW Brochure SP15-SP15i-World 0216 FR PDFRached DouahchuaPas encore d'évaluation

- W Brochure SP15-SP15i-World 0216 FR PDFDocument44 pagesW Brochure SP15-SP15i-World 0216 FR PDFRached DouahchuaPas encore d'évaluation

- Upload - Série D'exercices N°1-4tech-Logique Combinatoire-2014-2015Document9 pagesUpload - Série D'exercices N°1-4tech-Logique Combinatoire-2014-2015Hichem HamdiPas encore d'évaluation

- 9000 3 FR Original PDFDocument6 pages9000 3 FR Original PDFRached DouahchuaPas encore d'évaluation

- Cadre Devis Bordereau Prd2016 FouchanaDocument8 pagesCadre Devis Bordereau Prd2016 FouchanaRached DouahchuaPas encore d'évaluation

- CCTP - PRD 2016 Mhamdia5Document93 pagesCCTP - PRD 2016 Mhamdia5Rached DouahchuaPas encore d'évaluation

- Manuel Esd5500ece VR PDFDocument8 pagesManuel Esd5500ece VR PDFRached DouahchuaPas encore d'évaluation

- Avis Non Responsabilite Accident PDFDocument2 pagesAvis Non Responsabilite Accident PDFRached DouahchuaPas encore d'évaluation

- Rapport Accident PDFDocument5 pagesRapport Accident PDFRached DouahchuaPas encore d'évaluation

- LES CIRCUITS LOGIQUE ProgrammableDocument71 pagesLES CIRCUITS LOGIQUE ProgrammableAhmed DoghmiPas encore d'évaluation

- EI21 - Corrigé TD1 - Les Amplificateurs Opérationnels LinéairesDocument4 pagesEI21 - Corrigé TD1 - Les Amplificateurs Opérationnels LinéairesAla MassoudiPas encore d'évaluation

- Cours Up Beguenane 5Document16 pagesCours Up Beguenane 5zied houanebPas encore d'évaluation

- Bios BipDocument5 pagesBios Bipyassinedmx100% (1)

- Chap 3-L Fonct Logiq CombDocument119 pagesChap 3-L Fonct Logiq CombHela MloukaPas encore d'évaluation

- Exercices D'application Bascules Et Compteurs - SemicorrigéDocument8 pagesExercices D'application Bascules Et Compteurs - SemicorrigéASSIA SAOUDIPas encore d'évaluation

- VHDLDocument121 pagesVHDLRafik OudaoudPas encore d'évaluation

- Logique Programmable Réseaux Et Circuits PLA, PAL, GAL Et CPLDDocument17 pagesLogique Programmable Réseaux Et Circuits PLA, PAL, GAL Et CPLDMouhcine ZianeePas encore d'évaluation

- Chap 3 Les BasculesDocument20 pagesChap 3 Les BasculesAhmed BelhadjPas encore d'évaluation

- TP2 CAO ElectroniqueDocument10 pagesTP2 CAO Electroniquefersi mouhibPas encore d'évaluation

- TD1 ArmDocument4 pagesTD1 Armazza memmiPas encore d'évaluation

- Chapitre 2 2 Les RegistresDocument5 pagesChapitre 2 2 Les RegistresIddir YuderPas encore d'évaluation

- Chapitre2 - Circuits LogiquesDocument18 pagesChapitre2 - Circuits LogiquesMuding BkPas encore d'évaluation

- 07 Analsye de Circuits SequentielsDocument7 pages07 Analsye de Circuits SequentielsABDELAZIZ HAMDAOUIPas encore d'évaluation

- Architecture de BaseDocument7 pagesArchitecture de BaseDivin BoudzoumouPas encore d'évaluation

- Gel 625 - Cours - VHDL1Document44 pagesGel 625 - Cours - VHDL1Ismael AdjinilePas encore d'évaluation

- Micro CDocument8 pagesMicro CSelim RachdiPas encore d'évaluation

- Chapitre 5Document34 pagesChapitre 5Yannick Stephane NouchiPas encore d'évaluation

- Exercices Architecture 4 CITISEDocument8 pagesExercices Architecture 4 CITISEchfakhtPas encore d'évaluation

- Ch6 Pal FplaDocument33 pagesCh6 Pal FplaAnonymous kIoMGEPas encore d'évaluation

- Microcontrôleurs À Signaux Mixtes MSP430G2553 - TI - DigiKeyDocument4 pagesMicrocontrôleurs À Signaux Mixtes MSP430G2553 - TI - DigiKeynonoPas encore d'évaluation

- TD2 - P APIDocument2 pagesTD2 - P APIMohammed ALMUSHIAAPas encore d'évaluation

- Chapitre 1 Lat 54Document6 pagesChapitre 1 Lat 54radiaPas encore d'évaluation

- Hadj Said DjamelDocument92 pagesHadj Said DjamelSarah MessaouiPas encore d'évaluation

- Chapitre VI ConceptionDocument17 pagesChapitre VI ConceptionAlouani KacemPas encore d'évaluation

- VHDL TP 0506Document5 pagesVHDL TP 0506Haythem ChaouedPas encore d'évaluation

- Présentation Pfe Principale - PPTX (Autosaved)Document52 pagesPrésentation Pfe Principale - PPTX (Autosaved)Taha Chergui MouanePas encore d'évaluation

- OutputDocument134 pagesOutputDouar AymenPas encore d'évaluation