Académique Documents

Professionnel Documents

Culture Documents

TP3 AM Isis

Transféré par

Anas FarhaouiTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TP3 AM Isis

Transféré par

Anas FarhaouiDroits d'auteur :

Formats disponibles

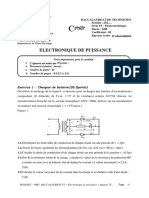

Electronique des systèmes Master_GE 2022/2023

TP3 : Modulation démodulation d’amplitude

But : Le but de cette manipulation est d’étudier certains circuits réalisant la modulation

et démodulation d’amplitude. On utilisera notamment un multiplieur analogique en

l’occurrence le circuit ADJ633.

Théorie

1. modulation Vm(t) V’s(t)

X Vs(t)

On considère le modulateur composé d’un multiplieur +

et d’un additionneur (figure 1). Le gain du multiplieur Vp(t)

sera noté km et celui de l’additionneur Ad. La Figure 1

porteuse

vp(t)=Vp Cos(2πfpt) et vm(t) représente le signal modulant à transmettre.

1.1. Exprimer vs(t) dans le cas où vm(t) = Vm cos(2πfmt) et la mettre sous la forme :

vs(t)=Vp[1+m cos(2πfmt)]cos(2πfpt) en précisant l’expression de m.

1.2. Représenter vs(t) et son spectre d’amplitude pour m = 0,5.

1.3. Exprimer vs(t) dans le cas où vm(t) admet un spectre s’étalant jusqu’à fmax.

Représenter le spectre de vs(t).

2. Détection d’enveloppe

On considère le montage de la figure 2. Il est attaqué par la tension vs(t) qui est un signal

AM avec un taux de modulation m = 0,5.

Figure 2: Détecteur Figure 3: Filtre passe bas

2.1. Représenter sur le même graphe vs(t) et v0(t).

2.2. On met en parallèle sur R’ un condensateur C’. Quelle devrait être la valeur de la

constante de temps τ=R’C’.

2.3. Représenter sur le même graphe les tensions v0(t) avant et après branchement de C’.

2.4. Pour améliorer le filtrage on utilise le filtre passe bas de la figure 3. Calculer sa

fonction de transfert. Représenter son diagramme de Bode. En déduire l’expression de sa

fréquence de coupure fc. Proposer alors des valeurs pour R0 et C0.

3. Détection synchrone

Le schéma de principe est celui de la figure 4. On suppose que la porteuse se met sous la

forme v’p(t)=V’p Cos(Ωp t+φ).

u(t) v(t) Suppression

X v’m(t)

vs(t) composante =

Passe bas

Porteuse

Figure 4: Schéma de principe d’une démodulation synchrone

3.1. Exprimer u(t) en prenant km pour le gain du multiplieur. Tracer le spectre de u(t).

3.2. On suppose le filtre passe bas idéal, exprimez v(t) et v’m(t).

3.3. Etudiez l’effet de la phase φ et Conclure.

Simulation

Université Cadi Ayyad Faculté des Sciences et Techniques Guéliz 1

Electronique des systèmes Master_GE 2022/2023

1. Modulation : On prendra fp=10kHz, Vp=5V, fm=1kHz et VCC=15V.

1.1. Placez le multiplieur AD633 dans l’espace de travail.

1.2. Placez deux générateurs de tension continue pour VCC et VDD=-VCC.

1.3. Placez deux générateurs de tension sinusoïdale pour Vm et Vp.

1.4. Connecter les éléments pour avoir le schéma suivant (fig. 5) :

Vm VCC

U1

1 8

X1 VS+

Vp 2 7 Vs

X2 W

3 6

Y1 Z

4 5

Y2 VS-

AD633

VDD

Figure 5 : Schéma du modulateur

1.5. Réglez VCC, VDD et Vp.

1.6. Visualiser sur l’oscilloscope la tension de sortie vs(t) présente sur la borne 7 ainsi que

vm(t). Régler alors l’amplitude de vm(t) pour avoir un taux de modulation m=0.5.

1.7. Placez un graphique de type « analogue analysis ». Editer les propriétés du graphique

fixer correctement le stop time. Ajouter « add traces » la courbe de vm(t) et vs(t) sur le

graphe.

1.8. Insérez les courbes obtenues dans votre compte rendu et faire un commentaire.

1.9. Insérez un graphique de type « Fourier » pour tracer le spectre de vs(t).

1.10. Donnez le spectre de vs(t) et faire un commentaire.

1.11. Changez fm et regarder l’effet sur le spectre.

1.12. Connectez, à la masse, la borne 6(Z) du circuit pour avoir une modulation sans

porteuse. Relevez alors le spectre de vs(t).

1.13. Remettre la borne Z(6) à vp(t) pour avoir une modulation avec porteuse.

2. Démodulation par détection d’enveloppe

2.1. Rajouter le détecteur d’enveloppe suivant (fig. 6) :

VDD

U2

4

5

2 D1 v0

6

Vs 3

DIODE

AD711

7

1

R1

1k

VCC

Figure 6 : Schéma du détecteur d’enveloppe

2.2. Visualisez la tension vs(t) et la sortie du détecteur en utilisant un graphique de type

« analogue analysis ». Insérez les courbes dans le compte rendu. Expliquer le rôle du

montage.

2.3. Tracez le spectre et donner les fréquences présentes dans le signal.

2.4. Mettre une capacité en parallèle sur la sortie du redresseur. Fixez la valeur de cette

capacité pour avoir un filtrage correct.

2.5. Relevez la sortie du détecteur et faire un commentaire.

2.6. Ajoutez un filtre passe bas R0C0 avec R0=10KΩ. Réglez C0 pour laisser passer la

fréquence fm. Donnez la valeur de C0.

2.7. Visualisez et représenter la tension de sortie vc(t). Faire un commentaire.

Université Cadi Ayyad Faculté des Sciences et Techniques Guéliz 2

Electronique des systèmes Master_GE 2022/2023

3. Démodulation synchrone

3.1. Effet de la phase de la porteuse

3.1.1. Réalisez le montage de la figure 7. Calculer la fonction de transfert du filtre et

proposer des valeurs pour R, C1 et C2.

Figure 7 : Etude de l’effet de la phase de la poreuse

3.1.2. Réglez C pour avoir un déphasage nul et vérifier que la démodulation se fait

correctement. Relevez alors sur un même graphe vm(t) et le signal démodulé pour une

modulation avec et sans porteuse.

3.1.3. Réglez C pour avoir un déphasage égal à π/2 et montrer que la démodulation ne

fonctionne pas.

3.1.4. Réglez C pour avoir un déphasage égal à π. Relevez alors sur un même graphe

vm(t) et le signal démodulé pour une modulation avec et sans porteuse. Expliquez.

3.2. Reconstitution de la porteuse

Pour reconstituer la porteuse on utilise une PLL modélisé par le montage suivant (fig. 8).

V'p

+

S1

OP : MULTIPLY

-

Vs

R4 AM FM

10k

C5

10n

Figure 8 : Modèle de la PLL

3.2.1. Implémentez le circuit sur Isis en mettant un signal d’entrée vs(t) à 10kHz et 5V

d’amplitude.

3.2.2. Réglez la fréquence centrale du VCO (générateur) à 10kHz. Réglez le niveau

(level) autour de 5V.

3.2.3. Paramétrez correctement le filtre passe bas pour avoir un signal de sortie stable.

Expliquez votre démarche.

3.2.4. Relevez la porteuse reconstituée v’p(t) et mesurez son déphasage par rapport à

vs(t).

3.2.5. Ajoutez un filtre correcteur de phase et régler le circuit pour avoir en sortie une

porteuse en phase avec vs(t). donnez alors le schéma du filtre correcteur de phase et les

valeurs des éléments.

3.3. Démodulation

3.3.1. Attaquer la PLL par le signal modulé AM. Ajoutez un autre multiplieur et le filtre

passe bas (voir figure 7).

3.3.2. Dimensionnez correctement le filtre passe bas.

3.3.3. Relevez le signal modulant de départ vm(t) et le signal démodulé v’m(t).

comparez et conclure.

Université Cadi Ayyad Faculté des Sciences et Techniques Guéliz 3

Vous aimerez peut-être aussi

- Exercices d'optique et d'électromagnétismeD'EverandExercices d'optique et d'électromagnétismeÉvaluation : 5 sur 5 étoiles5/5 (1)

- TD2 CorrigeDocument35 pagesTD2 CorrigeRoland Kitoko100% (1)

- Kabouri - TD2 MES 21 22Document4 pagesKabouri - TD2 MES 21 22Loubna MhamPas encore d'évaluation

- Physique STI ElectroniqueDocument16 pagesPhysique STI ElectroniqueLetudiant.frPas encore d'évaluation

- TD1 Mes 21 22Document5 pagesTD1 Mes 21 22Boualoulou NouhailaPas encore d'évaluation

- TP Electronique REDRESSEMENT FILTRAGE Par Armel Sitou AfanouDocument11 pagesTP Electronique REDRESSEMENT FILTRAGE Par Armel Sitou AfanouHamid BendjelloulPas encore d'évaluation

- Chapitre 2Document9 pagesChapitre 2kima lachgarPas encore d'évaluation

- TD Rdresseur Code MCCDocument4 pagesTD Rdresseur Code MCCESSADIKE ZAITAPas encore d'évaluation

- TP Electronique REDRESSEMENT FILTRAGE Par Armel Sitou AfanouDocument11 pagesTP Electronique REDRESSEMENT FILTRAGE Par Armel Sitou Afanoukima lachgarPas encore d'évaluation

- TD2 Gim2 Geii219 20Document3 pagesTD2 Gim2 Geii219 20Hàmža Ait BoulhcenPas encore d'évaluation

- TP n1 Bonlougou Ouenigamou Redressement MonophaseDocument19 pagesTP n1 Bonlougou Ouenigamou Redressement MonophasePaul BonlougouPas encore d'évaluation

- Derouech Si Tsi-Ge 2Document9 pagesDerouech Si Tsi-Ge 2AYMEN BOUNDARPas encore d'évaluation

- Sq2 Ep 2022 MohouaDocument4 pagesSq2 Ep 2022 MohouaJulesPas encore d'évaluation

- Série de TD N°1 Diodes Et ApplicationsDocument9 pagesSérie de TD N°1 Diodes Et ApplicationsTALAL EL MOUNEPas encore d'évaluation

- Sujet 1 Physique Appliquee Bac f2 2023 2Document8 pagesSujet 1 Physique Appliquee Bac f2 2023 2N'goran JuniorPas encore d'évaluation

- Examen 08 09 Session2Document5 pagesExamen 08 09 Session2Aaouine AbderrazzakPas encore d'évaluation

- Epreuve 1Document6 pagesEpreuve 1ChristianPas encore d'évaluation

- Calcul - Condensateurs de Liaison Ou de DécouplageDocument6 pagesCalcul - Condensateurs de Liaison Ou de Découplagetounsimed100% (1)

- Polycope TP ElectroniqueDocument11 pagesPolycope TP ElectroniqueAbderrahmane Maths100% (1)

- Sujet BTS Maths GroupeADocument7 pagesSujet BTS Maths GroupeACharles EkolloPas encore d'évaluation

- TD AOP 2022-2023Document10 pagesTD AOP 2022-2023bayouedraogo100% (1)

- TD N2Document5 pagesTD N2Faical MalaliPas encore d'évaluation

- TD3 global ATC ADC.pdf · إصدار ١Document16 pagesTD3 global ATC ADC.pdf · إصدار ١walidechabaki1Pas encore d'évaluation

- Epreuve Zéro D'electronique de Puissance Bac F3Document4 pagesEpreuve Zéro D'electronique de Puissance Bac F3Aymard Mougou100% (2)

- Chapitre6 Electronique de Puissance AvancéeDocument7 pagesChapitre6 Electronique de Puissance AvancéeIssam SteitPas encore d'évaluation

- TP-02-Syst-Lin-ass S4 Auto.Document4 pagesTP-02-Syst-Lin-ass S4 Auto.Djameleddine BougrinePas encore d'évaluation

- Correction TD3 ENPDocument17 pagesCorrection TD3 ENPgolden aaaPas encore d'évaluation

- Examen 2014 PG GE 02Document5 pagesExamen 2014 PG GE 02Meriem IdirPas encore d'évaluation

- Sujet TP ElecDocument50 pagesSujet TP Elecmelissaissa722Pas encore d'évaluation

- TD1 Variateur Vitesse 2021Document17 pagesTD1 Variateur Vitesse 2021Anass BentozerPas encore d'évaluation

- TP RLC Fonc Elct2013Document4 pagesTP RLC Fonc Elct2013Hmouma Dahmane100% (1)

- TD Cna-CanDocument5 pagesTD Cna-CanEmmanuelPas encore d'évaluation

- TD Traitement Du SignalDocument3 pagesTD Traitement Du SignalBenabdi YousraPas encore d'évaluation

- ENPU2023Document3 pagesENPU2023Taf AmourPas encore d'évaluation

- Les Capteurs, 62 Exercices Et Problèmes CorrigésDocument4 pagesLes Capteurs, 62 Exercices Et Problèmes CorrigésSòumia El67% (6)

- TP ElectroniqueDocument16 pagesTP ElectroniqueazizhamdiPas encore d'évaluation

- EEADocument7 pagesEEAR RPas encore d'évaluation

- RedresseursDocument48 pagesRedresseursBousmaha YoucefPas encore d'évaluation

- Capteur A TractionDocument12 pagesCapteur A TractionOualid HarroudPas encore d'évaluation

- CCDocument6 pagesCCAz-eddine KaibaPas encore d'évaluation

- TD2 RedresseursDocument7 pagesTD2 RedresseursAhmad Whabi100% (1)

- College Saint Paul Devoir N°2 Epnu 2023Document3 pagesCollege Saint Paul Devoir N°2 Epnu 2023Waf NgongangPas encore d'évaluation

- Examen EFFET ZENER ET AVALENCHEDocument6 pagesExamen EFFET ZENER ET AVALENCHEJone JonathanPas encore d'évaluation

- Examen 04 02 2005Document7 pagesExamen 04 02 2005Mohamed DallagiPas encore d'évaluation

- TD 1 Gim2 S2-2020-2021Document3 pagesTD 1 Gim2 S2-2020-2021Ťå Ř ÏqPas encore d'évaluation

- Copte Rendu tp1Document5 pagesCopte Rendu tp1ilyPas encore d'évaluation

- TD Coe302Document17 pagesTD Coe302Sarah HadiPas encore d'évaluation

- TP1 OscillateursDocument12 pagesTP1 OscillateursRaghadPas encore d'évaluation

- (Annales 3GE) (ETEP1) (DS) 2014 SDocument5 pages(Annales 3GE) (ETEP1) (DS) 2014 SHamza SadikPas encore d'évaluation

- Ab TD Série3 Etude Dynamique EnvoyeeDocument3 pagesAb TD Série3 Etude Dynamique EnvoyeedzererPas encore d'évaluation

- TD 2 MultivibrateurDocument2 pagesTD 2 MultivibrateurSamir Nait0% (1)

- Exercices Elec1112Document33 pagesExercices Elec1112Abderrahman Lahouaoui50% (2)

- Devoir Libre (s2) - TransistorsDocument2 pagesDevoir Libre (s2) - TransistorsAjana AminePas encore d'évaluation

- Devoir1 ApplicationsMatlab 19-20Document2 pagesDevoir1 ApplicationsMatlab 19-20Assia MhiaouiPas encore d'évaluation

- TD Oscillateur Corrigé PDFDocument16 pagesTD Oscillateur Corrigé PDFNes Rine81% (36)

- Simulation D'un Hacheur Série Et Commande D'un Moteur À Courant ContinuDocument4 pagesSimulation D'un Hacheur Série Et Commande D'un Moteur À Courant ContinumarPas encore d'évaluation

- M2107: Principe Des Transmissions Radio Thibault - Aubriot@Document39 pagesM2107: Principe Des Transmissions Radio Thibault - Aubriot@Felix Chokwe Danra TaissalaPas encore d'évaluation

- TTL Et CMOSDocument5 pagesTTL Et CMOSEdgar ANDRIAMAHEFAPas encore d'évaluation

- Fonctions de L'électroniqueDocument2 pagesFonctions de L'électroniquepiw miw100% (1)

- Synthétiseur de Fréquence ImportantDocument13 pagesSynthétiseur de Fréquence ImportantAbderazzaqe ElmoumanPas encore d'évaluation

- TD10 Mod Num CorrectionDocument3 pagesTD10 Mod Num CorrectionArsene Loic Mbanda BiamouPas encore d'évaluation

- TP ElecPInge2 2017-2018 v3 PDFDocument21 pagesTP ElecPInge2 2017-2018 v3 PDFMohamed BelaounPas encore d'évaluation

- Chapitre 2Document113 pagesChapitre 2Fadila FEPas encore d'évaluation

- Decrypt ElDocument15 pagesDecrypt ElAbderrahmen AbderrahmenPas encore d'évaluation

- Cours MA ISGE IC2 2019 2020Document62 pagesCours MA ISGE IC2 2019 2020Enoch BidimaPas encore d'évaluation

- Btsse 2016Document46 pagesBtsse 2016AFADPas encore d'évaluation

- Conception Dun Melangeur de Frequences ADocument122 pagesConception Dun Melangeur de Frequences AAyman LamzouriPas encore d'évaluation

- Cours PLL CompletDocument13 pagesCours PLL CompletYassine BelhmerPas encore d'évaluation

- Trans Num l3 1Document107 pagesTrans Num l3 1Souad Najoua LagmiriPas encore d'évaluation

- TRAVAUX PRATIQUES VHDL AMS ConvertisseurDocument11 pagesTRAVAUX PRATIQUES VHDL AMS ConvertisseurSanae SEPas encore d'évaluation

- Cours CA - Bersali1 - 2022 - P1 - Notions de Base en RadiofréquenceDocument13 pagesCours CA - Bersali1 - 2022 - P1 - Notions de Base en RadiofréquenceAzzedine HallazPas encore d'évaluation

- Géné VHF 1Hz À 100MHz À DDS AD9951 Piloté Par GPSDocument76 pagesGéné VHF 1Hz À 100MHz À DDS AD9951 Piloté Par GPSJean Marie PolardPas encore d'évaluation

- S Parameters Antennas Amplifiers ReviewDocument59 pagesS Parameters Antennas Amplifiers ReviewFeki SamarPas encore d'évaluation

- TD10 Mod FSK GMSK ElmCorDocument2 pagesTD10 Mod FSK GMSK ElmCorAsmaa ErramziPas encore d'évaluation

- Wouxun Kg-Uv920 SMDocument38 pagesWouxun Kg-Uv920 SMKrishna Pratap RanaPas encore d'évaluation

- Modem FSKDocument7 pagesModem FSKHasnae MoumniPas encore d'évaluation

- DV Toussaint S32016 CorrectionDocument5 pagesDV Toussaint S32016 CorrectionGray AbPas encore d'évaluation

- PLL PDFDocument23 pagesPLL PDFRroouuffaa AbbesPas encore d'évaluation

- There MineDocument5 pagesThere MinedudulemarcPas encore d'évaluation

- TRANSMISSION ANALOGIQUE Cours PDFDocument29 pagesTRANSMISSION ANALOGIQUE Cours PDFHarun Le Principal Gomina100% (1)

- Toute La Modulation Et La Démodulation D'amplitude Sur Une Maquette DidactiqueDocument23 pagesToute La Modulation Et La Démodulation D'amplitude Sur Une Maquette DidactiquebirkissamhaiwanggamdandiPas encore d'évaluation

- These Pascal AccoDocument144 pagesThese Pascal AccoRami SaaidiPas encore d'évaluation

- DADAMOUSSA Makhloufi PDFDocument79 pagesDADAMOUSSA Makhloufi PDFHortence SiuPas encore d'évaluation

- Correction Série3Document10 pagesCorrection Série3Mohamed FizaziPas encore d'évaluation

- Xor PDFDocument5 pagesXor PDFYoussef RagraguiPas encore d'évaluation

- Agreg Int Sii 2 2022Document51 pagesAgreg Int Sii 2 2022claretPas encore d'évaluation