Académique Documents

Professionnel Documents

Culture Documents

TD2 SMP6 en 2021 2022

TD2 SMP6 en 2021 2022

Transféré par

Karim BenallouchTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TD2 SMP6 en 2021 2022

TD2 SMP6 en 2021 2022

Transféré par

Karim BenallouchDroits d'auteur :

Formats disponibles

Université Mohammed V Faculté des Sciences

Rabat Rabat

TD2- Circuits Combinatoires -1-

Filière SMP6 – P1 : IEA

M33 : ELECTRONIQUE NUMERIQUE

Demi-Soustracteur et Soustracteur Complet

On veut réaliser la soustraction D de 2 nombres A et B codés en binaires naturel sur n bits tels que :

𝑨 = (𝒂𝒏−𝟏 … 𝒂𝒊 … 𝒂𝟎 )𝟐 ; 𝑩 = (𝒃𝒏−𝟏 … 𝒃𝒊 … 𝒃𝟎 )𝟐 ; 𝑫 = (𝒅𝒏−𝟏 … 𝒅𝒊 … 𝒅𝟎 )𝟐 ;

𝒂𝒏−𝟏 , 𝒃𝒏−𝟏 𝑒𝑡 𝒅𝒏−𝟏 étant les bits de poids fort.

I. Demi-soustracteur (𝑯𝒂𝒍𝒇 𝑺𝒖𝒃𝒔𝒕𝒓𝒂𝒄𝒕𝒐𝒓)

On appelle 𝒅𝒊 et 𝒓𝒊 respectivement le résultat et la retenue sortante de la HS

soustraction de 2 bits 𝒂𝒊 et 𝒃𝒊 indépendamment de la retenue 𝒓𝒊−𝟏 de la

soustraction des 2 bits précédents :

1. Etablir la table de vérité de ce circuit.

2. Donner les équations logiques de 𝒅𝒊 et de 𝒓𝒊 en fonction de 𝒂𝒊 , 𝒃𝒊 .

3. En déduire le logigramme de ce HS.

II. Soustracteur complet (𝑭𝒖𝒍𝒍 𝑺𝒖𝒃𝒔𝒕𝒓𝒂𝒄𝒕𝒐𝒓)

Pour généraliser cette structure afin de décrire la soustraction de

nombres de taille supérieure à 1, il faut introduire une variable supplémentaire

𝒓𝒊−𝟏 qui représente une retenue entrante :

FS

1. Etablir la table de vérité de ce circuit. -1

2. Etablir les équations logiques complètes de 𝒅𝒊 et de 𝒓𝒊 en

fonction de 𝒂𝒊 , 𝒃𝒊 et 𝒓𝒊−𝟏 à partir de la table de vérité.

3. En déduire le logigramme de ce circuit (FS) en intervenant 2 demi-soustracteurs.

4. Réaliser un soustracteur de deux mots de 2 bits : 𝑨 = (𝒂𝟏 𝒂𝟎 )𝟐 𝑒𝑡 𝑩 = (𝒃𝟏 𝒃𝟎 )𝟐 .

Comparateur 1 bit - n bits

On souhaite réaliser un comparateur de deux mots de n bits : A = (an… ai…a1)2 et B = (bn… bi…b1)2.

1. Donner le schéma bloc et décrire le fonctionnement de ce comparateur.

2. Dans un premier temps, on souhaite réaliser un comparateur élémentaire de 1

bit (n = 1).

a. Etablir les équations des sorties Si, Ii, et Ei en fonction des entrées ai,

bi et une éventuelle entrée de validation Vi. Comp.

b. Dessiner le schéma de ce comparateur élémentaire à partir des

opérateurs élémentaires (Not, AND, OR).

3. On souhaite maintenant étendre l'amplitude du comparateur à deux mots de 2 bits.

a. Etabli les équations de S2, I2, et E2 en fonction des bits a2, b2, S1, E1 et I1.

b. Déduire le rôle de l’entrée de validation Vi et donner son expression.

c. Concevoir le schéma de ce comparateur en associant des comparateurs élémentaires et un

minimum de portes logiques.

d. Etablir les relations de récurrence ci-dessous :

Sn = f(Sn-1, Vn-1, an, bn); In = g(In-1, Vn-1, an, bn); En = h(En-1, Vn-1)

Pr. A. AMARI | Année Univ. 2021-2022 1

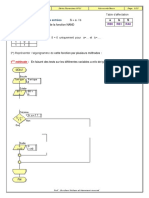

Transcodeur BCD / XS 3

On désire réaliser un transcodage du code BCD vers le code à excès de trois. Les nombres d’entrée et

de sortie sont exprimés sur 4 bits (E = E3 E2 E1 E0 et S = S3 S2 S1 S0), et ce transcodeur pourra convertir tous les

chiffres de 0 à 9 :

E0 (LSB) S0 (LSB)

E1 Transcodeur S1

E2 BCD / XS3 S2

E3 (MSB) S3 (MSB)

1. Dresser la table de vérité de ce transcodeur.

2. Donner les expressions logiques simplifiées des sorties S3, S2, S1 et S0 en fonction des entrées E3 , E2 ,

E1 et E0 de ce transcodeur.

3. Dessiner le logigramme de ce transcodeur.

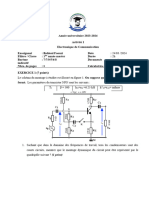

Multiplexeur (Extrait d’examen d’EN, A.U. 2017-18)

A l’aide des circuits multiplexeurs et une porte NON, on souhaite générer la fonction logique

représenté par le schéma de la figure 1.

0 E0 Mux S1

2 vers 1

1 E1 a

0

1 E0 Mux S2

2 vers 1

0 E1 a

0

0 E0 a1 a0

B

E1

Mux

S

0 E2 4 vers 1

C E3

Figure 1

1. Donner les équations de S1 et S2.

2. Déduire l’équation de sortie S en fonction de A, B et C.

3. Réaliser la fonction S à l’aide d’un seul Mux à 3 entrées d’adresses.

Pr. A. AMARI | Année Univ. 2021-2022 2

Vous aimerez peut-être aussi

- TD ArchitectureDocument2 pagesTD ArchitectureYassine EdahbiPas encore d'évaluation

- TP LcsDocument10 pagesTP LcsBelarbi Issam100% (2)

- TD2-EN-Elements de Reponse, Seance 7 (Ex3+Ex4)Document3 pagesTD2-EN-Elements de Reponse, Seance 7 (Ex3+Ex4)Karim BenallouchPas encore d'évaluation

- AB Cours Automatisme Chap 2 Et 3Document17 pagesAB Cours Automatisme Chap 2 Et 3MhB SaAdPas encore d'évaluation

- TD3 en 2019 2020Document2 pagesTD3 en 2019 2020Mahdi LahdiliPas encore d'évaluation

- Serie de TD N03Document1 pageSerie de TD N03Yasser Safar BattiPas encore d'évaluation

- Devoir 4 InfoDocument2 pagesDevoir 4 InfosaraPas encore d'évaluation

- Électronique NumeriqueDocument152 pagesÉlectronique NumeriqueSîdïMôhâmèdBënPas encore d'évaluation

- Serie 03Document3 pagesSerie 03hadjaissa fekharPas encore d'évaluation

- Codeur DecodeurDocument7 pagesCodeur DecodeurAntonio SabaPas encore d'évaluation

- Ado 1ap 21-22 TD4Document2 pagesAdo 1ap 21-22 TD4Hamza BoutlihPas encore d'évaluation

- T. D Sur Les Systemes de Numeration Et LDocument11 pagesT. D Sur Les Systemes de Numeration Et LJeanFrancoisAtemengueEbangaPas encore d'évaluation

- Architecture Des Ordinateurs TD1 - Portes Logiques Et Premiers CircuitsDocument13 pagesArchitecture Des Ordinateurs TD1 - Portes Logiques Et Premiers Circuitswafa wafaPas encore d'évaluation

- TD N°4 Circuits ArithmétiquesDocument2 pagesTD N°4 Circuits ArithmétiquesDhafer MezghaniPas encore d'évaluation

- TP1-Logique ElectroniqueDocument2 pagesTP1-Logique ElectroniqueGlade Goma YvesPas encore d'évaluation

- Circuit NumeriqueDocument1 pageCircuit NumeriqueAlain GeoffroyPas encore d'évaluation

- Examen1 2021 2022 GE3Document1 pageExamen1 2021 2022 GE3Youssef RagraguiPas encore d'évaluation

- TD3-En-Elements de Reponse, Seance 8 (Ex1+Ex2), Amari AzizDocument6 pagesTD3-En-Elements de Reponse, Seance 8 (Ex1+Ex2), Amari AzizMahdi LahdiliPas encore d'évaluation

- 2019 2020 Rattrapage - SMI3Document4 pages2019 2020 Rattrapage - SMI3FadelPas encore d'évaluation

- TDlogiqueDocument3 pagesTDlogiqueben boubakerPas encore d'évaluation

- Revision Generale D Electronique PDFDocument34 pagesRevision Generale D Electronique PDFHamzaStahiPas encore d'évaluation

- BTS BLANC N°1 Num SEI 2 - ITES + CorDocument5 pagesBTS BLANC N°1 Num SEI 2 - ITES + Corchrist sai100% (1)

- CCCCCDocument7 pagesCCCCCanicetmouoka3Pas encore d'évaluation

- TD CodeurDocument4 pagesTD CodeurMüheb BoudhraaPas encore d'évaluation

- Travaux Pratiques Electronique NumériqueDocument10 pagesTravaux Pratiques Electronique NumériqueOumaima RhayaPas encore d'évaluation

- Les TranscodeursDocument4 pagesLes Transcodeursmatch procPas encore d'évaluation

- TD6 - Additionneur Comparateur DecodeurDocument2 pagesTD6 - Additionneur Comparateur DecodeurPhantom Tonton100% (1)

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble Puteur100% (1)

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble PuteurPas encore d'évaluation

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble Puteur100% (1)

- TD 3.logique Combinatoire - BéjaiaDocument4 pagesTD 3.logique Combinatoire - BéjaiabigPas encore d'évaluation

- TD1 2Document2 pagesTD1 2Nidal Laatab100% (1)

- Les TranscodeursDocument4 pagesLes TranscodeursZaid LbachiriPas encore d'évaluation

- TD2 Motorisation - Logique CombinatoireDocument18 pagesTD2 Motorisation - Logique Combinatoirekira lilithPas encore d'évaluation

- Lectronique Umerique: Ravaux RatiquesDocument24 pagesLectronique Umerique: Ravaux Ratiquesعبير نجداويPas encore d'évaluation

- Circuits IntegrésDocument50 pagesCircuits Integrésyoussefnaire123Pas encore d'évaluation

- TD3-EN-Elements de Reponse, Seance 9 (Ex3+Ex4), Amari AzizDocument3 pagesTD3-EN-Elements de Reponse, Seance 9 (Ex3+Ex4), Amari AzizMahdi Lahdili100% (1)

- Architecture Et Technologie Des Ordinateurs - 6 - Mémoires Mortes Et Logique ProgrammableDocument12 pagesArchitecture Et Technologie Des Ordinateurs - 6 - Mémoires Mortes Et Logique ProgrammableGuillaume LauresPas encore d'évaluation

- Correction Des TD 3 Decodage Et Multuplixage (SMP S6)Document21 pagesCorrection Des TD 3 Decodage Et Multuplixage (SMP S6)RABAB MASDOURPas encore d'évaluation

- GEII ElecNum TDDocument20 pagesGEII ElecNum TDMohamed Zarboubi100% (1)

- TD Systeme ElectroniqueDocument9 pagesTD Systeme ElectroniquePëgüÿ CräqüäntPas encore d'évaluation

- TP 1 AoDocument2 pagesTP 1 AoKhaoula AtfaouiPas encore d'évaluation

- Cours - S1 - EI - LogiqueCombinatoire - Chapitre IIIDocument10 pagesCours - S1 - EI - LogiqueCombinatoire - Chapitre IIIoudjouadjPas encore d'évaluation

- Logique CombinatoireDocument11 pagesLogique CombinatoireNejib JallouliPas encore d'évaluation

- PT 2019-2020 27-03-2020 Devoir Surveille #6Document10 pagesPT 2019-2020 27-03-2020 Devoir Surveille #6YvesPas encore d'évaluation

- Geii 1a Logique TP 4Document3 pagesGeii 1a Logique TP 4Thibaud BouzyPas encore d'évaluation

- Examen 2017Document9 pagesExamen 2017asma.rahmouniPas encore d'évaluation

- Devoir de Synthèse N°3 - Sciences Physiques - 3ème Informatique (2013-2014) MR Krid MohsenDocument4 pagesDevoir de Synthèse N°3 - Sciences Physiques - 3ème Informatique (2013-2014) MR Krid MohsenLotfi BoucharebPas encore d'évaluation

- Devoir 5 SMDocument3 pagesDevoir 5 SMklunxPas encore d'évaluation

- Electronique Numérique - Cours - Chapitre (20 - 21) 4Document25 pagesElectronique Numérique - Cours - Chapitre (20 - 21) 4ziadbensalimPas encore d'évaluation

- Examen1 2019 2020 GE3Document1 pageExamen1 2019 2020 GE3Youssef RagraguiPas encore d'évaluation

- Pf3 Circuits Anal Et NumDocument4 pagesPf3 Circuits Anal Et Numdupont lavoisier100% (5)

- Fractionné 20231214 2147Document27 pagesFractionné 20231214 2147Black BleachPas encore d'évaluation

- Activit 2Document5 pagesActivit 2mwinkeudelrioPas encore d'évaluation

- Electronique 03Document5 pagesElectronique 03modeste nguimbouPas encore d'évaluation

- TD2 Gim2 Geii219 20Document3 pagesTD2 Gim2 Geii219 20Hàmža Ait BoulhcenPas encore d'évaluation

- TD Eci Master Meca2Document4 pagesTD Eci Master Meca2ElnBEKKARYPas encore d'évaluation

- TD3 enDocument2 pagesTD3 enIkram ElaimaPas encore d'évaluation

- Upload - Série D'exercices N°11-3tech-Microcontrôleur-2013-2014Document15 pagesUpload - Série D'exercices N°11-3tech-Microcontrôleur-2013-2014Moktada LouziPas encore d'évaluation

- Classification EnsiasDocument39 pagesClassification Ensiasrida4bouPas encore d'évaluation

- HTTP ProxiesDocument24 pagesHTTP ProxiesAn LamPas encore d'évaluation

- Un Modèle D'apprentissage À Distance Basé Sur Le Partage Des ConnaissancesDocument17 pagesUn Modèle D'apprentissage À Distance Basé Sur Le Partage Des ConnaissancesAïcha TarichenPas encore d'évaluation

- Conte RenduDocument15 pagesConte Renduayoub eljadidPas encore d'évaluation

- Partie Chapitre2 Automatisme&API CSE2Document5 pagesPartie Chapitre2 Automatisme&API CSE2jawaher zemezmiPas encore d'évaluation

- Rakotomalalaba Ges m1 06Document117 pagesRakotomalalaba Ges m1 06Djou ManaPas encore d'évaluation

- Iec 61000-6-8-2020Document68 pagesIec 61000-6-8-2020Gabriel Zenarosa LacsamanaPas encore d'évaluation

- Fable Du BoulangerDocument22 pagesFable Du BoulangeryounesPas encore d'évaluation

- Correction TD5: Remarque: Chaque Classe Et Chaque Interface Est Un Fichier SéparéDocument4 pagesCorrection TD5: Remarque: Chaque Classe Et Chaque Interface Est Un Fichier SéparéRihab BEN LAMINEPas encore d'évaluation

- Chapitre6 FrontPageDocument10 pagesChapitre6 FrontPageabdou adelPas encore d'évaluation

- 8 AboubouDocument5 pages8 AboubouSediki ZakariaPas encore d'évaluation

- Formation Python 3Document73 pagesFormation Python 3bwajihPas encore d'évaluation

- Mémoire Tanoh Y.P - Licence ProDocument38 pagesMémoire Tanoh Y.P - Licence ProDepanama Francky100% (1)

- Circuit Touristique Culturel PDFDocument6 pagesCircuit Touristique Culturel PDFSantatra RakotoharimalalaPas encore d'évaluation

- Gradateurs PDFDocument16 pagesGradateurs PDFHalim TlemçaniPas encore d'évaluation

- Chapitre 2Document7 pagesChapitre 2ahmed garrachPas encore d'évaluation

- Telecharger Inuit Les Peuples Du Froid PDF Par Georges Hebert Germain Tout142Document3 pagesTelecharger Inuit Les Peuples Du Froid PDF Par Georges Hebert Germain Tout142Tigosse BerrakiPas encore d'évaluation

- DomotiqueDocument54 pagesDomotiquechantalbiyeme01Pas encore d'évaluation

- Spectrophotometre À Absorption À Flamme VFDocument2 pagesSpectrophotometre À Absorption À Flamme VFmadihaPas encore d'évaluation

- Micromania ChristopheDocument1 pageMicromania ChristopheNeyRoxPas encore d'évaluation

- Ip - STT Puericulture Terminale Esf Lecon 1 Puericulture Version PapierDocument23 pagesIp - STT Puericulture Terminale Esf Lecon 1 Puericulture Version PapierSamuel the psalmistPas encore d'évaluation

- Semestre S8!4!15Document12 pagesSemestre S8!4!15Francisco PachonPas encore d'évaluation

- Du Cercle À L'hyperbole: La Trigonométrie HyperboliqueDocument15 pagesDu Cercle À L'hyperbole: La Trigonométrie HyperboliquekzeipiPas encore d'évaluation

- IEC 60092-301-1980 Amd2-1995 ScanDocument4 pagesIEC 60092-301-1980 Amd2-1995 ScanAndres ArizaPas encore d'évaluation

- 5 MDX OLAP 2010 4pDocument17 pages5 MDX OLAP 2010 4pMohamed Beji100% (1)

- CTi Service TipsDocument32 pagesCTi Service TipsMario Raul Gonzalez TerrazaPas encore d'évaluation

- Ups Technology - Upson-Ii 1000-3000-1Document2 pagesUps Technology - Upson-Ii 1000-3000-1alain1tianaPas encore d'évaluation

- Finale E1 Juin 2013Document141 pagesFinale E1 Juin 2013mohhizbar50% (2)

- TP4 InformatiqueDocument5 pagesTP4 Informatiquesalim LezhariPas encore d'évaluation

- DS Révision 3STIDocument3 pagesDS Révision 3STIPROF PROFPas encore d'évaluation