Académique Documents

Professionnel Documents

Culture Documents

La Logique Séquentielle

La Logique Séquentielle

Transféré par

malikCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

La Logique Séquentielle

La Logique Séquentielle

Transféré par

malikDroits d'auteur :

Formats disponibles

La logique squentielle

Logseq

1) Diffrence entre systmes combinatoires et systmes squentiels.

Un systme combinatoire est tel que l'tat de ses sorties ne dpende que de l'tat des entres. Il

peut donc tre reprsent par une table de vrit ou un tableau de Karnaugh, pour chaque sortie.

Il est donc possible d'crire l'quation logique de chaque sortie, en fonction seulement des

entres.

Un systme squentiel dpend non seulement des entres, mais aussi des tats prcdents du

systme (notion de squence et d'tapes). On retrouvera les mmes tats des entres plusieurs

tapes, alors que les sorties seront diffrentes. Il est donc impossible de reprsenter un tableau

de Karnaugh (car il y aurait plusieurs tats possibles dans une mme case (fonction mmoire)).

2) Sommaire des fonctions principales en logique squentielle.

Les oprateurs de base sont les bascules, et donnent naissance de nombreux dispositifs composs

par association des bascules de base (ex: registres dcalage, compteurs...).

Les bascules (Chapitre 3):

Les bascules RS ( 0 ou 1 prioritaire) et la bascule R .S .

Les bascules D (le verrou ou D latch, et la bascule D dclenche sur front edge triggered).

Les bascules JK(JK positive edge triggered, JK negative edge triggered, JK matre esclave, et

JK data lock-out).

Les fonctions complexes ralises par association de bascules (Chapitre 4).

Les compteurs, dcompteurs et diviseurs (synchrones ou asynchrones) modulo N=2n.

(comportant N tapes. Compteurs binaires n bits, ex: compteur binaire 8 bits= compteur

modulo 256, soit 256 tapes de 0 255).

Les compteurs, dcompteurs et diviseurs (synchrones ou asynchrones) modulo M (M ne

correspondant pas une puissance de 2).(C'est le cas des compteurs BCD = dcimal cod en

binaire ou M=10, soit 10 tapes de 0 9).

Les registres dcalage.

Les compteurs particuliers construits partir des registres dcalage (ex: compteurs en

anneau, compteurs Johnson, gnrateurs de squence pseudo-alatoire...).

3) Les bascules.

Les bascules sont des lments squentiels simples qui ralisent une fonction de mmorisation. Leur

intrt rside principalement dans leur utilisation pour raliser des systmes complexes.

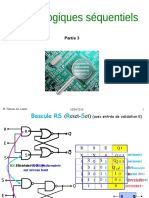

3-1) La bascule RS asynchrone appele verrou de type RS.

C'est la bascule de base qui sert fabriquer les autres. S vient de l'anglais "to Set" (mettre 1), et

R= "to Reset" (mettre 0).

LOGSEQ

Logique squentielle. Page: 1

>1

Q*

>1

S

0

0

1

1

R

0

1

0

1

Q

Qp

0

1

0

Q*

Qp

1

0

0

Qp=Q prcdent

(avant que S=R=0)

Etat mmoire

Etat interdit

(0 prioritaire)

Bascule RS (NOR)

Q

&

&

R

&

Q*

&

S

0

0

1

1

R

0

1

0

1

Q

Qp

0

1

1

Q*

Qp

1

0

1

Etat mmoire

Etat interdit

Bascule RS (NAND) (1 prioritaire)

Le fonctionnement est identique sauf pour la combinaison R=S=1 (demande de mise 1 et de

remise zro simultane). Cet tat n'est en principe pas utilis, et est souvent appel tat interdit

(ou combinaison interdite). Toutefois dans des cas rares, il faut l'envisager. Ex: automatisme de

mise en marche et d'arrt pour une machine outil. La scurit des personnes impose d'utiliser des

bascules RS 0 prioritaire (RS NOR, ex circuit CMOS CD4043), ainsi en cas d'accident, l'appui sur

les boutons marche et arrt provoque l'arrt.

Remarque: Certains dispositifs de scurit imposent le contraire, c'est le cas de systmes d'alarme

ou de dispositifs anti-explosion ou anti-incendie. Alors l'appui simultan sur marche et arrt doit

entraner la marche. On utilisera alors un verrou RS de type NAND.

Attention: Le verrou de type NAND est souvent constitu de seulement 2 portes NAND, les

entres sont alors active l'tat bas (parfois appel bascule R S ).

Q

&

&

Q*

S

0

0

1

1

Q

1

1

0 0

1 Qp

R

0

1

Q*

1

0

1

Qp

Etat interdit

(1 prioritaire)

Etat mmoire

Bascule RS

Important: Si l'tat appel interdit n'est pas utilis, la sortie Q* correspond Q .

Application: La bascule RS est souvent utilise associe des boutons poussoirs, afin d'viter les

problmes de rebonds (anti-rebonds). Elle permet la mise en marche et l'arrt d'un dispositif par des

actions fugitives, l'tat mmoire permet de maintenir la marche ou l'arrt alors qu'il n'y a plus de

boutons actionns (ou de signaux de commande actifs).

LOGSEQ

Logique squentielle. Page: 2

Symbole de la bascule RS

Application (l'anti rebonds)

+Vcc

Q

Q

R1

gnd

Vers

utilisation

R2

3-2) Les bascules synchrones dclenches par niveaux (D latch). Une entre de commande

appele C (H ou LE = latch enable) permet le fonctionnement de la bascule. A l'tat inactif, les

sorties de la bascule sont figes (tat mmoire). Ce mode de fonctionnement n'est utilis que dans

les bascules D latch (verrous de type D).

Verrous de type D (D latch)

Q

D

1D

C

C1

Q

Si C=1 le verrou est dit

transparent Q=D

Si C=0 le verrou est l'tat

de mmoi re. Q=Qp

3-3) Les bascules synchrones dclenches par fronts D ou JK (edge triggered). Les

modifications en sortie ne peuvent s'effectuer qu'aux moments des fronts de l'horloge (montants ou

descendants). La dtection du front se fait au passage une tension donne (1,3V en TTL Std). Les

fronts doivent tre suffisamment raides. Les entres prises en compte sont celles qui existent au

moment du front. Elles doivent alors tre stables (voir paramtres dynamiques des bascules, tsu et

th).

D (edge triggered)

Q

1D

C1

ou

D flip-flops

JK

1J

C1

1K

positive

edge triggered

Q

Q

1J

C1

1K

Q

Q

negative

edge triggered

S

Q

1J

C1

Q

1K

R

avec Preset

et Clear

Remarque: Pour le fonctionnement, voir le tableau rcapitulatif.

3-4) Les bascules matre-esclave (Master-Slave). Elles sont constitues de deux parties appeles

matre et esclave. Le fonctionnement se fait en deux temps.

1) Lorsque C=1, la bascule matre est active, la bascule esclave est bloque (les sorties sont donc

figes) mais la bascule matre suit les volutions des entres.

2) Lorsque C passe 0, il y blocage de la bascule matre (tat juste prcdent le front

descendant de C), la bascule esclave est alors transparente.

Il existe des bascules matre-esclave avec verrouillage des donnes (data lock-out). Les entres sont

prises lors d'un front montant de l'entre d'horloge, les sorties changent sur le front descendant.

LOGSEQ

Logique squentielle. Page: 3

3-5) Remarques: Les bascules D et JK possdent souvent 2 entres supplmentaires d'initialisation.

Une de remise 0 (Reset = R ou Clear = Clr) et une de mise 1 (Set = S ou Preset = Pre). Ces

entres sont asynchrones par rapport l'horloge.

Les verrous de type D sont souvent avec sortie 3 tats. Dans ce cas une entre de commande

(Enable = E ou Output control = OC) permet la mise en haute ou basse impdance de la sortie.

3-6) Paramtres dynamiques des bascules. Les temps de propagations sont dfinis entre la sortie

et l'entre qui a provoqu la transition. Ainsi pour une bascule D edge triggered comportant des

entres d'initialisations (S et R), il faut dfinir diffrents temps:

Temps de propagation par rapport l'horloge: tpHL(H to Q) et tpLH(H to Q).

Temps de propagation par rapport aux entres d'initialisation: tpLH(S to Q) par rapport

S et tpHL(R to Q) avec l'entre R.

Temps d'tablissement et temps de maintien: Il faut de plus que les entres soit stables

pendant la transition active de l'horloge. On appelle temps d'tablissement ou temps de

prpositionnement (set up time = tsu) la dure minimale pendant laquelle les entres doivent tre

stables avant le front actif de l'horloge, pour pouvoir tre prises en compte. De mme on appelle

temps de maintien (hold time = th) la dure minimale pendant laquelle les donnes doivent tre

maintenues aprs le front actif de l'horloge. L'un de ces temps peut tre positifs, nuls ou mme

ngatif. Ex: si tsu = 15nS et que th = -5nS, il est alors possible de modifier les donnes juste

avant le front actif de l'horloge, sans qu'il y ait d'erreur sur la valeur prise en compte (Rem: les

temps tsu et th peuvent tre diffrents pour les niveaux "1" et "0").

Temps de propagation pour les sorties 3 tats: Pour les lments dont la sortie peut tre mise

en haute impdance, il est important de dfinir les temps de propagation entre la sortie et l'entre

de commande. Ex: tpLZ(OC to Q) indique le temps entre la commande (OC) et la sortie (Q)

pour que Q passe de "0" l'tat "Z". On trouvera donc de mme: tpHZ, tpZL et tpZH.

1,3V en TTL Std

OC

EN

C1

1D

t

tsu

th

OC

t

0,5v

Voh

Z

t

tplh

(S to Q)

tphl

(H to Q)

tpzl

tphz

tplh

(OC

to

Q)

(H to Q)

Important: Afin de simplifier la reprsentation des chronogrammes, on ne reprsentera les temps

de monte et de descente que dans les cas indispensables. Dans les autres cas, les fronts seront

reprsents verticaux. Le seuil (1,3V pour les TTL) ne sera donc pas reprsent. Les temps de

LOGSEQ

Logique squentielle. Page: 4

propagation apparaissent alors comme de simples retards.

Reprsentation simplifie des temps de propagation

On ne fait pas

apparatre les

temps de monte

et de descente

Q

t

tphl

tplh

3-7) Synthse des systmes squentiels, tables de transition des bascules. Les mthodes de

synthse permettent d'crire les quations logiques des entres d'une bascule partir de sa table de

transition.

Tables de transition des bascules RS D et JK

t 00

t 10

01

t 11

SR

0 --

t 01

10

t 00

0

t 01

1

t 10

0

t 11

1

JK

t 00

0 --

t 01

1 --

t 10

-- 1

t 11

-- 0

Bascule RS

Bascule D

Bascule JK

-- 0

t XY dsigne une

transition de la sortie

de l'tat initial X

l'tat final Y

ex: t 01 pour la JK

correspond un passage

de 0 1.

il faut alors J=1

K est indiffrent (--)

Les tables de transition permettront de dterminer, partir d'une transition souhaite en sortie,

quels sont les tats logiques devant tre prsents sur les entres (avant le front actif de l'horloge

pour les bascules synchrones). L'tude se rapproche alors de celle des systmes combinatoires (voir:

mthode d'Huffman).

Explication des tables:

Dans l'exemple de la JK, si l'on dsire obtenir la transition t 00 (Q est 0 et doit le rester aprs le

front d'horloge), la table donne J=0 et K indiffrent.

Vrifions pour les deux valeurs de K:

Si J=0 et K=0, nous sommes dans le cas mmoire, la sortie restera donc 0.

Si J=0 mais K=1, il y a forage 0 de la sortie (position Reset de la sortie).

Intrt de la JK par rapport aux autres bascules: pour la JK toutes les transitions permettent de

n'imposer qu'une seule des deux entres (indtermination = choix possible), Les solutions seront

donc souvent plus simples l'aide de bascules JK.

LOGSEQ

Logique squentielle. Page: 5

4) Les fonctions complexes ralises par association de bascules (Chapitre 4).

4-1) Les compteurs, dcompteurs et diviseurs (synchrones ou asynchrones) modulo N=2n.

(comportant N tapes. Compteurs binaires n bits, ex: compteur binaire 8 bits= compteur modulo

256, soit 256 tapes de 0 255).

- On obtient des compteurs si la sortie de rang n (Qn ) de la nime bascule volue sur les

fronts descendants de la sortie prcdente (Qn-1).

- On obtient des dcompteurs si la sortie de rang n (Qn ) de la nime bascule volue sur les

fronts montants de la sortie prcdente (Qn-1).

Attention: Ne pas confondre avec l'volution sur fronts montants ou descendants de

Chronogrammes:

Compteur binaire 4 bits, dclench sur fronts montants de H

H

A

t

B

t

C

t

Compteur

D

t

N

A B

E F

Dcompteur binaire 4 bits, dclench sur fronts montants de H

H

A

t

B

t

C

t

Dcompteur

D

t

N F

Remarque: On constate sur les chronogrammes des compteurs et des dcompteurs qu'il n'y a

qu'une inversion (complmentation) de chaque signal de sortie (A, B, C, D).

LOGSEQ

Logique squentielle. Page: 6

a) Les compteurs et dcompteurs asynchrones. Ils utilisent le principe des diviseurs de

frquence par 2, monts en cascade ( l'aide de bascules D [D reli Q ] ou de JK avec J=K=1).

A l'aide de bascules D.

Compteur asynchrone

dcompteur asynchrone

A l'aide de bascules JK. (Ex: compteur asynchrone 4 bits, dclench sur les fronts

montants de l'horloge).

Compteur asynchrone JK

Inconvnients des (d)compteurs asynchrones. (Prsence d'tats indsirables, et lenteur).

Les inconvnients proviennent de

l'asynchronisme. L'horloge n'est

applique qu' la 1re bascule.

Ainsi, il ne peut y avoir de

transitions simultannes sur

l'ensemble des sorties. Des tats

indsirables apparaissent

pendant le temps de propagation

total de l'information de l'horloge

la dernire sortie. Ce temps de

propagation maximal correspond

n.tp (n tant le nombre de

bascules, et tp tant le temps de

propagation [tpLH ou tpHL] d'une

bascule. On ne peut donc pas

les utiliser des frquences

leves.

LOGSEQ

Dfauts des compteurs asynchrones

A

D

N

Etats indsirables

Logique squentielle. Page: 7

b) Les compteurs et dcompteurs synchrones. Ils liminent l'addition des temps de

propagation des bascules, en utilisant le mme signal d'horloge pour toutes les entres d'horloge.

Ils sont en principe raliss l'aide de bascules JK. Les entres J et K sont alors relies et

appeles report (retenue). Lorsque la retenue est active, la bascule changera d'tat au prochain

front d'horloge.

Compteur synchrone report srie. Ce type de compteur est simple raliser (Les

portes ET pour le report sont toutes 2 entres), mais il est limit en frquence par la

propagation de la retenue (Il faut attendre la stabilisation du dernier ET avant le prochain

front de l'horloge).

Compteur synchrone report srie

Compteur synchrone report parallle. C'est le plus rapide, car il suffit d'attendre la

stabilisation d'une porte ET, au lieu de plusieurs en srie. Mais il ncessite une porte ET

2 entres, 1 3 entres, et ainsi de suite suivant le nombre d'tages du compteur. En

pratique on trouve surtout des compteurs 4 tages. C'est alors l'utilisateur de cascader

plusieurs de ces compteurs en ralisant au besoin un report parallle d'un compteur

Compteur synchrone report parallle

l'autre.

4-2) Les compteurs, dcompteurs et diviseurs (synchrones ou asynchrones) modulo M (M ne

correspondant pas une puissance de 2).(C'est le cas des compteurs BCD = dcimal cod en

binaire ou M=10, soit 10 tapes de 0 9). Compteur BCD synchrone report parallle

LOGSEQ

Logique squentielle. Page: 8

Les compteurs intgrs.

On trouve sous forme de circuits intgrs, des compteurs et dcompteurs asynchrones et

synchrones. Leur squence peut tre soit binaire soit BCD. Certains offrent mme des posibilits de

prpositionnement un nombre quelconque (chargement).

Exemples de compteurs intgrs:

Compteur binaire asynchrone

12 tages

Compteur dcompteur synchrone binaire dcimal

avec chargement parallle asynchrone.

Diviseur par N programmable

(N de 2 10)

Comptage/dcomptage

Count

enable

Carry

(retenue)

U/D

CE

PL

Chargement

Binaire/

Dcimal

Horloge

Sorties

Entre de prpositionnement

Mise en cascade de compteurs.

a) Cascade asynchrone. Il suffit de remarquer que le compteur de poids suprieur doit tre

incrment sur les fronts descendants du bit de poids fort du compteur prcdent. Attention:

pour cascader des dcompteurs asynchrones il faut prendre les fronts montants.

Cascade de compteurs asynchrones

CTR/DIV16

Cascade de dcompteurs asynchrones

CTR/DIV16

CTR/DIV16

H

Q0

Q1

Q2

Q3

Q0

Q1

Q2

Q3

CTR/DIV16

H

Q0

Q1

Q2

Q3

Q0

Q1

Q2

Q3

b) Cascade synchrone. La mise en srie asynchrone est possible, mais on perd l'avantage des

compteurs synchrones. On prfre donc une association synchrone (mme horloge pour tous les

compteurs). On retrouve les deux type de report (retenue). Le report srie, et le report parallle

(voir principe, avantages et inconvnients dans le chapitre sur les compteurs synchrones).

Association synchrone, report srie

Compteurs 4029

Vdd

CE

H

Association synchrone, report parallle

Compteurs 74161

CO

CE

CO

H

Q0

Vdd

CE

Enp

CO

Q0

CO

Vdd

Ent

H

Q0

Q3

Q0

Q3

CO

Ent

H

Q3

Enp

CO

Ent

Q0

H

Q3

Enp

CO

Ent

Q0

H

Q3

Enp

Q0

H

Q3

Q3

Les compteurs 74161 disposent de 2 entres de validation de comptage

Enp et Ent permettent d'autoriser ou d'inhiber le comptage

Ent permet d'inhiber la sortie retenue en mme temps que le compteur.

Rem: Certains compteurs comportent plusieurs entres d'inhibition de comptage Enp et Ent,

permettant l'association synchrone avec report parallle.

LOGSEQ

Logique squentielle. Page: 9

4-3) Les registres dcalage.

Registre dcalage 4 bits

Registre dcalage 4 bits

H

Vin

t

A

t

B

t

C

t

D

t

Applications principales des registres dcalages: Conversions srie-parallle et parallle-srie,

calcul arithmtique dans les unit arithmtiques et logique (division ou multiplication par 2), lignes

retard numriques, mmoires circulantes accs squentiel...

4-4) Les compteurs particuliers construits partir des registres dcalage (ex: compteurs en

anneau, compteurs Johnson, gnrateurs de squence pseudo-alatoire...).

Compteur en anneau 4 bits

a) Les compteurs en anneau.

Applications des compteurs en anneau: (ex: 4017). Ils sont souvent utiliss comme squenceur

lmentaire en rapport avec les signaux qu'ils dlivrent (Voir chronogrammes page suivante).

Utiliss dans les jeux de lumire appells chenillards.

LOGSEQ

Logique squentielle. Page: 10

Compteur en anneau 4 bits

H

A

t

B

t

C

t

D

t

Compteur Johnson 4 bits

b) Les compteurs Johnson.

Compteur Johnson 4 bits

H

A

t

B

t

C

t

D

t

Applications: Ils sont surtout utiliss pour raliser des diviseurs de frquence par un nombre

quelconque (pair ou impaire). On obtient un rapport cyclique de 1/2 pour les diviseurs par un

nombre pair, alors qu'il est en principe diffrent de 1/2 pour les diviseurs par un nombre impair

(attention: si le rapport cyclique de l'horloge est exactement de 1/2, certaines structures plus

complexes permettent d'obtenir le rapport cyclique de 1/2 avec les diviseurs impairs).

LOGSEQ

Logique squentielle. Page: 11

Vous aimerez peut-être aussi

- Présentation LabviewDocument44 pagesPrésentation LabviewAla MassoudiPas encore d'évaluation

- Chap6 Les Bascules PDFDocument8 pagesChap6 Les Bascules PDFDěmøïšěllë RãnPas encore d'évaluation

- MicroprocesseurDocument24 pagesMicroprocesseurmounaPas encore d'évaluation

- Chapitre 1 - Rappel Sur Les Circuits SéquentielsDocument18 pagesChapitre 1 - Rappel Sur Les Circuits SéquentielsTtech hackPas encore d'évaluation

- Circuits Séquentiels Bascules Et CompteurDocument10 pagesCircuits Séquentiels Bascules Et Compteurhicham_barakatePas encore d'évaluation

- Ch10 CI11 I11 SequentielleDocument8 pagesCh10 CI11 I11 Sequentiellecpommier100% (1)

- Chapire I La Logique SéquentielleDocument8 pagesChapire I La Logique SéquentielleMouhamed MoustaphaPas encore d'évaluation

- Circuits Csequentiels Partie1Document36 pagesCircuits Csequentiels Partie1Nidal LaatabPas encore d'évaluation

- Logique SequentielleDocument28 pagesLogique SequentielleIkram ElaimaPas encore d'évaluation

- Chapi CIRCUITS LOGIQUES L1GInfo&GEI 2021-2022Document19 pagesChapi CIRCUITS LOGIQUES L1GInfo&GEI 2021-2022Zaza RatsiPas encore d'évaluation

- Seìquentiel 1Document100 pagesSeìquentiel 1Aicha LahnoukiPas encore d'évaluation

- Circuits SéquentielsDocument29 pagesCircuits Séquentielsmustapha skanderPas encore d'évaluation

- Chap5 Systèmes Séquentiels 2016Document11 pagesChap5 Systèmes Séquentiels 2016MOHAMED AIT HADDOUCHPas encore d'évaluation

- SéquentielDocument8 pagesSéquentielak penPas encore d'évaluation

- Logique SequentielleDocument101 pagesLogique SequentielleDjouweinannodji YvesPas encore d'évaluation

- Corrigé Du TD2: N-1barDocument3 pagesCorrigé Du TD2: N-1barELMEHDI CHOUINEPas encore d'évaluation

- Bascule SDocument15 pagesBascule SManar BouPas encore d'évaluation

- SYNTHESE DES SYSTEMES SEQUENTIELS Doc ProfDocument10 pagesSYNTHESE DES SYSTEMES SEQUENTIELS Doc ProfNejib JallouliPas encore d'évaluation

- Chap5 Systèmes Séquentiels NKHAILI Complet-1Document16 pagesChap5 Systèmes Séquentiels NKHAILI Complet-1lodyyy4Pas encore d'évaluation

- Cours Logique Sequentielle Bascules STSDocument5 pagesCours Logique Sequentielle Bascules STSezed1234Pas encore d'évaluation

- ch2 - C - Logiques Séquentiels (Complet)Document85 pagesch2 - C - Logiques Séquentiels (Complet)DønuTsPas encore d'évaluation

- Circuits Sequentiels3Document14 pagesCircuits Sequentiels3ABDERABBI RHAZLAHJORPas encore d'évaluation

- Logique-Sequentielle ESTM GE GIMDocument36 pagesLogique-Sequentielle ESTM GE GIMCrateFXPas encore d'évaluation

- Circuits Sc3a9quentiels BasculesDocument4 pagesCircuits Sc3a9quentiels BasculesJérémie DansouPas encore d'évaluation

- Les BasculesDocument5 pagesLes Basculesحنيش يوسف100% (1)

- La Dipol de Sin Et CosDocument26 pagesLa Dipol de Sin Et CosnouichimoumenPas encore d'évaluation

- Présentation Logique SequentielleDocument50 pagesPrésentation Logique SequentiellemohPas encore d'évaluation

- Document EleveDocument13 pagesDocument EleveakremibechirPas encore d'évaluation

- CM2: Circuits Séquentiels: Licence STS L1Document29 pagesCM2: Circuits Séquentiels: Licence STS L1YASSINE KERWIPas encore d'évaluation

- Log SéqDocument6 pagesLog SéqMohammed NaimiPas encore d'évaluation

- Les Circuits SéquentielsDocument14 pagesLes Circuits SéquentielsJOHNE JKPas encore d'évaluation

- Systeme Sequentiels ProfDocument8 pagesSysteme Sequentiels ProfAhmed BelhadjPas encore d'évaluation

- Chapitre 5Document9 pagesChapitre 5Mohamed CharradaPas encore d'évaluation

- Systemes Logiques Chapitre6 PDFDocument10 pagesSystemes Logiques Chapitre6 PDFGüz ElleştimePas encore d'évaluation

- Cours Les Circuits Séquentiels (Architecture Des Ordinateurs)Document34 pagesCours Les Circuits Séquentiels (Architecture Des Ordinateurs)momoPas encore d'évaluation

- Cours de Bascules Numériques 2021-22Document23 pagesCours de Bascules Numériques 2021-22Manel AsnicarPas encore d'évaluation

- Suite - Logique Séquentielle (Chapitre 6 - Chapitre 7 - Chapitre 8) - (Les Bascules - Les CompteursDocument15 pagesSuite - Logique Séquentielle (Chapitre 6 - Chapitre 7 - Chapitre 8) - (Les Bascules - Les CompteursFares ChetouhPas encore d'évaluation

- Chap 3 Les Bascules Syst Log 2Document8 pagesChap 3 Les Bascules Syst Log 2mohamed ben slimanePas encore d'évaluation

- Cours de Bascules Numériques 2017-2018Document28 pagesCours de Bascules Numériques 2017-2018Camile SiliaPas encore d'évaluation

- Chap 4 Logique Séq 2020Document14 pagesChap 4 Logique Séq 2020Ali DridiPas encore d'évaluation

- 1-Architecture Chapitre 1-4Document35 pages1-Architecture Chapitre 1-4Mounaim AaouadouPas encore d'évaluation

- Chapitre 4Document8 pagesChapitre 4rajakrifaPas encore d'évaluation

- Elecseq 1Document20 pagesElecseq 1Daniel King-zockPas encore d'évaluation

- Chap V BasculesDocument13 pagesChap V BasculesoussamamahjourPas encore d'évaluation

- EXA AutoDocument9 pagesEXA AutoTko ToolPas encore d'évaluation

- 13 BasculesDocument5 pages13 BasculesZakaria GhazizPas encore d'évaluation

- Bascule SDocument6 pagesBascule SYahya ElamraniPas encore d'évaluation

- Circuits SéquentielDocument27 pagesCircuits SéquentielasmaPas encore d'évaluation

- Bascules 1Document31 pagesBascules 1baha.jamel32Pas encore d'évaluation

- Chapitre IV 1Document64 pagesChapitre IV 1Monxef BlrPas encore d'évaluation

- CIRA1 - 3) Logique Sequentielle PDFDocument7 pagesCIRA1 - 3) Logique Sequentielle PDFLANGO RICHARD BAMBAPas encore d'évaluation

- Bascules Et Compteurs PDFDocument15 pagesBascules Et Compteurs PDFAva KevinPas encore d'évaluation

- Les Bascules BistablesDocument8 pagesLes Bascules BistablesTopina Rahim100% (1)

- Chapitre III La Logique SéquentielleDocument26 pagesChapitre III La Logique SéquentielleGaya MhbPas encore d'évaluation

- Les BasculesDocument14 pagesLes BasculesDjouweinannodji Yves100% (1)

- Papport Filtre Coupe BandeDocument6 pagesPapport Filtre Coupe BandeVictor AhadiPas encore d'évaluation

- Teleinformatique Notes de Cours 1 1 PDFDocument11 pagesTeleinformatique Notes de Cours 1 1 PDFBrahim BenhamimidPas encore d'évaluation

- Ecran Easypitch-55mn91 DirectDocument6 pagesEcran Easypitch-55mn91 DirectHoby RakotoarisoaPas encore d'évaluation

- Catalogue PC - Portables & Peripheriques Valable Jusqu'Au 31 Mars 2020Document27 pagesCatalogue PC - Portables & Peripheriques Valable Jusqu'Au 31 Mars 2020Ababacar DioufPas encore d'évaluation

- ESGI BrochureDocument5 pagesESGI BrochureAzura ComptePas encore d'évaluation

- TP1 4Document22 pagesTP1 4Abderrahmane WrPas encore d'évaluation

- Les ClassesDocument17 pagesLes ClassesLai'Fe-Ini DimbiniainaPas encore d'évaluation

- Cours IsDocument39 pagesCours IsLAGHRABI OUSSAMAPas encore d'évaluation

- Complement POO Elements de La Programmation JAVADocument68 pagesComplement POO Elements de La Programmation JAVAMOHAMED AIMEN MECHEKOURPas encore d'évaluation

- Présentation Générale. Solution de Gestion de Files D AttenteDocument22 pagesPrésentation Générale. Solution de Gestion de Files D Attenteabdel cscecPas encore d'évaluation

- Chapitre 1:: Cours RliDocument44 pagesChapitre 1:: Cours RliKamel EddinePas encore d'évaluation

- MDSD Final MCQs Combined BSSE (Reg+Self)Document96 pagesMDSD Final MCQs Combined BSSE (Reg+Self)wardaPas encore d'évaluation

- ADF5355 and Arduino - FR - GB - V1Document4 pagesADF5355 and Arduino - FR - GB - V1Carlos Guillermo VahnovanPas encore d'évaluation

- Remarques Et Astuces de Programmation en AssembleurDocument31 pagesRemarques Et Astuces de Programmation en AssembleuramaniPas encore d'évaluation

- TD RipDocument4 pagesTD RipHa Na0% (1)

- Leica GS09 UserManual FRDocument184 pagesLeica GS09 UserManual FRGogne RodolphPas encore d'évaluation

- TD N°1 Transmission NumériqueDocument2 pagesTD N°1 Transmission NumériqueGuy Kennet MankouPas encore d'évaluation

- TP N°02-Part1Document4 pagesTP N°02-Part1chaima2003poshPas encore d'évaluation

- PNE Environnement Du Poste de Travail CP2I - DONC. Octobre Windows 10. Présentation Généralités. Version Pro (Redstone)Document440 pagesPNE Environnement Du Poste de Travail CP2I - DONC. Octobre Windows 10. Présentation Généralités. Version Pro (Redstone)balamurali_aPas encore d'évaluation

- MultiplexeurDocument2 pagesMultiplexeurHouda FakhorPas encore d'évaluation

- Configuration Du BIOS 1Document14 pagesConfiguration Du BIOS 1Ahmed FayçalPas encore d'évaluation

- Structure MachineDocument2 pagesStructure MachineYoussouf KadiPas encore d'évaluation

- ITN Module 7Document31 pagesITN Module 7agrimaABDELLAHPas encore d'évaluation

- Planification Des Réseaux IdODocument13 pagesPlanification Des Réseaux IdOKoceila SALEMPas encore d'évaluation

- Maxi Travaux Pratiques Lightroom 6CC - 61 TP Pour Maîtriser Lightroom - Patrick Moll PDFDocument274 pagesMaxi Travaux Pratiques Lightroom 6CC - 61 TP Pour Maîtriser Lightroom - Patrick Moll PDFcortexaxiomePas encore d'évaluation

- TD Systemes Deust1Document4 pagesTD Systemes Deust1Tahar GFPas encore d'évaluation

- Elektor N°473 2018-09-10Document116 pagesElektor N°473 2018-09-10alex bousquetPas encore d'évaluation

- Examen DBADocument3 pagesExamen DBAnour hene67% (3)

- Memoire License Final HOTO V5Document62 pagesMemoire License Final HOTO V5Augustin AgognoPas encore d'évaluation