Académique Documents

Professionnel Documents

Culture Documents

DS Microsys 17 18

Transféré par

Sana BakhdilTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

DS Microsys 17 18

Transféré par

Sana BakhdilDroits d'auteur :

Formats disponibles

Filière : LP_IS

Module : Microsystèmes A.U : 2017 – 2018

Semestre 5

Examen final

Durée : 2h

Consigne : la correction de votre copie tiendra compte de la clarté de votre

raisonnement et de l’optimisation de l’espace lors de la conception du circuit de

l’exercice I

Questions de cours (4,5 points)

1) Donner brièvement le procédé technologique (sans faire de dessin) de la

réalisation d’une diode à jonction PN sur silicium. (2 points)

2) Comment peut-on réaliser des transistors MOSFET de type N et P sur le même

substrat ? (1 point)

3) Rappeler brièvement les étapes de conception et simulation d’un circuit CMOS sur

le logiciel ELECTRIC. (1,5 point)

Exercice I (10,5 points)

1) Réaliser par dessin technologique (sur la feuille annexe), la fonction logique

suivante :

S A B.C

Remarque : Afin de faciliter le dessin, respecter les légendes des composants et

matériaux mentionnés sur la feuille annexe

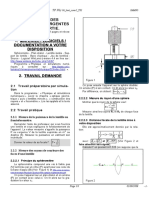

Exercice II (5 points)

Soit Le circuit ci-contre

R

- Les deux résistances R sont

identiques. D1

- Les diodes D1 et D2 sont

V U

identiques et seront

R

remplacées par leur modèles à

seuil (V0 = 0,7V)

R

- Le générateur V est variable

En faisant une étude en fonction D2

des états des diodes, tracer U en

fonction de V.

Pr Fouad DEMAMI

Vous aimerez peut-être aussi

- Annales de Mathématiques, Baccalauréat C et E, Cameroun, 2008 - 2018: Sujets et CorrigésD'EverandAnnales de Mathématiques, Baccalauréat C et E, Cameroun, 2008 - 2018: Sujets et CorrigésÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- DS Statique Mpsi 2020 PDFDocument4 pagesDS Statique Mpsi 2020 PDFCHARLIE / شارليPas encore d'évaluation

- Chapitre 2 Schemas Normes Installations ElectriquesDocument42 pagesChapitre 2 Schemas Normes Installations ElectriquesEl Hasnaoui YsfPas encore d'évaluation

- Chapitre 16 Redressement Non CommandéDocument13 pagesChapitre 16 Redressement Non CommandéLokmane Abada100% (5)

- Module 02 BureautiqueDocument130 pagesModule 02 BureautiquetehamiPas encore d'évaluation

- TD Réseaux ESIEE 11 12Document21 pagesTD Réseaux ESIEE 11 12Alloula Alae100% (2)

- TP4 CombinatoireDocument4 pagesTP4 CombinatoireNawfal Fathi El IdrissiPas encore d'évaluation

- Polycop TP Pspice14 15Document29 pagesPolycop TP Pspice14 15s3uPas encore d'évaluation

- Examen Rattrapage GE4 452 BG 2020Document1 pageExamen Rattrapage GE4 452 BG 2020Mohamed Amine ZouhriPas encore d'évaluation

- TPOL1 InitProteus TPSE1Document9 pagesTPOL1 InitProteus TPSE1Lukombo AfonsoPas encore d'évaluation

- Polycopie TP 2020 LogisimDocument31 pagesPolycopie TP 2020 LogisimMahdi LahdiliPas encore d'évaluation

- Outils de SimulationDocument14 pagesOutils de Simulationtoufik bendibPas encore d'évaluation

- Polycopie TP-2020-LogisimDocument31 pagesPolycopie TP-2020-LogisimFad FodPas encore d'évaluation

- Rapport TP) 2020Document45 pagesRapport TP) 2020KAWTAR EL AMRIPas encore d'évaluation

- Circuits Electriques Et Electroniques. Blancs 2017Document7 pagesCircuits Electriques Et Electroniques. Blancs 2017Alain GeoffroyPas encore d'évaluation

- 2met Devoir BilanDocument27 pages2met Devoir Bilanbenjaminbeneditoukila.cdPas encore d'évaluation

- TP 2020 LogisimDocument31 pagesTP 2020 LogisimbelkacemiPas encore d'évaluation

- Bts CM 2019 U41 SujetDocument8 pagesBts CM 2019 U41 SujetSmith FrankPas encore d'évaluation

- 1er Devoir Du 1er Semestre PCT 2nde D 2020-2021 Ceg SekereDocument3 pages1er Devoir Du 1er Semestre PCT 2nde D 2020-2021 Ceg SekereSanounou MomangaPas encore d'évaluation

- Contrôle Continu Sur La Modélisation Énergétique Par Bond-Graphe Et Simulation Des Systèmes Multi-PhysiquesDocument1 pageContrôle Continu Sur La Modélisation Énergétique Par Bond-Graphe Et Simulation Des Systèmes Multi-PhysiquesMohamed Amine ZouhriPas encore d'évaluation

- Exam Intro Elec 1 Ere Session 19Document1 pageExam Intro Elec 1 Ere Session 19Sadieu Guenhs Haicha SAMBAPas encore d'évaluation

- 2bep Ep1 td01Document49 pages2bep Ep1 td01zangoPas encore d'évaluation

- Book 1Document15 pagesBook 1Hossam EddinPas encore d'évaluation

- TP Circuits Hyperfréquences: Master Systèmes de TélécommunicationDocument30 pagesTP Circuits Hyperfréquences: Master Systèmes de TélécommunicationArold Serge TchikayaPas encore d'évaluation

- Installation Electrique SuiteDocument19 pagesInstallation Electrique SuiteRafils LonjiPas encore d'évaluation

- Les TPs PDFDocument15 pagesLes TPs PDFMohamed Taha MESBANEPas encore d'évaluation

- Devoir de Synthèse N°1 - Physique - 2ème Sciences (2012-2013) MR Dhaoui YOUNSIDocument3 pagesDevoir de Synthèse N°1 - Physique - 2ème Sciences (2012-2013) MR Dhaoui YOUNSIazzabi.sihemPas encore d'évaluation

- Solutionnaire Archi TD1Document5 pagesSolutionnaire Archi TD1Colmain Nassiri100% (1)

- Examen Electronique 2019Document4 pagesExamen Electronique 2019Dhafer MezghaniPas encore d'évaluation

- COURS LENTILLE 06 - Lent - Conv2 - TS1Document3 pagesCOURS LENTILLE 06 - Lent - Conv2 - TS1BernardPas encore d'évaluation

- Examens LectricitDocument52 pagesExamens LectricitChéri FaPas encore d'évaluation

- TD Resistance EquivalentesDocument4 pagesTD Resistance EquivalentesHassan GuenzaouzPas encore d'évaluation

- TP3-Inverseur CMOS PDFDocument4 pagesTP3-Inverseur CMOS PDFRottina RossyPas encore d'évaluation

- TP-02-Syst-Lin-ass S4 Auto.Document4 pagesTP-02-Syst-Lin-ass S4 Auto.Djameleddine BougrinePas encore d'évaluation

- BTS 2019 Electronique Pour ET Sujet 1Document4 pagesBTS 2019 Electronique Pour ET Sujet 1Christian BouliPas encore d'évaluation

- Veved TP RDM 3Document33 pagesVeved TP RDM 3Sana EmmanuelPas encore d'évaluation

- StandardLangageProgrammation IEC 61131-3Document80 pagesStandardLangageProgrammation IEC 61131-3gilbertbeaulieuPas encore d'évaluation

- Schema ElectriqueDocument51 pagesSchema ElectriqueMohammed RezougPas encore d'évaluation

- Devoir PCT 2nde SDocument2 pagesDevoir PCT 2nde Sbitenouwe samuel100% (1)

- 2bep Ep1 td01Document48 pages2bep Ep1 td01Sou TibonPas encore d'évaluation

- TP 1Document2 pagesTP 1hamza kharef100% (1)

- TP2 Électromoteur-LinéaireDocument3 pagesTP2 Électromoteur-LinéaireKerherve JulienPas encore d'évaluation

- TP2 EquivalenceMET-MENDocument3 pagesTP2 EquivalenceMET-MENKerherve JulienPas encore d'évaluation

- Algo TPDocument2 pagesAlgo TPhakimaPas encore d'évaluation

- Activit 2Document5 pagesActivit 2mwinkeudelrioPas encore d'évaluation

- TP EnR S3Document13 pagesTP EnR S3Sofywka SofaPas encore d'évaluation

- DS 7 964 2019-2020 31-26Document3 pagesDS 7 964 2019-2020 31-26ruffinh223Pas encore d'évaluation

- Élec TGVDocument4 pagesÉlec TGVdawoud.kenzariPas encore d'évaluation

- SysML TD2 Corrigé PDFDocument3 pagesSysML TD2 Corrigé PDFHamza Smahri100% (1)

- DS 7 428 2022-2023 86Document2 pagesDS 7 428 2022-2023 86gravelmarianne27Pas encore d'évaluation

- 2nde CD 1D2S PCT 2022-2023 CEG YAGBE SujetDocument4 pages2nde CD 1D2S PCT 2022-2023 CEG YAGBE SujetjustsdedePas encore d'évaluation

- (Elec) Elek - DeLPHI Pour Électroniciens 09-10Document5 pages(Elec) Elek - DeLPHI Pour Électroniciens 09-10Madidj_2014Pas encore d'évaluation

- Maintenance Des Systèmes informatiques-DLLDocument55 pagesMaintenance Des Systèmes informatiques-DLLScribdTranslationsPas encore d'évaluation

- Rapport de Travaux Pratiques Conception Des Circuits AnalogiquesDocument31 pagesRapport de Travaux Pratiques Conception Des Circuits AnalogiquesYacine83% (6)

- Fascicule TP Asservissement 2018Document34 pagesFascicule TP Asservissement 2018Rayen ريانPas encore d'évaluation

- Saisie Du Schéma:: Matériel NécessaireDocument18 pagesSaisie Du Schéma:: Matériel NécessaireZeineb BelaidPas encore d'évaluation

- Evaluation Certificative 2 - 7P - 2022Document2 pagesEvaluation Certificative 2 - 7P - 2022vanwolleghemPas encore d'évaluation

- TD Chap2 ElectroniqueDocument5 pagesTD Chap2 ElectroniqueWael MaatougPas encore d'évaluation

- Le Dipôle Électrique SynthèseDocument4 pagesLe Dipôle Électrique SynthèseBelliphrice Bin EphricePas encore d'évaluation

- TP 2 - Étude Du Transistor À Effet de Champ: GS DSDocument3 pagesTP 2 - Étude Du Transistor À Effet de Champ: GS DShamza kharef100% (1)

- TP3 Va Et VientDocument5 pagesTP3 Va Et VientMohamed HadjiPas encore d'évaluation

- RLClibre Exerc TS17 FRDocument6 pagesRLClibre Exerc TS17 FRMohamed El Ouahdani100% (1)

- Recti H28 PDFDocument4 pagesRecti H28 PDFJerry Rodriguez FloresPas encore d'évaluation

- 5 Electricite Base TDDocument4 pages5 Electricite Base TDtos yesPas encore d'évaluation

- (Superpartituras - Com.br) Super Mario Bros Overworld PDFDocument9 pages(Superpartituras - Com.br) Super Mario Bros Overworld PDFDeyvid NascimentoPas encore d'évaluation

- ComposantselectriqueDocument54 pagesComposantselectriqueamina sayahPas encore d'évaluation

- Philips TV CH L01.1e Ab Service Manual.14-28Document15 pagesPhilips TV CH L01.1e Ab Service Manual.14-28Enrik VillaPas encore d'évaluation

- Mesure Rapport TransformationDocument3 pagesMesure Rapport TransformationsoltaniPas encore d'évaluation

- Utilisation Du Multimetre NumeriqueDocument3 pagesUtilisation Du Multimetre NumeriqueMaxence KouessiPas encore d'évaluation

- DMvac2 PDFDocument5 pagesDMvac2 PDFPenda NiassPas encore d'évaluation

- Transmission de Données Par BluetoothDocument26 pagesTransmission de Données Par BluetoothBojane100% (1)

- GR-3 - FrançaisDocument4 pagesGR-3 - FrançaisTopcon Middle East100% (2)

- 5020-5013 MultiDocument2 pages5020-5013 Multijuan_g_2009Pas encore d'évaluation

- Electrical PresentationDocument113 pagesElectrical PresentationAymane QariohPas encore d'évaluation

- 1198d Fr-EnDocument11 pages1198d Fr-EnYvesnounounePas encore d'évaluation

- Diode 3Document19 pagesDiode 3Mariam ZbakhPas encore d'évaluation

- QCM MAchinesDocument6 pagesQCM MAchinesKarl HermèsPas encore d'évaluation

- Verres Phosphates LaserDocument9 pagesVerres Phosphates LaserCharles PautratPas encore d'évaluation

- Construisez Des Applications Autonomes Et Fiables Avec LabVIEW Real TimeDocument26 pagesConstruisez Des Applications Autonomes Et Fiables Avec LabVIEW Real TimeEL AFOUPas encore d'évaluation

- Cours LabView PDFDocument17 pagesCours LabView PDFbabo88Pas encore d'évaluation

- Cahier Des Charges Du Mini Projet Post Traitement Des Fichiers LogDocument3 pagesCahier Des Charges Du Mini Projet Post Traitement Des Fichiers LogDeicid KurosakiPas encore d'évaluation

- 6219 15573 1 SMDocument13 pages6219 15573 1 SMMEed E-tanPas encore d'évaluation

- Adapter Un Collecteur D'échappement Sport Sur Une Barchetta Climatisée.Document20 pagesAdapter Un Collecteur D'échappement Sport Sur Une Barchetta Climatisée.Rossi56Pas encore d'évaluation

- MOILAMDocument35 pagesMOILAMHoàng Duy LộcPas encore d'évaluation

- Initiation SDRDocument17 pagesInitiation SDRhaha2012Pas encore d'évaluation

- Série Oscillateur Amortie Et Non AmortieDocument5 pagesSérie Oscillateur Amortie Et Non Amortieala_1964Pas encore d'évaluation

- TP Circuits Hyperfréquences: Master Systèmes de TélécommunicationDocument30 pagesTP Circuits Hyperfréquences: Master Systèmes de TélécommunicationArold Serge TchikayaPas encore d'évaluation

- Cours EngrenagesDocument5 pagesCours EngrenagesJesuis ContentPas encore d'évaluation