Académique Documents

Professionnel Documents

Culture Documents

Circuits Analogiques - Problemes Et Corriges - p189-197

Transféré par

Sawat SiwarTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Circuits Analogiques - Problemes Et Corriges - p189-197

Transféré par

Sawat SiwarDroits d'auteur :

Formats disponibles

UNIVDOCS.

COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

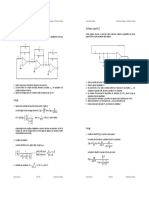

Oscillateur sinusoïdal triphasé

L’étude proposée concerne le circuit de la figure ci-dessous, utilisant des amplificateurs de tension

supposés idéaux en régime dynamique faibles signaux.

C1

10n C1

10n C1

R1 10n

R2 R1

-

R2 R1

-

R2

S1

+ -

S2

+ S3

1. Ecrivez l’expression de la fonction de transfert en boucle ouverte.

2. En boucle fermée et en régime sinusoïdal, déterminez la pulsation ωosc des oscillations et la

condition d’entretien de celles-ci.

3. Evaluez les résistances pour que le système oscille à la fréquence de 1021 Hz.

Corrigé

1. Expression de la fonction de transfert en boucle ouverte G( p ) B' ( p )

Z( p) R1

Les trois étages sont des montages inverseurs Gi ( p ) = − avec Z ( p ) =

R2 1 + R1 C1 p

3

⎛ R ⎞ 1 1

d’où G( p ) B' ( p ) = ⎜⎜ − 1 ⎟⎟ 3

avec ω0 = et B' ( p ) = 1 (retour unitaire)

⎝ R2 ⎠ ⎛ p ⎞ R1 C1

⎜⎜1 + ⎟⎟

⎝ ω 0 ⎠

relation valable car les conditions d’adaptation en tension entre blocs sont respectées. En effet, la

résistance de sortie du montage inverseur est très faible par rapport à sa résistance d’entrée

(contre-réaction tension-courant).

2. Conditions d’oscillations

La boucle étant fermée et en régime établi, G( jω )B' ( jω ) = 1 .

⎧Im[G ( jω )B' ( jω )] = 0

3

⎛ R1 ⎞ 1 ⎧⎪ω = ω0 3

⎜⎜ − ⎟⎟ =1 → ⎨ ⇒ ⎨ osc

⎝ R2 ⎠ ω2 ω ⎛⎜ ω2 ⎞ ⎩Re [G ( j ω ) B ' ( jω )] = 1 ⎪⎩R1 = 2 R2

1− 3 +j ⎜ 3 − 2 ⎟⎟

ω0

2 ω0 ⎝ ω0 ⎠

3

3. Evaluation des résistances R1 = = 27 kΩ , R 2 = 13.5 kΩ .

2π fosc C1

Sylvain Géronimi Page 188 Oscillateurs sinusoïdaux

UNIVDOCS.COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Oscillateur à pont RLC

L’étude proposée concerne le circuit de la figure ci-dessous, utilisant un amplificateur de tension

supposé idéal en régime dynamique faibles signaux.

R3

+

R L C

100n -

R1 vs

R2

1. Ecrivez la fonction de transfert B ' ( p ) en tension du réseau passif.

2. Ecrivez le gain de l’amplificateur G.

3. En boucle fermée et en régime sinusoïdal, déterminez l’expression de la pulsation ω osc des

oscillations du signal de sortie, ainsi que la condition sur les résistances.

4. La résistance R représentant les imperfections de l’inductance ( R >> R3 ), donnez le type de

comportement du bloc amplificateur.

5. Donnez la valeur de l’inductance L pour obtenir un signal de sortie à la fréquence de 16 kHz.

6. Evaluez la résistance R3 de telle manière que ζ = 0.5 pour la fonction B ' ( p ) .

7. Comment devez-vous faire varier R1 pour démarrer les oscillations ?

Corrigé

1. Fonction de transfert B ' ( p ) en tension du réseau passif

L’ensemble des éléments mis en parallèle conduit à une impédance

1 Lp Lp

Z ( p ) = R // // Lp = R // = .

Cp LCp 2 + 1 L

LCp + p + 1

2

R

La fonction de transfert en tension est fournie par le pont

L

p

Z( p) R3

B' ( p ) = =

Z ( p ) + R3 ⎛1 1 ⎞

LCp 2 + L ⎜⎜ + ⎟⎟ p + 1

⎝ R R 3 ⎠

Sylvain Géronimi Page 189 Oscillateurs sinusoïdaux

UNIVDOCS.COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

2. Gain de l’amplificateur

L’amplificateur de tension étant idéal, sa bande passante est considérée comme infinie.

R1

G( p ) = 1 + = G (amplificateur non inverseur de gain réel)

R2

3. Conditions d’oscillations

La boucle étant fermée et en régime établi, G B' ( jω ) = 1 , relation valable car les conditions

d’adaptation en tension entre blocs sont respectées. En effet, la résistance d’entrée est infinie et

résistance de sortie est nulle pour le bloc amplificateur idéal. Si l’amplificateur est réel, la contre-

réaction tension-tension conduit à des résultats voisins.

Lω ⎧ 1

⎪ωosc =

⎛ R1 ⎞ ⎧Im[G B' ( jω )] = 0 ⎪

G B' ( jω ) = ⎜⎜1 +

R3 LC

⎟⎟ =1 → ⎨ ⇒ ⎨

( )

⎝ R2 ⎠ Lω ⎛⎜ 1 + 1 ⎞⎟ + j LCω 2 − 1 ⎩Re[G B' ( jω )] = 1 ⎪1 + R1 = 1 + R3

⎜R R ⎟ ⎪⎩ R2 R

⎝ 3 ⎠

4. Comportement du bloc amplificateur

R1

Puisque R >> R3 → G = 1 + ≅ 1.

R2

L’amplificateur se comporte comme un suiveur de tension ( R 2 >> R1 ).

5. Evaluation de l’inductance

1

L= ≅ 0.99 mH

(2π fosc )2 C

6. Evaluation de la résistance R3

L

p

R3 2ζ 1 L

Pour R >> R3 , B' ( p ) ≅ . La relation nécessaire = = est obtenue en

LCp 2 +

L

p +1

ω n Q ω n R 3

R3

identifiant à la forme canonique du filtre passe-bande du second ordre, d’où R3 ≅ 99.5 Ω .

7. Démarrage des oscillations

R1

Il faut établir la condition G B' ( p ) > 1 avec G = 1 + = 1 + ε , c’est-à-dire donner à la résistance

R2

R1 une valeur relativement plus élevée que la valeur nominale, puis diminuer cette valeur jusqu’à

l’obtention du régime sinusoïdal établi.

Ce montage est utilisé pour détecter la présence de matériaux magnétiques ou amagnétiques.

Sylvain Géronimi Page 190 Oscillateurs sinusoïdaux

UNIVDOCS.COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Oscillateur à pont RLC avec potentiomètre

L’étude proposée concerne le circuit de la figure ci-dessous, utilisant un amplificateur de tension

supposé idéal en régime dynamique faibles signaux.

R2

100k

R1

-

5k

+

(1-α)R

R

αR 10k

C L

10n 10mH

Etude du régime dynamique (faibles signaux)

1. Ecrivez les fonctions de transfert en tension du réseau passif B' ( p ) et de l’amplificateur G.

2. Ecrivez les conditions d’oscillation.

3. Calculez la fréquence des oscillations et la position α du potentiomètre pour laquelle le circuit

oscille.

Corrigé

1. Fonction de transfert B' ( p ) en tension du réseau passif

L’ensemble des éléments mis en parallèle conduit à une impédance

1 Lp Lp

Z ( p ) = α R // // Lp = α R // = .

Cp LCp 2 + 1 L

LCp 2 + p +1

αR

La fonction de transfert en tension est fournie par le pont

L

p

B' ( p ) =

Z( p)

=

(1 − α )R

Z ( p ) + (1 − α )R L

LCp 2 + p +1

α (1 − α )R

L’amplificateur de tension étant idéal, sa bande passante est considérée comme infinie.

R2

G( p ) = 1 + = G (amplificateur non inverseur de gain réel)

R1

Sylvain Géronimi Page 191 Oscillateurs sinusoïdaux

UNIVDOCS.COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

2. Conditions d’oscillations

La boucle étant fermée et en régime établi, G B' ( jω ) = 1 , relation valable car les conditions

d’adaptation en tension entre blocs sont respectées. En effet, la résistance d’entrée est infinie et

résistance de sortie est nulle pour le bloc amplificateur idéal. Si l’amplificateur est réel, la contre-

réaction tension-tension amène à des résultats voisins.

Lω ⎧LCω 2 − 1 = 0

⎛ R ⎞ (1 − α )R ⎧Im[G B' ( jω )] = 0 ⎪

G B' ( jω ) = ⎜⎜1 + 2 ⎟⎟ =1 → ⎨ ⇒ ⎨ ⎛ R2 ⎞

⎝ Lω

R1 ⎠

(

+ j LCω 2 − 1 ) ⎩Re[G B' ( jω )] = 1 ⎪α ⎜⎜1 + ⎟ =1

α (1 − α )R ⎩ ⎝ R1 ⎟⎠

1 R1

fosc = ,α=

2π LC R1 + R2

3. Application numérique

fosc ≅ 15.9 kHz , α = 0.0476

Sylvain Géronimi Page 192 Oscillateurs sinusoïdaux

UNIVDOCS.COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

Oscillateur à pont de Wien

L’étude proposée concerne le circuit de la figure suivante, utilisant un amplificateur linéaire de tension

supposé idéal.

+ R3 C1

S

10k 15n

-

C2

R2 R4

10k 15n

10k

R1

Condition d’entretien des oscillations

1. Ecrivez la fonction de transfert en boucle ouverte.

2. En boucle fermée, exprimez les conditions d’entretien d’oscillations sinusoïdales.

3. Donnez les règles de démarrage de l’oscillateur.

4. Calculez les valeurs de la fréquence fosc des oscillations et de la résistance R1 .

Stabilisation de l’amplitude des oscillations par thermistance

La résistance R2 s’identifie à une thermistance à coefficient de température négatif telle que

R2 = R0 − a v eff

2

avec R0 = 11 kΩ, a = 10 3 Ω / V 2 et v eff

2

la valeur quadratique moyenne de la tension

aux bornes de R2 .

5. Vérifiez que la condition de démarrage est assurée.

6. Evaluez l’amplitude de la tension de sortie v s en Vpp .

Stabilisation de l’amplitude des oscillations par résistance variable

R3

10k + U1

S

C1

uA741

15n

-

R2

37.5k

R6

C2 D1

R4

15n G

10k J1

J2N4416A R5 C3 D1N4148

100k 100u

La résistance variable est constituée d’un JFET travaillant dans sa zone ohmique et commandé en

tension par un détecteur de crête, Dans ces conditions, la tension v ds ne peut dépasser quelques

Sylvain Géronimi Page 193 Oscillateurs sinusoïdaux

UNIVDOCS.COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

dizaines de mVpp , ce qui explique la présence de la résistance série R6 sur le schéma électrique. Le

transistor possède les caractéristiques IDSS = 14 mA, VP = − 4 V .

7. Donnez l’expression de la résistance RDS du transistor.

8. Ecrivez l’expression de R2 en fonction de RDS , v s et v ds , puis l’expression de R6 .

9. La diode possédant une tension de seuil V0 , écrivez l’expression de VGS en fonction de V0 , v ds

et R2 .

10. Evaluez RON , VGS , v s , RDS et R6 en prenant v ds = 80 mVpp et V0 = 0.6 V .

11. Vérifiez que la condition de démarrage est assurée.

Corrigé

Condition d’entretien des oscillations

1. Fonction de transfert en boucle ouverte

Amplificateur non inverseur : G (p ) = 1 +

R2

(gain constant car amplificateur idéal)

R1

Réseau sélectif : B' (p ) =

RC p

avec R = R3 = R 4 et C = C1 = C2

R 2 C 2 p 2 + 3 RC p + 1

2ζ

p

ω

filtre de type passe-bande de la forme B0' 2 n et de caractéristiques

p 2ζ

+ p +1

ω n2 ωn

∆ω ⎛ R ⎞

= 2ζ = 3 , d’où G(p )B' (p ) = ⎜⎜1 + 2 ⎟⎟

1 1 1 1

B0' = , ωn = , = .

3 RC ωn Q ⎝ R1 ⎠ p ωn

3+ +

ωn p

relation valable car les conditions d’adaptation en tension entre blocs sont respectées. En effet, la

résistance d’entrée est infinie et résistance de sortie est nulle pour le bloc amplificateur idéal. Si

l’amplificateur est réel, la contre-réaction tension-tension conduit à des résultats voisins.

Cependant, le gain peut ne plus être considéré comme constant si la fréquence de l’oscillateur

n’est pas faible par rapport à la bande passante de l’amplificateur.

2. Conditions d’oscillations

⎛ R ⎞

En boucle fermée et en régime établi, G ( jω )B' ( jω ) = ⎜⎜1 + 2 ⎟⎟

1

=1

⎝ R1 ⎠ ⎛ω ω ⎞

3 − j ⎜⎜ n − ⎟⎟

⎝ ω ω n ⎠

Conditions de Barkhausen → ⎨

[ ( ) (

⎧Im G jω B' jω = 0 ) ] ⇒ ⎨

⎧ ω osc = ω n

⎩Re [G ( jω )B ' ( jω ) ] = 1 ⎩ 2R = 2R 1

3. Condition de démarrage

R2

1+ >3 soit R2 supérieure à sa valeur nominale ou R1 inférieure à sa valeur nominale.

R1

Sylvain Géronimi Page 194 Oscillateurs sinusoïdaux

UNIVDOCS.COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

1

4. Application fosc = ≅ 1061 Hz , R1 = 5 kΩ

2π RC

Stabilisation de l’amplitude des oscillations par thermistance

5. Condition de démarrage

R0

Le démarrage est assuré car 1 + > 3 avec l’alimentation éteinte. Une fois l’alimentation

R1

allumée, la tension aux bornes de la thermistance augmente jusqu’à ce que sa valeur ohmique

diminue et se stabilise à R 2 = 2R1 .

6. Amplitude de la tension de sortie

R0 − R2

v eff = = 1Veff ⇒ v s = 3 2 v eff ≅ 4.24 Vpp

a

Stabilisation de l’amplitude des oscillations par résistance variable

7. Expression de la résistance dynamique du JFET

RON −VP

RDS ≅ avec RON ≅ (à partir d’une caractéristique de transfert « stylisée » du JFET)

V I DSS

1 − GS

VP

8. Expressions des résistances R2 et R3

Condition d’oscillations : R 2 = 2 (R 6 + RDS ) car R 6 + R DS s’identifie à R1 des études précédentes

RDS

Pont de résistances : v ds = vs

RDS + R6 + R2

2 RDS v s R2

d’où R2 = et R6 = − RDS

3 v ds 2

9. Expression de la tension de grille

Le redressement de l’alternance négative du signal sinusoïdal de sortie s’effectue en détection

crête puisque R5 C3 >> Tosc , d’où v s pp = 2 (V0 − VGS ) en tenant compte du seuil de conduction de

la diode.

1 − α V0 4 RON

VGS = − avec α = (tension continue négative de commande du JFET canal N).

1 3 R2 v ds

α−

VP

10. Application

RON ≅ 286 Ω , VGS ≅ − 2.45 V , v s ≅ 6.1Vpp , RDS ≅ 738 Ω et R6 ≅ 18 kΩ .

Sylvain Géronimi Page 195 Oscillateurs sinusoïdaux

UNIVDOCS.COM

Université Paul Sabatier Electronique analogique – Problèmes et corrigés

11. Condition de démarrage

R2

Le démarrage est assuré car 1 + > 3 avec l’alimentation éteinte ( VGS = 0 ). A la mise

R6 + RON

sous tension du montage, la valeur de RDS augmente et se stabilise pour vérifier l’égalité

R 2 = 2 (R 6 + RDS ) .

Simulation du circuit

Démarrage de l’oscillateur

4.0V

0V

-4.0V

0s 0.5s 1.0s 1.5s

V(S) V(G)

Time

Régime permanent

4.0V

fosc = 1055 Hz

vs = 6 Vpp

v+ = 2 Vpp v ds = 80 mVpp

0V

VGS = -2.39 V

-4.0V

1.3500s 1.3505s 1.3510s 1.3515s 1.3520s 1.3525s

V(S) V(G) V(U1:+) V(J1:d)

Time

Sylvain Géronimi Page 196 Oscillateurs sinusoïdaux

Vous aimerez peut-être aussi

- Rapport Fin de Stage de LOUARDI MARIADocument59 pagesRapport Fin de Stage de LOUARDI MARIAكمال كمالPas encore d'évaluation

- Traitementdimage 18 19 Exam+sol Tf.Document2 pagesTraitementdimage 18 19 Exam+sol Tf.Sawat SiwarPas encore d'évaluation

- Cours RegulationDocument121 pagesCours RegulationKouakou Joseph N' Guessan75% (4)

- AmplificateurDocument19 pagesAmplificateurHamza EL BADISSI100% (2)

- Examen Transmission22Document3 pagesExamen Transmission22Insafe AarabPas encore d'évaluation

- Signal PDFDocument208 pagesSignal PDFgalou123Pas encore d'évaluation

- Polycope Des ExercicesDocument20 pagesPolycope Des ExercicesYahya Elamrani0% (1)

- CFCIM - 11022015 - Contrat Et Signature Éléctroniques PDFDocument52 pagesCFCIM - 11022015 - Contrat Et Signature Éléctroniques PDFDourhani YassinePas encore d'évaluation

- Chapitre 3 Les Oscillateurs SinusoidauxDocument21 pagesChapitre 3 Les Oscillateurs SinusoidauxPerla del DesiertoPas encore d'évaluation

- Ampli Op en Régime N.L - Problème 2Document1 pageAmpli Op en Régime N.L - Problème 2Mbaira LeilaPas encore d'évaluation

- 1 Exercice Redressement Triphase Commande PDFDocument4 pages1 Exercice Redressement Triphase Commande PDFbhfgtdPas encore d'évaluation

- 4G Planning and Initial Tuning Using Drive Test - SEGHIER & NABIDocument102 pages4G Planning and Initial Tuning Using Drive Test - SEGHIER & NABIBOUZANA ElaminePas encore d'évaluation

- Rapport TP Opt2Document10 pagesRapport TP Opt2arassy azharPas encore d'évaluation

- Problemes Et Corriges-Oscillateurs HarmoniquesDocument7 pagesProblemes Et Corriges-Oscillateurs HarmoniquesÄdnānë SmimitePas encore d'évaluation

- TDs Aléatoires+CorrigéDocument14 pagesTDs Aléatoires+CorrigéOubaida21 SnackPas encore d'évaluation

- tp5 Les Filtres ActifsDocument4 pagestp5 Les Filtres ActifsTS AUTOMATISATION100% (2)

- Chap12 (Controle Auto Du Gain Appliqué Aux Oscillateurs Sinusoidaux)Document29 pagesChap12 (Controle Auto Du Gain Appliqué Aux Oscillateurs Sinusoidaux)sperate0% (1)

- TD Filtrage SolutionEDocument6 pagesTD Filtrage SolutionEliticia ait messaoudePas encore d'évaluation

- Poly TDs TNS Francais 2017 2018Document26 pagesPoly TDs TNS Francais 2017 2018Miloud MOULAY OMARPas encore d'évaluation

- EdeB TD4 1 2020Document2 pagesEdeB TD4 1 2020Arsene SohPas encore d'évaluation

- TNS TD2 Filtrage NumeriqueDocument2 pagesTNS TD2 Filtrage NumeriqueChaima Belhedi100% (1)

- GEL-16120 - Modulation NumeriqueDocument30 pagesGEL-16120 - Modulation NumeriqueIbrahimFaroukSolarPas encore d'évaluation

- Amplificateur de Puissance Classe B, ABDocument7 pagesAmplificateur de Puissance Classe B, ABKhaira ToulaPas encore d'évaluation

- Modulation D'amplitudeDocument5 pagesModulation D'amplitudemengchhyPas encore d'évaluation

- Traitement Du Signal-Eln - L3 TD2: Analyse Et Synthèse Des Filtres AnalogiquesDocument4 pagesTraitement Du Signal-Eln - L3 TD2: Analyse Et Synthèse Des Filtres AnalogiquesSouha KhadraouiPas encore d'évaluation

- Exos-Ampli PuissanceDocument10 pagesExos-Ampli PuissanceFarid BakaPas encore d'évaluation

- Exos Corrigés Analyse de Filtre NumDocument3 pagesExos Corrigés Analyse de Filtre NumDoc100% (1)

- Corrige de L'Exercice 1: Comparateurs de Phase 2.2.: 02 PLL (E+C)Document11 pagesCorrige de L'Exercice 1: Comparateurs de Phase 2.2.: 02 PLL (E+C)Babacar NdiayePas encore d'évaluation

- TD N°1 Elément de Module Circuits Et Réseaux Électriques.Document3 pagesTD N°1 Elément de Module Circuits Et Réseaux Électriques.ELFargaliMohamed0% (1)

- Solutions - Des - Exercices Capteurs Et MétrologieDocument3 pagesSolutions - Des - Exercices Capteurs Et MétrologieAnis Latreche100% (1)

- TD FILTRES Isetcom STICL2 2018Document3 pagesTD FILTRES Isetcom STICL2 2018Mohamed Dhia Eddine DrissPas encore d'évaluation

- Travaux Pratiques 2Document4 pagesTravaux Pratiques 2Cha Bnr100% (1)

- Chapitre 1 Transistor JFET Ver1 11.05.23Document28 pagesChapitre 1 Transistor JFET Ver1 11.05.23AZIL AMINPas encore d'évaluation

- Correction TD 2223Document21 pagesCorrection TD 2223Babacar Mbaye AagPas encore d'évaluation

- Dr. Guermat Noubeil - Support de Cours - Electronique Des ImpulsDocument114 pagesDr. Guermat Noubeil - Support de Cours - Electronique Des ImpulsỖś ɱŏPas encore d'évaluation

- Mémoir 10Document39 pagesMémoir 10amal amoulaPas encore d'évaluation

- Exercices2009 2010Document24 pagesExercices2009 2010Miss AmericanaPas encore d'évaluation

- TD2 Gim2 Geii219 20Document3 pagesTD2 Gim2 Geii219 20Hàmža Ait BoulhcenPas encore d'évaluation

- Chapitre 6 Les Convirtisseurs CAN Et CNADocument12 pagesChapitre 6 Les Convirtisseurs CAN Et CNAAymane Fahmi100% (1)

- Série D'exercices #3: DIODE A JONCTION-Niveau GE-TC1xDocument1 pageSérie D'exercices #3: DIODE A JONCTION-Niveau GE-TC1xAchref Khadraoui100% (1)

- Mod Analog td1 PDFDocument3 pagesMod Analog td1 PDFAbdou Super100% (2)

- Corro TD3 Signaux PhysiqueDocument13 pagesCorro TD3 Signaux PhysiqueBoris Emmanuel AssemienPas encore d'évaluation

- Amplificateur Lineaire Integre Et RetroaDocument10 pagesAmplificateur Lineaire Integre Et Retroapape diopPas encore d'évaluation

- Communication Analogique Et Numérique: Exercice ExerciceDocument2 pagesCommunication Analogique Et Numérique: Exercice ExerciceFatima EL FasihiPas encore d'évaluation

- Montage Amplificateur en Emetteur Commun "Bootstrap" Montage Amplificateur en Emetteur Commun "Bootstrap"Document3 pagesMontage Amplificateur en Emetteur Commun "Bootstrap" Montage Amplificateur en Emetteur Commun "Bootstrap"manalPas encore d'évaluation

- Série Td2 #TS PDFDocument4 pagesSérie Td2 #TS PDFIlyas KendouciPas encore d'évaluation

- Serie de TD 1+corrigeDocument5 pagesSerie de TD 1+corrigeIdir AmeurPas encore d'évaluation

- TPs Automatique 1Document6 pagesTPs Automatique 1HolaPas encore d'évaluation

- TD7 - Traitement de Singal - 2018 - 2019Document9 pagesTD7 - Traitement de Singal - 2018 - 2019nait ahmed hasnaPas encore d'évaluation

- Sujet TP 1Document6 pagesSujet TP 1Ibidhi EskanderPas encore d'évaluation

- ExerciceDocument13 pagesExerciceLoubna ElPas encore d'évaluation

- Électronique Numérique: Semaine 5Document40 pagesÉlectronique Numérique: Semaine 5Amechghal LahcenPas encore d'évaluation

- TD4 CorrDocument8 pagesTD4 CorrIslem BenmesbahPas encore d'évaluation

- Série Td2 #TS PDFDocument4 pagesSérie Td2 #TS PDFIlyas KendouciPas encore d'évaluation

- Filtrage AnalogiqueDocument16 pagesFiltrage AnalogiqueAli OuattaraPas encore d'évaluation

- TD TasDocument3 pagesTD TasINTTICPas encore d'évaluation

- 5BTC Hyper Part2 09Document60 pages5BTC Hyper Part2 09Yàs SîñéPas encore d'évaluation

- ReseauDocument8 pagesReseaupaulPas encore d'évaluation

- Rappel Avec TD Analyse de Fourier - Séries Et Intégrale de Fourier ELN 3Document4 pagesRappel Avec TD Analyse de Fourier - Séries Et Intégrale de Fourier ELN 3DocPas encore d'évaluation

- TP 3Document7 pagesTP 3Méd El YazidPas encore d'évaluation

- Correction Examen2 Le202Document6 pagesCorrection Examen2 Le202Ibrahim BahloulPas encore d'évaluation

- Mines MP 2008 CorrigeDocument4 pagesMines MP 2008 CorrigeWalid rabojaPas encore d'évaluation

- Corrections Ec td3 Oscillateurs Electroniques CorrectionDocument3 pagesCorrections Ec td3 Oscillateurs Electroniques CorrectionYoussef MahdiPas encore d'évaluation

- DL1 SolDocument5 pagesDL1 Solmehdi benmassoudPas encore d'évaluation

- ELCIN - 40 Oscillateur A Resistance Negative Avec RLC SerieDocument4 pagesELCIN - 40 Oscillateur A Resistance Negative Avec RLC Seriesih emPas encore d'évaluation

- Traitementdimage 17 18 Rattr+sol Tf.Document2 pagesTraitementdimage 17 18 Rattr+sol Tf.Sawat SiwarPas encore d'évaluation

- Traitementdimage 16 17 Rattr+sol Tf.Document2 pagesTraitementdimage 16 17 Rattr+sol Tf.Sawat SiwarPas encore d'évaluation

- Traitementdimage 16 17 Exam+sol Tf.Document2 pagesTraitementdimage 16 17 Exam+sol Tf.Sawat SiwarPas encore d'évaluation

- Emd Cem Uef21 2011 PDFDocument1 pageEmd Cem Uef21 2011 PDFayoub chahPas encore d'évaluation

- Cours Introduction à La CEM ISIMM 2023Document218 pagesCours Introduction à La CEM ISIMM 2023Sawat SiwarPas encore d'évaluation

- Emd Cem 2015Document4 pagesEmd Cem 2015Sawat SiwarPas encore d'évaluation

- Corrigé Epreuve TAS M1 S1 RT 2018Document9 pagesCorrigé Epreuve TAS M1 S1 RT 2018Sawat SiwarPas encore d'évaluation

- Merged 20230416 220010Document6 pagesMerged 20230416 220010Sawat SiwarPas encore d'évaluation

- L2 en Cours 4 AO ImpDocument13 pagesL2 en Cours 4 AO ImpThe geek CuestaPas encore d'évaluation

- 3 Echantillonnage Des SignauxDocument1 page3 Echantillonnage Des SignauxAbdo BenotsmanPas encore d'évaluation

- TTL CmosDocument4 pagesTTL CmosmedPas encore d'évaluation

- Parcours PDFDocument2 pagesParcours PDFIssam MobPas encore d'évaluation

- 2 Analyse Machine EtatsDocument15 pages2 Analyse Machine EtatsMENANI ZineddinePas encore d'évaluation

- DOMOVEA FR 220110 HAGERDocument12 pagesDOMOVEA FR 220110 HAGERChristophe De OliveiraPas encore d'évaluation

- TPN 4: Détection Infrarouge Et Étude Du Détecteur Photoélectrique - RéflexDocument8 pagesTPN 4: Détection Infrarouge Et Étude Du Détecteur Photoélectrique - RéflexFotcha EricPas encore d'évaluation

- Cours IoT P1S2Document21 pagesCours IoT P1S2saadPas encore d'évaluation

- 2 1 Introduction - AutomatiqueDocument10 pages2 1 Introduction - AutomatiqueAmine MahyouPas encore d'évaluation

- MergedDocument88 pagesMergedZoheir AhmedPas encore d'évaluation

- Arabi MémoireDocument77 pagesArabi MémoirehoulteurbePas encore d'évaluation

- La TelephonieDocument8 pagesLa TelephonieSonia BoufalaPas encore d'évaluation

- E Thyristor2Document4 pagesE Thyristor2Yahya AminePas encore d'évaluation

- Notice Autoradio Trafic 3Document8 pagesNotice Autoradio Trafic 3Mendoza adacPas encore d'évaluation

- Architecture D'un MicroprocesseurDocument7 pagesArchitecture D'un MicroprocesseurkeylogPas encore d'évaluation

- IQLINKDocument55 pagesIQLINKchrispau64Pas encore d'évaluation

- C4 SequentielleDocument82 pagesC4 SequentielleOumar MandodjoPas encore d'évaluation

- Correctiontd3 Bus de TerrainDocument3 pagesCorrectiontd3 Bus de TerrainSouhaila LaghlimiPas encore d'évaluation

- A4200PBXDocument944 pagesA4200PBXmoore_steve86% (7)

- TD1 Architecture Des OrdinateursDocument2 pagesTD1 Architecture Des OrdinateursMarcel poufong100% (1)

- Polycom RealPresence Group 310-720p - Kit de Vidéo-Conférence - Avec EagleEye IV-12x Camera (7200-65330-101)Document4 pagesPolycom RealPresence Group 310-720p - Kit de Vidéo-Conférence - Avec EagleEye IV-12x Camera (7200-65330-101)donald landohPas encore d'évaluation

- Traitement de SignalDocument20 pagesTraitement de SignalAymen GoubaaPas encore d'évaluation

- Tp3 Mesure Des ResistancesDocument7 pagesTp3 Mesure Des ResistancesMarie Olive FoffiePas encore d'évaluation

- 845 Relays Brochure HELLA FRDocument72 pages845 Relays Brochure HELLA FRSeve NebawaogaPas encore d'évaluation