Académique Documents

Professionnel Documents

Culture Documents

TP Compteur GMSA

Transféré par

Sheeya FilaliTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TP Compteur GMSA

Transféré par

Sheeya FilaliDroits d'auteur :

Formats disponibles

Université

Sidi Mohamed Ben Abdellah 2021-‐2022

Ecole Nationale des Sciences Appliquées

Département Génie Industriel

TP : Analyse par simulation des compteurs - GMSA_1

OBJECTIFS :

Analyser par simulation sur Proteus (ou tout autre logiciel de simulation) le fonctionnement

de compteurs asynchrone et synchrone.

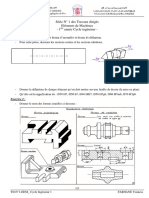

1. COMPTEUR BINAIRE ASYNCHRONE

Un compteur est constitué ́ de bascules JK (ou de bascules D) montées en diviseur de fréquence

par deux. Il est dit asynchrone lorsque chacune de ces bascules n'utilisent pas le même signal

d'horloge. On donne le schéma d'un compteur binaire asynchrone 3 bits :

SAISIE DU SCHÉMA ET LABELLISATION DES FILS

-‐ Saisir ce schéma sur Proteus

-‐ Placer les signaux d’entrées et les sondes de tensions. Configurer les générateurs de la façon

suivante :

LANCEMENT DE LA SIMULATION ET EXPLOITATION DES RÉSULTATS

1) Lancer la simulation et imprimer les résultats.

2) Écrire sous chaque période d'horloge la valeur de sortie du compteur en décimal (Q0

constitue le bit de poids faible et Q2 constitue le bit de poids fort). Donner le modulo du

compteur.

3) Repérer TH (la période du signal d'horloge H) sur le chronogramme. Calculer la fréquence

FH -‐ Mesurer précisément la période TQ0 du signal de sortie Q0. Calculer sa fréquence FQ0. En

déduire le rapport de division de fréquence entre la sortie Q0 et l'entrée H.

4) Effectuer ces mesures pour les sorties Q1 et Q2.

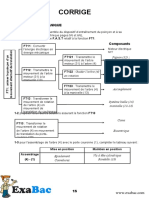

2. COMPTEUR BINAIRE SYNCHRONE

Un compteur constitué́ de bascules JK est dit synchrone lorsque chacune de ces bascules

utilisent le même signal d'horloge. On donne le schéma d'un compteur binaire synchrone :

LANCEMENT DE LA SIMULATION ET EXPLOITATION DES RÉSULTATS

1) Lancer la simulation sur 20 périodes de H.

2) Visualiser les chronogrammes en zoomant sur la transition de la valeur comptée 15 à 0.

Mesurer le retard entre un changement d'état de la sortie Q0 et le front d'horloge qui

provoque ce changement.

3) Effectuer la même mesure pour la sortie Q1, Q2 et Q3 (toujours par rapport au signal

d'horloge). Que peut-‐on dire des différents retards ?

4) En quoi est dû le retard entre Q0 et H ?

5) Pourquoi n’y a-‐t-‐il pas de retard entre Q0, Q1, Q2 et Q3 contrairement au montage

asynchrone ?

6) En observant les chronogrammes complets, quel doit être le niveau logique de Q0 pour que

s’opère un changement d’état de Q1 ?

7) En déduire la justification du câblage de Q0 sur J et K de la seconde bascule :

8) En observant les chronogrammes complets, quel doit être les niveaux logiques de Q0 et

Q1 pour que s’opère un changement d’état de Q2 ?

9) En déduire la justification du câblage de U3:A sur J et K de la troisième bascule :

10) En observant les chronogrammes complets, quel doit être les niveaux logiques de Q0, Q1

et Q2 pour que s’opère un changement d’état de Q3 ?

11) En déduire la justification du câblage de U4:A sur J et K de la quatrième bascule.

Vous aimerez peut-être aussi

- Chapitre 3Document15 pagesChapitre 3william tiakoPas encore d'évaluation

- TP4 EstsbDocument6 pagesTP4 EstsbLamyae ChPas encore d'évaluation

- Chapitre 5Document12 pagesChapitre 5bachar soumiaPas encore d'évaluation

- Série D'exercices N°3-3tech-Bascules-Compteurs-2012-2013Document9 pagesSérie D'exercices N°3-3tech-Bascules-Compteurs-2012-2013Hyacinthe Kossi100% (3)

- TP LCS 2022 2023Document3 pagesTP LCS 2022 2023kka29173Pas encore d'évaluation

- Serie 1Document9 pagesSerie 1OMAR ENNAJIPas encore d'évaluation

- TD5 enDocument1 pageTD5 enIkram ElaimaPas encore d'évaluation

- Cours LogiqueDocument11 pagesCours LogiqueMohamed Anouar ChakerPas encore d'évaluation

- Fonction ComptageDocument9 pagesFonction ComptagedukenukembabiesPas encore d'évaluation

- Cours de Compteurs Num Riques 2015-2016Document28 pagesCours de Compteurs Num Riques 2015-2016Mamadou Korka KantéPas encore d'évaluation

- Wa0018.Document4 pagesWa0018.ffghjhkkPas encore d'évaluation

- Chapitre 5 - Compteur Et DécompteurDocument11 pagesChapitre 5 - Compteur Et DécompteurDouaa GhazouaniPas encore d'évaluation

- Les Compteurs ISISDocument10 pagesLes Compteurs ISISDiego MezaPas encore d'évaluation

- Les CompteursDocument7 pagesLes CompteursSoufiane AggourPas encore d'évaluation

- Compte AsynchroneDocument5 pagesCompte Asynchroneياسين بوعيشيPas encore d'évaluation

- Chapitre II Comp Decomp CNDocument9 pagesChapitre II Comp Decomp CNKhalil FrikhaPas encore d'évaluation

- TP N4compteur - SynchroneDocument2 pagesTP N4compteur - Synchroneamine cheurfaPas encore d'évaluation

- Exercices Sur Les CompteursDocument11 pagesExercices Sur Les CompteursThe geek Cuesta100% (1)

- Compte UrDocument38 pagesCompte Urisraalaya167Pas encore d'évaluation

- Les Compteurs Et Decompteurs PDFDocument11 pagesLes Compteurs Et Decompteurs PDFbakkari MPas encore d'évaluation

- Série 2 - CompteursDocument4 pagesSérie 2 - CompteursMOURAD NIMIROUPas encore d'évaluation

- Électronique TsaDocument21 pagesÉlectronique TsaadamsclovisherbertsPas encore d'évaluation

- Les CompteursDocument20 pagesLes CompteursMontassar Lajili79% (14)

- Compte UrsDocument11 pagesCompte Ursmaiga mohamedPas encore d'évaluation

- Compte UrsDocument11 pagesCompte Ursmaiga mohamedPas encore d'évaluation

- Compte UrsDocument11 pagesCompte Ursmaiga mohamedPas encore d'évaluation

- Compte UrsDocument11 pagesCompte Ursmaiga mohamedPas encore d'évaluation

- Compte UrsDocument11 pagesCompte Ursmaiga mohamedPas encore d'évaluation

- Compte UrsDocument11 pagesCompte Ursmaiga mohamedPas encore d'évaluation

- TP Elect Pui Shache Ur MosDocument3 pagesTP Elect Pui Shache Ur MosAbdø AboulQasimPas encore d'évaluation

- Traiter: Logiques SequentiellesDocument4 pagesTraiter: Logiques SequentiellesBlaise EdimoPas encore d'évaluation

- Automatisme Chapitre 5Document23 pagesAutomatisme Chapitre 5Meryem JabranePas encore d'évaluation

- CR CompteursDocument6 pagesCR CompteursGuel's MwenderwaPas encore d'évaluation

- CH 6 CompteursDocument7 pagesCH 6 CompteursGOUMMAR ABDERRAHIMPas encore d'évaluation

- TP3 Bascules Compteurs RegistresDocument3 pagesTP3 Bascules Compteurs Registreseya arfaouiPas encore d'évaluation

- TP Cao Electronique 1 - 230921 - 111416 - 230921 - 120514Document7 pagesTP Cao Electronique 1 - 230921 - 111416 - 230921 - 120514Mohamed CharradaPas encore d'évaluation

- PDF ExCompteurDocument22 pagesPDF ExCompteurAnas le Rouge100% (2)

- TP L&C22Document3 pagesTP L&C22Ømãx Õmär ÄsrîPas encore d'évaluation

- Exos de Logique SéquentielleDocument5 pagesExos de Logique SéquentielleSabrine Khoualdi100% (1)

- TD2 - Chaîne DacquisitionDocument3 pagesTD2 - Chaîne DacquisitionMootez ZouariPas encore d'évaluation

- 44444Document4 pages44444TEDIE TCHANYAPas encore d'évaluation

- TP 1Document68 pagesTP 1Hana KhemissiPas encore d'évaluation

- TP Circuits SAquentiels Bascules Et Compteurs 2020 CopieDocument3 pagesTP Circuits SAquentiels Bascules Et Compteurs 2020 CopieIslem Branci100% (1)

- Chapitre 6Document19 pagesChapitre 6RABAB MASDOURPas encore d'évaluation

- TP2MISEDocument1 pageTP2MISEBenrabah IkhlasPas encore d'évaluation

- Serie D'exercices 4 BASCULES 2021-2022Document3 pagesSerie D'exercices 4 BASCULES 2021-2022Manel AsnicarPas encore d'évaluation

- TD Cna CanDocument2 pagesTD Cna CanYOUNESS KARAMI0% (1)

- Chap7 Les CompteursDocument10 pagesChap7 Les CompteursDěmøïšěllë RãnPas encore d'évaluation

- TDN°1 Compteur DecompteurDocument1 pageTDN°1 Compteur DecompteurKhalil FrikhaPas encore d'évaluation

- Examen 2005Document4 pagesExamen 2005Yassir RochdPas encore d'évaluation

- Chapitre 6 Registre Et CompteursDocument14 pagesChapitre 6 Registre Et CompteursAbdelkerim LemaadiPas encore d'évaluation

- TH4 1 EvalDocument5 pagesTH4 1 EvalMehdi BouchamiPas encore d'évaluation

- EvaluationDocument5 pagesEvaluationBucky's DollPas encore d'évaluation

- LogiqueSéquentielle Partie2Document13 pagesLogiqueSéquentielle Partie2Mehdi El AlaouiPas encore d'évaluation

- Se - Rie 3 Logique Se - Quentielle ENSADocument8 pagesSe - Rie 3 Logique Se - Quentielle ENSAFathi AbderrahmanePas encore d'évaluation

- TP AutomatismeDocument32 pagesTP AutomatismeKawtar FelkiPas encore d'évaluation

- Cours_Signal_Fltrage_Mrabti_22-23Document18 pagesCours_Signal_Fltrage_Mrabti_22-23Sheeya FilaliPas encore d'évaluation

- SimplexeDocument94 pagesSimplexeSheeya FilaliPas encore d'évaluation

- Files D'attentesDocument88 pagesFiles D'attentesSheeya FilaliPas encore d'évaluation

- Annexe 2 Poulie-Courroie CranteeDocument1 pageAnnexe 2 Poulie-Courroie CranteeSheeya FilaliPas encore d'évaluation

- Chap1 RO, Modélisation1Document23 pagesChap1 RO, Modélisation1Sheeya FilaliPas encore d'évaluation

- Exercices - Serie 5 - Elts de Machines CI1 2022 - 2023Document1 pageExercices - Serie 5 - Elts de Machines CI1 2022 - 2023Sheeya FilaliPas encore d'évaluation

- ANNEXE 1 POULIE-COURROIE Plates Et TrapézDocument2 pagesANNEXE 1 POULIE-COURROIE Plates Et TrapézSheeya FilaliPas encore d'évaluation

- TDDocument53 pagesTDSheeya Filali100% (2)

- Exercices - Serie 1 - Elts de Machines CI1 2022 - 2023Document3 pagesExercices - Serie 1 - Elts de Machines CI1 2022 - 2023Sheeya FilaliPas encore d'évaluation

- Exercices - Serie 2 - Elts de Machines CI1 2022 - 2023Document4 pagesExercices - Serie 2 - Elts de Machines CI1 2022 - 2023Sheeya FilaliPas encore d'évaluation

- TD FilesDocument7 pagesTD FilesSheeya Filali100% (1)

- 00 Doc PrincipalDocument85 pages00 Doc PrincipalSheeya FilaliPas encore d'évaluation

- TD1MERISEDocument2 pagesTD1MERISESheeya FilaliPas encore d'évaluation

- Exercices RévisionDocument1 pageExercices RévisionSheeya FilaliPas encore d'évaluation

- Cours Microprocesseur ENSADocument138 pagesCours Microprocesseur ENSASheeya FilaliPas encore d'évaluation

- TD - Examen BlancDocument2 pagesTD - Examen BlancSheeya FilaliPas encore d'évaluation

- Compteur Synch-Nou-15-16 ProfDocument9 pagesCompteur Synch-Nou-15-16 ProfHayet BechedliPas encore d'évaluation

- RapportDocument4 pagesRapportDenner PaganotiPas encore d'évaluation

- Technique La Description: Multifonction ÉlectroniqueDocument27 pagesTechnique La Description: Multifonction Électroniqueabdelhadi elkhyatPas encore d'évaluation

- Gestion de ParkingDocument7 pagesGestion de ParkingsaidloubarPas encore d'évaluation

- Lydec GuideAmenageurs ANNEXE3Document28 pagesLydec GuideAmenageurs ANNEXE3fouad_zehouani75% (4)

- Technique CDocument8 pagesTechnique CKarim FathiPas encore d'évaluation

- TP logique-ERII4Document8 pagesTP logique-ERII4galougalakPas encore d'évaluation

- Robot Élévateur JJJJJJJJJJJJJJJJJJJJJJJJJJJJJJJJJ PDFDocument50 pagesRobot Élévateur JJJJJJJJJJJJJJJJJJJJJJJJJJJJJJJJJ PDFJawher Salem100% (1)

- Item 1 2 3 4 - SL7000 - Guide Technique SL7000Document20 pagesItem 1 2 3 4 - SL7000 - Guide Technique SL7000SALVADORPas encore d'évaluation

- Epreuve de CircuitsDocument2 pagesEpreuve de CircuitsThibou GabienPas encore d'évaluation

- Corrigé TD2 CNDocument6 pagesCorrigé TD2 CNPapeCheikh SYLLAPas encore d'évaluation

- NjipoolDocument5 pagesNjipoolmnawarPas encore d'évaluation

- Mini-Projet Automatismes Cycle Ing 2014 - 15 PDFDocument2 pagesMini-Projet Automatismes Cycle Ing 2014 - 15 PDFSean Mcfarland100% (1)

- Cours API MII SembarquésDocument40 pagesCours API MII SembarquésGabbianimarcoPas encore d'évaluation

- Micro Control Eur 2Document23 pagesMicro Control Eur 2Hayet BechedliPas encore d'évaluation

- TD CapteursDocument6 pagesTD CapteursAbdessamad BoujbiraPas encore d'évaluation

- Stage 3Document31 pagesStage 3chedi troudi100% (1)

- U518176-FR-Equalis S Notice-Rev1Document109 pagesU518176-FR-Equalis S Notice-Rev1Mamadou djibril Ba86% (7)

- DES MatieresDocument49 pagesDES MatieresMAROUA TWALBIAPas encore d'évaluation

- Chapitre-3 - Les Appareils de MesureDocument6 pagesChapitre-3 - Les Appareils de Mesurealouani souhirPas encore d'évaluation

- Cours 4 - TableauxDocument43 pagesCours 4 - Tableauxϟ KaiZyX ϟPas encore d'évaluation

- Edition 4 - Guide Mise en Service Et Utilisation T2MDocument79 pagesEdition 4 - Guide Mise en Service Et Utilisation T2MGusdeluxe0% (1)

- TP Electronique Numérique SéquentielDocument23 pagesTP Electronique Numérique Séquentielall you need كل ما تحتاجPas encore d'évaluation

- 03 1200 Bloc Temporisations IEC Et Compteurs IEC Pour SIMATIC S7-1200Document52 pages03 1200 Bloc Temporisations IEC Et Compteurs IEC Pour SIMATIC S7-1200Abdelhalim ZAOUIPas encore d'évaluation

- Item 1 2 3 4 - SL7000 - Présentation Compteur SL7000 CepelDocument37 pagesItem 1 2 3 4 - SL7000 - Présentation Compteur SL7000 CepelSALVADORPas encore d'évaluation

- Circuit LogiqueDocument23 pagesCircuit LogiqueSidahmed LarbaouiPas encore d'évaluation

- TPN°14 - Mémoire - Temporisation - Comptage - PL7 PRO - CorrigéDocument13 pagesTPN°14 - Mémoire - Temporisation - Comptage - PL7 PRO - CorrigébelkacemiPas encore d'évaluation

- Brochage Des Principaux CI-TTLDocument8 pagesBrochage Des Principaux CI-TTLBrahimElbazPas encore d'évaluation

- Recherche Fuites EauDocument35 pagesRecherche Fuites Eaualpha999Pas encore d'évaluation

- Revue des incompris revue d'histoire des oubliettes: Le Réveil de l'Horloge de Célestin Louis Maxime Dubuisson aliéniste et poèteD'EverandRevue des incompris revue d'histoire des oubliettes: Le Réveil de l'Horloge de Célestin Louis Maxime Dubuisson aliéniste et poèteÉvaluation : 3 sur 5 étoiles3/5 (3)

- L'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.D'EverandL'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.Évaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Le guide du hacker : le guide simplifié du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandLe guide du hacker : le guide simplifié du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 5 sur 5 étoiles5/5 (2)

- Apprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationD'EverandApprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationPas encore d'évaluation

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Piraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéD'EverandPiraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéPas encore d'évaluation

- Dark Python : Apprenez à créer vos outils de hacking.D'EverandDark Python : Apprenez à créer vos outils de hacking.Évaluation : 3 sur 5 étoiles3/5 (1)

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- Technologie automobile: Les Grands Articles d'UniversalisD'EverandTechnologie automobile: Les Grands Articles d'UniversalisPas encore d'évaluation

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- Le money management facile à apprendre: Comment tirer profit des techniques et stratégies de gestion de l'argent pour améliorer l'activité de trading en ligneD'EverandLe money management facile à apprendre: Comment tirer profit des techniques et stratégies de gestion de l'argent pour améliorer l'activité de trading en ligneÉvaluation : 3 sur 5 étoiles3/5 (3)

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Kali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.D'EverandKali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.Évaluation : 5 sur 5 étoiles5/5 (1)

- Le Guide Rapide Du Cloud Computing Et De La CybersécuritéD'EverandLe Guide Rapide Du Cloud Computing Et De La CybersécuritéPas encore d'évaluation

- Stratégie d'Investissement en Crypto-monnaie: Comment Devenir Riche Avec les Crypto-monnaiesD'EverandStratégie d'Investissement en Crypto-monnaie: Comment Devenir Riche Avec les Crypto-monnaiesÉvaluation : 3.5 sur 5 étoiles3.5/5 (11)

- Python Offensif : Le guide du débutant pour apprendre les bases du langage Python et créer des outils de hacking.D'EverandPython Offensif : Le guide du débutant pour apprendre les bases du langage Python et créer des outils de hacking.Pas encore d'évaluation

- Le marketing d'affiliation en 4 étapes: Comment gagner de l'argent avec des affiliés en créant des systèmes commerciaux qui fonctionnentD'EverandLe marketing d'affiliation en 4 étapes: Comment gagner de l'argent avec des affiliés en créant des systèmes commerciaux qui fonctionnentPas encore d'évaluation

- Dans l'esprit des grand investisseurs: Un voyage à la découverte de la psychologie utilisée par les plus grands investisseurs de tous les temps à travers des analyses opérationnellD'EverandDans l'esprit des grand investisseurs: Un voyage à la découverte de la psychologie utilisée par les plus grands investisseurs de tous les temps à travers des analyses opérationnellÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- Le plan marketing en 4 étapes: Stratégies et étapes clés pour créer des plans de marketing qui fonctionnentD'EverandLe plan marketing en 4 étapes: Stratégies et étapes clés pour créer des plans de marketing qui fonctionnentPas encore d'évaluation

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation

- Le Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsD'EverandLe Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsÉvaluation : 4 sur 5 étoiles4/5 (2)

- La psychologie du trading facile à apprendre: Comment appliquer les stratégies et les attitudes psychologiques des traders gagnants pour réussir dans le trading.D'EverandLa psychologie du trading facile à apprendre: Comment appliquer les stratégies et les attitudes psychologiques des traders gagnants pour réussir dans le trading.Évaluation : 4 sur 5 étoiles4/5 (2)