Académique Documents

Professionnel Documents

Culture Documents

Exercice de Logique Sequentielle

Transféré par

Khawla BenzinebCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Exercice de Logique Sequentielle

Transféré par

Khawla BenzinebDroits d'auteur :

Formats disponibles

FEUILLE D'EXERCICES : Logique

TABLE DES MATIERES :

1 FONCTION DECOMPTEUR ASYNCHRONE A BASCULE D.............................................................................................2

2 FONCTION COMPTEUR ASYNCHRONE A BASCULE D..................................................................................................3

3 FONCTION COMPTEUR ASYNCHRONE MODULO 5 A BASCULE D...........................................................................4

4 FONCTION COMPTEUR ASYNCHRONE MODULO 10 A BASCULE D..........................................................................5

5 FONCTION "REGISTRE A DECALAGE"...............................................................................................................................6

6 ETUDE DU "COMPTEUR A ANNEAU".................................................................................................................................8

7 ETUDE DU "COMPTEUR DE JOHNSON".............................................................................................................................9

8 FONCTION COMPTEUR ASYNCHRONE MODULO X A BASCULES JK"...................................................................10

9 FONCTION COMPTEUR ASYNCHRONE MODULO 10 A BASCULE JK......................................................................11

10 FONCTION "DIVISION DE FREQUENCE".........................................................................................................................12

11 FONCTION ASYNCHRONE A BASCULE JK.....................................................................................................................14

12 ETUDE D’UN COMPTEUR BINAIRE...................................................................................................................................15

13 ETUDE DE COMPTEURS.......................................................................................................................................................17

14 ASSOCIATIONS DE COMPTEURS MODULO 10...............................................................................................................19

15 FONCTION "COMPTEUR A MODULO DEFINI PAR CABLAGE"..................................................................................20

16 ETUDE D’UN COMPTEUR-DECOMPTEUR A PRECHARGEMENT...............................................................................22

17 COMPARER DES CHRONOGRAMMES SYNCHRONES ET ASYNCHRONES.............................................................25

18 ANNEXE...................................................................................................................................................................................27

HEF4518B DUAL BCD COUNTER..................................................................................................................................................................................................... 27

74HC/ HCT393 DUAL 4-BIT BINARY RIPPLE COUNTER..................................................................................................................................................... 27

74HC/HCT193 PRESETTABLE SYNCHRONOUS 4-BIT BINARY UP/DOWN COUNTER.................................................................................................... 28

74HC/HCT4040 12-STAGE BINARY RIPPLE COUNTER........................................................................................................................................................... 29

74HC/HCT163 PRESETTABLE SYNCHRONOUS 4-BIT BINARY COUNTER......................................................................................................................... 30

Exercices logique séquentielle – V1.31 1/30

Lycée Jules Ferry – Versailles - 2007 - 2008

CRDEMA

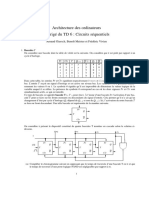

1 FONCTION DECOMPTEUR ASYNCHRONE A BASCULE D

Schéma structurel :

1. Le fonctionnement de ces bascules es-il synchrone ou asynchrone ? Argumenter votre réponse.

a Qa b Qb c Qc

1D 1D 1D

H

C1 C1 C1

2. Tracer les chronogra mmes des sorties Qa, Qb et Qc (à l’état initial, Qa=Qb=Qc= "0").

3. Convertir en décimal les trois bits binaires Qc, Qb et Qa en prenant Qa pour bit de poids faible.

4. Quelle est la fonction réalisée ?

5. Donner le modulo du compteur

H

1

t

0

Qa 1

t

0

Qb 1

t

0

Qc 1

t

0

NQD0

t

Exercices logique séquentielle – V1.31 2/30

Lycée Jules Ferry – Versailles - 2007 - 2008

CRDEMA

2 FONCTION COMPTEUR ASYNCHRONE A BASCULE D

Schéma structurel :

1. Le fonctionnement de ces bascules es-il synchrone ou asynchrone ? Argumenter votre réponse.

a Qa b Qb c Qc

1D 1D 1D

H

C1 C1 C1

2. Tracer les chronogrammes des sorties Qa, Qb et Qc (à l’état initial, Qa =Qb=Qc= "0").

3. Convertir en décimal les trois bits binaires Qc, Qb et Qa en prenant Qa pour bit de poids faible.

4. Quelle est la fonction réalisée ? Comparer ce schéma structurel avec celui de l’exercice précédent et conclure sur

l’incidence de la fonction réalisée.

5. Donner le modulo du compteur

H1

t

0

Qa 1

t

0

Qb 1

t

0

Qc 1

t

0

NQD0

t

Exercices logique séquentielle – V1.31 3/30

Lycée Jules Ferry – Versailles - 2007 - 2008

CRDEMA

3 FONCTION COMPTEUR ASYNCHRONE MODULO 5 A BASCULE D

1. Donner la table de vérité de l’opérateur logique (/R = f (Qa, Qc))

2. Quel est le role de l’entrée /R ?A quel niveau est elle active ? Cette entrée est dite prioritaire, qu’entendez vous par

là ?

3. Tracer les chronogrammes des sorties Qa, Qb, Qc et /R (à l’état initial, Qa=Qb=Qc= "0").

4. Convertir en décimal les trois bits binaires Qc, Qb et Qa en prenant Qa pour bit de poids faible.

5. Quelle est la fonction réalisée ?

Exercices logique séquentielle – V1.31 4/30

Lycée Jules Ferry – Versailles - 2007 - 2008

CRDEMA

4 FONCTION COMPTEUR ASYNCHRONE MODULO 10 A BASCULE D

1. Donner la table de vérité de l’opérateur logique (R = f (Q1, Q3))

2. Quel est le rôle de l’entrée R ? A quel niveau est elle active ?

3. Tracer les chronogrammes des sorties Q0, Q1, Q2, Q3 et R (à l’état i nitial, Q0=Q1=Q2=Q3= "0").

4. Convertir en décimal les trois bits binaires Q0, Q1, Q2 et Q3 en prenant Q0 pour bit de poids faible.

5. Quelle est la fonction réalisée ?

Exercices logique séquentielle – V1.31 5/30

Lycée Jules Ferry – Versailles - 2007 - 2008

CRDEMA

5 FONCTION "REGISTRE A DECALAGE".

Le schéma structurel pourrait être réalisé à partir du circuit logique CD4013A ou d’un 74LS374

Schéma structurel :

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

D 1D

1D 1D 1D 1D 1D 1D 1D

C1

CL

C1 C1 C1 C1 C1 C1 C1

Construire le chronogramme de cette structure demande d’avoir à l’esprit que tout opérateur introduit un temps de latence

entre le moment de la commande et celui où le résultat aboutit en sortie. Ce temps est appelé temps de propagation. Or ici les

entrées de commandes sont actionnées simultanément. Lors d’un front montant de CL un opérateur voit donc l’état de

l’opérateur qui le précède avant que celui-ci n’ait eu le temps de changer d’état. Ce principe étant admis vous pouvez

construire successivement les chronogrammes de Q0, Q1,…, Q6 et Q7

Chronogrammes en page suivante

Exercices logique séquentielle – V1.31 6/30

Lycée Jules Ferry – Versailles - 2007 - 2008

CRDEMA

CL 1 t

0

D 1 tt

0 tt

Q0 1 tt

0 tt

Q1 1 t

0

Q2 1

0

Q3 1

0

Q4 1

0

Q5 1

0

Q6 1

0

Q7 1

0

0 0,2 0,4 0,6 0,8 1 1,2 1,4 1,6 1,8 2 2,2 2,4 2,6 2,8 ms

Exercices logique séquentielle – V1.31 7/30

Lycée Jules Ferry – Versailles - 2007 -

6 ETUDE DU "COMPTEUR A ANNEAU".

Schéma structurel.

1. Tracer les chronogrammes de Q0, Q1 et Q2 (s'aider du mémotech pour la documentation du CD4013).

2. Exprimer la fréquence FQ0 en fonction de FH

3. Au vu des chronogrammes, indiquer le modulo de ce compteur.

H

1

t

0

RAZ

1

t

0

Q0 1

t

0

Q1 1

t

0

Q2 1

0 t

Exercices logique séquentielle – V1.31 8/30

Lycée Jules Ferry – Versailles - 2007 -

7 ETUDE DU "COMPTEUR DE JOHNSON".

Schéma structurel.

1. Faire le même travail que précédemment (compteur en anneau) sur ce nouveau schéma

2. Quelle différence existe-t-il entre ce schéma et le précédent ? Quelle en est la conséquence sur le modulo

et la fréquence des signaux de sortie?

H

1

t

0

RAZ

1

t

0

Q0 1

t

0

Q1 1

t

0

Q2 1

0 t

Exercices logique séquentielle – V1.31 9/30

Lycée Jules Ferry – Versailles - 2007 -

8 FONCTION COMPTEUR ASYNCHRONE MODULO X A BASCULES JK".

1. Sur quel front fonctionnent les bascules ?

2. A quel niveau logique les entrées /R sont elles activent ?

3. Compléter les chronogrammes de Qa, Qb, Qc et de /R (à l’état initial, Qa=Qb=Qc= "0").

4. Donner un nom à cette structure (modulo) ?

Exercices logique séquentielle – V1.31 10/30

Lycée Jules Ferry – Versailles - 2007 -

9 FONCTION COMPTEUR ASYNCHRONE MODULO 10 A BASCULE JK

On désire réaliser un compteur asynchrone modulo 10 à l’aide de bascules JK activent sur front montant.

1. Réaliser le schéma permettant de réaliser ce compteur

2. Tracer les chronogrammes des sorties Q0, Q1, Q2, Q3 et Raz (à l’état initial, Q0=Q1=Q2=Q3= "0").

3. Convertir en décimal les quatre bits binaires Q3, Q2, Q1 et Q0 en prenant Q0 pour bit de poids faible.

Exercices logique séquentielle – V1.31 11/30

Lycée Jules Ferry – Versailles - 2007 -

10 FONCTION "DIVISION DE FREQUENCE".

Le schéma structurel est réalisé à partir du circuit logique HEF4027B

Schéma structurel.

Le circuit U2 est alimenté sous 0/5V

1. Il vous appartient de câbler les broches repérées S et R de façon à inhiber la "mise à un" et à

effectuer une "remise à zéro" de la sortie Us dès la mise sous tension du circuit. On utilisera le

signal RAZ (cf chronogrammes).

Conditions initiales:

- la sortie Q de U2a est au niveau bas,

- la sortie Q de U2b est au niveau bas.

2. Sachant que Ucad est une ddp logique 0/5V de fréquence F=10KHz, représenter les

chronogrammes des grandeurs J , K, Q et Q (chronogrammes en page suivante) pour les deux

bascules JK, mettant en évidence le fonctionnement de la structure. Et ceci pour 9 périodes de

Ucad.

3. Déterminer la fréquence du signal de sortie, et préciser la division effectuée.

Exercices logique séquentielle – V1.31 12/30

Lycée Jules Ferry – Versailles - 2007 -

Ucad

1

t

0

RAZ

1

t

0

Qa 1

t

0

Qa

1

t

0

Qb/Us

1

t

0

Qb

1

0 t

Exercices logique séquentielle – V1.31 13/30

Lycée Jules Ferry – Versailles - 2007 -

11 FONCTION ASYNCHRONE A BASCULE JK.

Le schéma structurel est réalisé à partir du circuit logique HEF4027B

Schéma structurel.

1J Q1 Q1 1J Q2

JE

C1 1K C1 1K

C

KE Q2

Tracer les chronogrammes des sorties Q1 et Q2.

JE 1

0 t

tttt

KE 1

0

C 1

0

Q1 1

0

Q2 1

0

0

4 8 12 16 20 24 28 32 36 40 44 48 52 56 µs

Exercices logique séquentielle – V1.31 14/30

Lycée Jules Ferry – Versailles - 2007 -

12 ETUDE D’UN COMPTEUR BINAIRE.

Symbole :

1. En exploitant sa table de vérité ou sa représentation détermine :

l’entrée et l’événement provoquant sa mise à zéro ;

l’entrée et l’événement provoquant le comptage ;

le modulo du comptage ;

le nombre mini possible en sortie ;

le nombre maxi possible en sortie.

2. Compléter les chronogrammes suivants :

Exercices logique séquentielle – V1.31 15/30

Lycée Jules Ferry – Versailles - 2007 -

H 1 t

0

RAZ 1 tt

0 tt

Q0 1 tt

Q1 10 ttt

tt

0 tt

Q2 1

Q3 10 t

0

Q4 1

Q5 10

0

Q6 1

Q7 10

0

Q8 1

0

Q9 1

0

Q10

1

Q11

1

?

NHD

4 8 12 16 20 24 28 32 36 40 44 48 52 56 ms

Exercices logique séquentielle – V1.31 16/30

Lycée Jules Ferry – Versailles - 2007 -

13 ETUDE DE COMPTEURS .

Symboles :

1. Pour chacun des composants représentés c-dessous, déterminer :

l’entrée et l’événement (0, 1 ou ) provoquant leur mise à zéro ;

l’entrée et l’événement provoquant le comptage ;

et le modulo de comptage.

2. Compléter les chronogrammes

suivants Procédure :

- En faisant attention aux événements de mise à zéro (RAZ) compléter le

chronogramme du nombre de sortie NO.

- En déduire l'état de chaque ligne de sortie du compteur

Exercices logique séquentielle – V1.31 17/30

Lycée Jules Ferry – Versailles - 2007 -

CP0 1 t

0

MR 1 tt

0 tt

t

NOD

?

O0 1

451

0

8

O1 1

0

O2 1

0

O3 1

0 t

0 4 8 12 16 20 24 28 32 36 40 44 48 52 56

ms

CP0 1 t

0

MR 1 tt

0 t

tt

NOD

452

O0 1

0

0

O1 1

O2 1 0

0

O3 1

0

t

0

4 8 12 16 20 24 28 32 36 40 44 48 52 56

ms

Exercices logique séquentielle – V1.31 18/30

Lycée Jules Ferry – Versailles - 2007 -

14 ASSOCIATIONS DE COMPTEURS MODULO 10.

Schéma structurel. Travail demandé : tracer les

chronogrammes ci-dessous

/CP1 1 t

0

MR 1

0 t

NU10 t

3

U0 1

t

0

U1 1

t

0

U2 1

t

0

U3 1

0 t

ND10 t

4

D0 1

t

0

D1 1

t

0

D2 1

t

0

D3 1

0 t

N10

t

4

0

4 8 12 16 20 24 28 32 36 40 44 48 52 56 ms

Exercices logique séquentielle – V1.31 19/30

Lycée Jules Ferry – Versailles - 2007 -

15 FONCTION "COMPTEUR A MODULO DEFINI PAR CABLAGE".

Schéma structurel.

Le schéma ci-dessus est celui d’un compteur dont le modulo est déterminé par câblage

1. Pour IC1, déterminer :

l’entrée et l’événement provoquant le comptage ;

l’entrée et l’événement provoquant la mise à zéro de son contenu.

2. Déterminer la première valeur du contenu remettant à zéro le compteur.

3. Enoncer la succession de nombres stables produits par ce compteur.

4. Compléter les chronogrammes sur la page suivante

5. Proposer un nouveau câblage afin d’obtenir une fonction comptage modulo 12. Enoncer la

suite des nombres stables produits par cette structure.

Exercices logique séquentielle – V1.31 20/30

Lycée Jules Ferry – Versailles - 2007 -

H1

0 t

N .

CT0 1

0

CT1 1

0

CT2 1

0

CT3 1

0

R1

0

0 4

8 12 16 20 24 28 32 36 40 44 48 52 56 ms

Exercices logique séquentielle – V1.31 21/30

Lycée Jules Ferry – Versailles - 2007 -

16 ETUDE D’UN COMPTEUR-DECOMPTEUR A PRECHARGEMENT.

Symbole :

1. En exploitant sa table de vérité ou sa représentation détermine :

l’entrée et l’événement provoquant sa mise à zéro ;

l’entrée et l’événement provoquant le comptage ;

l’entrée et l’événement provoquant le décomptage ;

le modulo du décomptage et du comptage ;

l’entrée et l’événement provoquant le préchargement ;

les entrées de données pour le préchargement ;

la condition pour que RINC soit actif et l’état associé ;

la condition pour que RDEC soit actif et l’état associé.

2. Compléter les chronogrammes des deux pages suivantes :

Exercices logique séquentielle – V1.31 22/30

Lycée Jules Ferry – Versailles - 2007 -

RAZ 1

t

0

HINC 1

t

0

HDEC 1 t

0

CHARGE 1

t

0

NQD t

?

Q0 1

t

0

Q1 1

t

0

Q2 1

t

0

Q3 1

0 t

RINC 1

t

0

RDEC 1

0 t

0 4 8 12 16 20 24 28 32 36 40 44 48 ms

Exercices logique séquentielle – V1.31 23/30

Lycée Jules Ferry – Versailles - 2007 -

RAZ 1

t

0

HINC 1

t

0

HDEC 1 t

0

CHARGE 1

0 t

?

NQD t

Q0 1

t

0

Q1 1

t

0

Q2 1

t

0

Q3 1

0 t

RINC 1

t

0

RDEC 1

0 t

48 52 56 60 64 68 72 76 80 84 88 92 96 100 104 ms

Exercices logique séquentielle – V1.31 24/30

Lycée Jules Ferry – Versailles - 2007 -

17 COMPARER DES CHRONOGRAMMES SYNCHRONES ET ASYNCHRONES.

Schéma structurel.

Voici une structure de comptage. Le compteur 74163a est un compteur synchrone, le 74393 est un

compteur asynchrone. Vous allez construire les chronogrammes de l'un et de l'autre suivant les procédés

respectifs de chacun de ces compteurs. Ils sont tous deux commandés par le même signal de commande H, le

comptage est donc simultané. Ainsi vous pourrez vous rendre compte de la différence entre les deux modes

de fonctionnement.

Procédure :

- Construire le premier chronogramme comme vous en avez l'habitude (H est commun)

Le deuxième chronogramme dilate l'échelle de temps au voisinage de t=32ms du premier chronogramme. À cette échelle vous ne

pourrez pas négliger les temps de propagation de l'information dans les opérateurs. Pour simplifier vous considérerez qu'un temps

de propagation TP vaut 15ns.

- Les quatre sorties de l ' o p é r a t e u r synchrone sont toutes c o m m a n d é e s par H. Construire le

chronogramme de ces sorties en considérant un TP entre de H et chaque transition de sortie.

- L a s o r t i e AS0 de l ' o p é r a t e u r a s y n c h r o n e est c o m m a n d é e par d e H . Construire le

chronogramme de AS0 en considérant un TP entre de H et transition de AS0. La sortie AS1 est

commandée par de AS0, un TP doit donc s'écouler entre ces deux événements. Vous procéderez

ainsi aussi pour les sorties AS2 et AS3.

- Représenter chaque TP par une flèche de couleur. (voir exemple)

- Déterminer pour chaque instant (même pendant les transitions) les valeurs de S et AS.

Exercices logique séquentielle – V1.31 25/30

Lycée Jules Ferry – Versailles - 2007 -

H1 H1 t

t

0 0

/RAZ 1 /RAZ 1

0 0

S0 1 S0 1

0 0

S1 1 S1 1

0 0

S2 1 S2 1

0 0

S3 1 S3 1

0 0

8

S .

S .

AS0 1 AS0 1

0 0

AS1 1 AS1 1

0 0

AS2 1 AS2 1

0 0

AS3 1 AS3 1

0 0

8

AS .

AS .

16 20 24 28 32 36 40 ms 31,980 32,000 32,020 32,040 32,060 32,080 32,100 ms

Exercices logique séquentielle – V1.31 26/30

Lycée Jules Ferry – Versailles - 2007 -

18 ANNEXE

HEF4518B Dual BCD counter

FUNCTION TABLE

CP0 CP1 MR MODE

H L counter advances

L L counter advances

X L no change

X L no change

L L no change

H L no change

X X H O0 to O3 = LOW

74HC/HCT393 Dual 4-bit binary ripple counter

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 13 1CP, 2CP clock inputs (HIGH-to-LOW, edge-triggered)

2, 12 1MR, 2MR asynchronous master reset inputs (active HIGH)

3, 4, 5, 6, 1Q0 to 1Q3, flip-flop outputs

11, 10, 9, 8 2Q0 to 2Q3

7 GND ground (0 V)

14 VCC positive supply voltage

Exercices logique séquentielle – V1.31 27/30

Lycée Jules Ferry – Versailles - 2007 -

74HC/HCT193 Presettable synchronous 4-bit binary up/down counter

FUNCTION TABLE

INPUTS OUTPUTS

MR /PL CPU CPD D0 D1 D2 D3 Q0 Q1 Q2 Q3 /TCU /TCD

OPERATING MODE 14 11 5 4 15 1 10 9 3 2 6 7 12 13

H X X L X X X X L L L L H L

reset (clear)

H X X H L L H H

X X X X L L

L L X L L L L L L L L L H L

X H L L L L L L L L H H

parallel load

L L L X H H H H H H H H L H

H X H H H H H H H H H H

L L

L L

count up L H H X X X X count up H H

count down L H H X X X X count down H H

Exercices logique séquentielle – V1.31 28/30

Lycée Jules Ferry – Versailles - 2007 -

74HC/HCT4040 12-stage binary ripple counter

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

8 GND ground (0 V)

9, 7, 6, 5, 3, 2, 4, 13, 12, 14, 15, 1 Q0 to Q11 parallel outputs

10 CP clock input (HIGH-to-LOW, edge-triggered)

11 MR master reset input (active HIGH)

16 VCC positive supply voltage

FUNCTION TABLE

INPUTS OUTPUTS

CP MR Qn

L no change

L count

X H L

Timing diagram:

Exercices logique séquentielle – V1.31 29/30

Lycée Jules Ferry – Versailles - 2007 -

74HC/HCT163 Presettable synchronous 4-bit binary counter

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1 MR synchronous master reset (active LOW)

2 CP clock input (LOW-to-HIGH, edge-triggered)

3, 4, 5, 6 D0 to D3 data inputs

7 CEP count enable input

8 GND ground (0 V)

9 PE parallel enable input (active LOW)

10 CET count enable carry input

14, 13, 12, 11 Q0 to Q3 flip-flop outputs

15 TC terminal count output

16 VCC positive supply voltage

FUNCTION TABLE

INPUTS OUTPUTS

OPERATING MODE MR CP CEP CET PE Dn Qn TC

reset (clear) L X X X X L L

H X X L L L L

parallel load

H L H H (1)

X X

count H H H L X count (1)

hold H X L X H X qn (1)

(do nothing) H X X L H X qn L

(1) The TC output is HIGH when CET is HIGH and the counter is at terminal count (HHHH).

Exercices logique séquentielle – V1.31 30/30

Lycée Jules Ferry – Versailles - 2007 -

Vous aimerez peut-être aussi

- Aide Memoire Tuyauterie - CompletDocument62 pagesAide Memoire Tuyauterie - CompletMars7695% (121)

- Il Faut Que Je Sois ParfaitDocument111 pagesIl Faut Que Je Sois ParfaitlynxnetPas encore d'évaluation

- Programmation Didactique - Concours 10Document55 pagesProgrammation Didactique - Concours 10Miguel92% (13)

- CI05 TD13 Corrigé - Déterminer Le Modèle de Connaissance D - Un Système AsserviDocument4 pagesCI05 TD13 Corrigé - Déterminer Le Modèle de Connaissance D - Un Système AsserviKhaled JberiPas encore d'évaluation

- 3 - Rapport Sukuk Final PDFDocument28 pages3 - Rapport Sukuk Final PDFOussama Derwich100% (2)

- Exercice de Logique Sequentielle PDFDocument30 pagesExercice de Logique Sequentielle PDFmohcenPas encore d'évaluation

- Exercice de Logique SequentielleDocument30 pagesExercice de Logique SequentielleMidox MidoPas encore d'évaluation

- Fractionné 20231218 0441Document28 pagesFractionné 20231218 0441Black BleachPas encore d'évaluation

- Chap 08Document8 pagesChap 08Enidroun OutPas encore d'évaluation

- Chap 3 Les CompteursDocument10 pagesChap 3 Les CompteursAhmed BelhadjPas encore d'évaluation

- Correction de La Série 2-ConvertiDocument6 pagesCorrection de La Série 2-ConvertiLaataoui OnsPas encore d'évaluation

- Chapitre 1 - Rappel Sur Les Circuits SéquentielsDocument18 pagesChapitre 1 - Rappel Sur Les Circuits SéquentielsTtech hackPas encore d'évaluation

- Circuits Séquentiels Bascules Et CompteurDocument10 pagesCircuits Séquentiels Bascules Et Compteurhicham_barakatePas encore d'évaluation

- 2008 - 3 - Logique SequentiellerDocument17 pages2008 - 3 - Logique SequentiellerfieeaPas encore d'évaluation

- Circuits Sc3a9quentiels BasculesDocument4 pagesCircuits Sc3a9quentiels BasculesJérémie DansouPas encore d'évaluation

- 05 TD #5 Num SEI 2 - ITES + CORDocument5 pages05 TD #5 Num SEI 2 - ITES + CORchrist saiPas encore d'évaluation

- 2012 2013 ExamenDocument4 pages2012 2013 ExamenFadelPas encore d'évaluation

- Circuits Csequentiels Partie1Document36 pagesCircuits Csequentiels Partie1Nidal LaatabPas encore d'évaluation

- Logique SequentielleDocument28 pagesLogique SequentielleIkram ElaimaPas encore d'évaluation

- Upload-Série D'exercices N°6-3tech-Compteurs Synchrones-2013-2014Document3 pagesUpload-Série D'exercices N°6-3tech-Compteurs Synchrones-2013-2014Habib TrikiPas encore d'évaluation

- TD E Logique Sequentielle Fonction MemorisationDocument3 pagesTD E Logique Sequentielle Fonction MemorisationYoussef ElalaouiPas encore d'évaluation

- TD2 S 4 LPEEI2020 VFDocument3 pagesTD2 S 4 LPEEI2020 VFELMEHDI CHOUINEPas encore d'évaluation

- Regimes Libres de L Oscillateur Harmonique ExercicesDocument3 pagesRegimes Libres de L Oscillateur Harmonique ExercicesIthiel MelchisedecPas encore d'évaluation

- Circuits SéquentielDocument27 pagesCircuits SéquentielasmaPas encore d'évaluation

- PDF Compteur PDFDocument12 pagesPDF Compteur PDFThe geek CuestaPas encore d'évaluation

- Corrigé Du TD2: N-1barDocument3 pagesCorrigé Du TD2: N-1barELMEHDI CHOUINEPas encore d'évaluation

- Bascule CRDocument5 pagesBascule CRAbderrazak MiassarPas encore d'évaluation

- Chap2-Circuits Séquentiels PDFDocument29 pagesChap2-Circuits Séquentiels PDFaymen houchePas encore d'évaluation

- Bascules SynchronesDocument7 pagesBascules SynchronesMohamed Ben FredjPas encore d'évaluation

- FlogiqueDocument9 pagesFlogiqueSamir abidiPas encore d'évaluation

- 4-Régime TransitoireDocument14 pages4-Régime Transitoirenada chbiki100% (1)

- Régime transitoireDocument3 pagesRégime transitoireyouness.rqiqqPas encore d'évaluation

- Ch10 CI11 I11 SequentielleDocument8 pagesCh10 CI11 I11 Sequentiellecpommier100% (1)

- Fascicule TP SYSTEME LOGIQUE 2 V2018Document32 pagesFascicule TP SYSTEME LOGIQUE 2 V2018Gharby Nour ElhoudaPas encore d'évaluation

- Systeme Sequentiels Eleve-CompteursDocument3 pagesSysteme Sequentiels Eleve-CompteursAhmed BelhadjPas encore d'évaluation

- 13 BasculesDocument5 pages13 BasculesZakaria GhazizPas encore d'évaluation

- Bascule SDocument15 pagesBascule SManar BouPas encore d'évaluation

- Série Corrigée Sur Les Compteurs À Base de BasculeDocument17 pagesSérie Corrigée Sur Les Compteurs À Base de BasculeMootaz RahalPas encore d'évaluation

- Série D'exercices N°3-3tech-Bascules-Compteurs-2012-2013-CorrectionDocument10 pagesSérie D'exercices N°3-3tech-Bascules-Compteurs-2012-2013-CorrectionMustapha LibourkiPas encore d'évaluation

- Fonction Exponentielle CoursDocument9 pagesFonction Exponentielle Courssuper starPas encore d'évaluation

- TP6 GFDocument3 pagesTP6 GFMohamed HeraouaPas encore d'évaluation

- Etude Du Circuit NE 555Document10 pagesEtude Du Circuit NE 555codety CODETYPas encore d'évaluation

- TD2 Module P514 A.U. 2015/2016Document6 pagesTD2 Module P514 A.U. 2015/2016OUMAIMA LAMAAMARPas encore d'évaluation

- Série Compteur À Base de BasculeDocument8 pagesSérie Compteur À Base de BasculemelekkanounPas encore d'évaluation

- Resume Oscillations Libres Dun Circuit RLCDocument1 pageResume Oscillations Libres Dun Circuit RLCsh ChaiPas encore d'évaluation

- BKMADocument7 pagesBKMANourou ABDOULAZIZPas encore d'évaluation

- Fiche TD 2Document2 pagesFiche TD 2baboucarbadji221Pas encore d'évaluation

- Manuel ProfesseurDocument17 pagesManuel Professeurnouredine akliPas encore d'évaluation

- Elecseq 1Document20 pagesElecseq 1Daniel King-zockPas encore d'évaluation

- Chap6 Les Bascules PDFDocument8 pagesChap6 Les Bascules PDFDěmøïšěllë RãnPas encore d'évaluation

- CIRA1 - 3) Logique Sequentielle PDFDocument7 pagesCIRA1 - 3) Logique Sequentielle PDFLANGO RICHARD BAMBAPas encore d'évaluation

- Chap1 PDFDocument15 pagesChap1 PDFHanane AmzilPas encore d'évaluation

- Seìquentiel 1Document100 pagesSeìquentiel 1Aicha LahnoukiPas encore d'évaluation

- Corrige TD06 PDFDocument4 pagesCorrige TD06 PDFabdelgoui rymPas encore d'évaluation

- Upload - Série D'exercices N°6-3tech-Compteurs Synchrones-2013-2014Document3 pagesUpload - Série D'exercices N°6-3tech-Compteurs Synchrones-2013-2014Hayet BechedliPas encore d'évaluation

- Td2 Avec Corrige PartielDocument11 pagesTd2 Avec Corrige PartielelomaniparoPas encore d'évaluation

- Wa0018.Document4 pagesWa0018.ffghjhkkPas encore d'évaluation

- Chapitre III Circuits Séquentiels 4x1Document26 pagesChapitre III Circuits Séquentiels 4x1wafa wafaPas encore d'évaluation

- TP4-DE-LCS ChelloufDocument9 pagesTP4-DE-LCS ChelloufIslam CHELLOUF100% (1)

- cours xx astable et monostable serge bettiniDocument8 pagescours xx astable et monostable serge bettiniouedraogojunior017Pas encore d'évaluation

- Upload - Série D'exercices N°3-3tech-Bascules-Compteurs-2012-2013Document9 pagesUpload - Série D'exercices N°3-3tech-Bascules-Compteurs-2012-2013Chadi Ezzine100% (1)

- TD 33 - Systèmes Séquentiels - Fonction MémoireDocument2 pagesTD 33 - Systèmes Séquentiels - Fonction Mémoirebhs channel0% (1)

- Chapitre 4 Les Compteurs Et Décompteurs Asynchrones Partie 1Document12 pagesChapitre 4 Les Compteurs Et Décompteurs Asynchrones Partie 1mohamed ben slimanePas encore d'évaluation

- SolfegeDocument24 pagesSolfegeDodaPas encore d'évaluation

- Guide Des Associations 2020 21Document88 pagesGuide Des Associations 2020 21David Avishaï CohenPas encore d'évaluation

- Mobiscript 3Document77 pagesMobiscript 3wukzPas encore d'évaluation

- Brochure SOBANE Incendie - FRDocument144 pagesBrochure SOBANE Incendie - FRLarmes de SangPas encore d'évaluation

- LM Linear Range 12774 FRDocument248 pagesLM Linear Range 12774 FRAhmed MezniPas encore d'évaluation

- Ifu - Lettre DgiDocument9 pagesIfu - Lettre Dgicomptabilité financière approfondiePas encore d'évaluation

- MTTH 4Document1 pageMTTH 4Anas MenoirPas encore d'évaluation

- (CFT) Memento PDFDocument6 pages(CFT) Memento PDFlacoste123Pas encore d'évaluation

- L'Etat de Nature Chez Thomas HobbesDocument10 pagesL'Etat de Nature Chez Thomas HobbesDenisa Elena FocaruPas encore d'évaluation

- Les Obstacles A La CommunicationDocument3 pagesLes Obstacles A La CommunicationSissou Bello100% (2)

- Certificat Informatique & Internet - Guide de L'apprenantDocument6 pagesCertificat Informatique & Internet - Guide de L'apprenantKhadidiatou DialloPas encore d'évaluation

- 9 - Cours 9 Applications Industrielles Du Laser AggrandiDocument4 pages9 - Cours 9 Applications Industrielles Du Laser AggrandiLokman HamzaPas encore d'évaluation

- Atd BasketballDocument20 pagesAtd BasketballelhanyPas encore d'évaluation

- STA201 - Equations Structurelles - 1 - JakobowiczDocument65 pagesSTA201 - Equations Structurelles - 1 - JakobowicztchamPas encore d'évaluation

- Devoir de Controle +Liaisons+MécaniquesN2 1AS 2021Document4 pagesDevoir de Controle +Liaisons+MécaniquesN2 1AS 2021Razan KhPas encore d'évaluation

- Cours HDD ASSASNETDocument91 pagesCours HDD ASSASNETAlyssa PeixotoPas encore d'évaluation

- Partie II La Théorie Du Comportement de ConsommateurDocument77 pagesPartie II La Théorie Du Comportement de ConsommateuressalkagarmounePas encore d'évaluation

- Système CW de LiebertDocument86 pagesSystème CW de LiebertJavier LunaPas encore d'évaluation

- Bertrand Russell Théorie de La Connaissance - Le Manuscrit de 1913Document3 pagesBertrand Russell Théorie de La Connaissance - Le Manuscrit de 1913Ahmed KabilPas encore d'évaluation

- Placard de Recrutement ATS FRDocument7 pagesPlacard de Recrutement ATS FRMarass-Tech AgadezPas encore d'évaluation

- Cas - Pratique - Conduite - Du - Changement - Jean-FrançoisDocument3 pagesCas - Pratique - Conduite - Du - Changement - Jean-FrançoisFérielPas encore d'évaluation

- Jeu de L'oie Épisode 3Document5 pagesJeu de L'oie Épisode 3Mery MeryPas encore d'évaluation

- CV Afiatou ToeDocument1 pageCV Afiatou ToeFranck AbPas encore d'évaluation

- PompageDocument14 pagesPompagewithe animalsPas encore d'évaluation

- Fiche Oral TEXTE 3 - Paysage, BaudelaireDocument2 pagesFiche Oral TEXTE 3 - Paysage, BaudelaireLola bricotPas encore d'évaluation

- René Et Julien Sorel Ambition Et MélancolieDocument0 pageRené Et Julien Sorel Ambition Et MélancolieayouzyouftnPas encore d'évaluation