Académique Documents

Professionnel Documents

Culture Documents

Les Circuits Arithmetiques

Transféré par

Nejib JallouliTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Les Circuits Arithmetiques

Transféré par

Nejib JallouliDroits d'auteur :

Formats disponibles

LES OPERATIONS ARITHMETIQUES BINAIRES

I- REPRÉSENTATIONS DES NOMBRES EN BINAIRES

Un nombre binaire peut être soit ………………. Soit ……………, ainsi on écrit:

+ 7(10) = + 1 1 1(2) ; + 12(10) = + 1 1 0 0(2) ; - 7(10) = - 1 1 1(2) et - 12(10) = - 1 1 0 0(2)

mais cette représentation ne peut pas être traitée par les systèmes informatiques qui ne reconnaissent

certainement pas les signes + et – (les systèmes informatiques n'utilisent que les 0 et les 1).

I-1 Binaire signé:

On réserve le bit du plus fort poids pour le signe. Par convention, le plus (+) sera représenté par …….

alors que le moins (-) par ………….. Ce ci exige la définition d'un ………………… de représentation

qui est le nombre de bits réservés à l'écriture du nombre binaire désiré.

Exemples: Ecrire les nombres suivants en binaire signé sur un format de:

4 bits (quartet) ; Remarque:

8 bits (octet)

+5 avec un format de …. bits, on a uniquement

-5 ……. bits utiles. Ainsi avec 8 bits on ne peut

+ 12 coder que les équivalents décimaux de +127

- 13 et -127

I-2 complément à 2

Le codage par complémentation est très utilisé car il permet de transformer une ………………… en

une …………………. Pour bien en comprendre le principe, on va auparavant définir ce que sont les

………………………. et à …….

On forme le complément à 1 (ou complément restreint) d'un nombre binaire en complémentant un à

un ( en changeant tous les zéros en uns, et tous les uns en zéros). Par exemple:

Le complément à 1 de 100110 est ………………………

Le complément à 1 de 11101 est ………………………..

Cette opération s'obtient par des simples inverseurs logiques. La figure suivante donne l'exemple à 3 bits.

a0 a0

a1 a1

A A

a2 a2

Le complément à 2 ( ou complément vrai) d'un nombre binaire s'obtient en ajoutant ….. au

complément restreint: ainsi

Le complément à 2 de 100110 est 011001

Le complément à 2 de 11101 est 00010

Comme pour le binaire signé le complément à 2 doit utiliser un format prédéfini.

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:1

Les compléments à 1 et à 2 offrent un autre moyen pour coder les nombres binaires négatifs comme le

montre le tableau ci-dessous où l'on retrouve le bit de signe. On utilise un format de 8 bits (octet).

Valeur Binaire Complément Complément

décimal absolue plus signé à1 à2

signe

+ 255 1111 1111 Ipossible Ipossible Ipossible

+ 128 1000 0000 Ipossible Ipossible Ipossible

+ 127 0111 1111 0111 1111 0111 1111 0111 1111

+1 0000 0001 0000 0001 0000 0001 0000 0001

+0 0000 0000 0000 0000 0000 0000 0000 0000

-0 -0000 0000 1000 0000 1111 1111 0000 0000

-1 -0000 0001 1000 0001 1111 1110 1111 1111

-2 -0000 0010 1000 0010 1111 1101 1111 1110

- 127 -0111 1111 1111 1111 1000 0000 1000 0001

- 128 -1000 0000 Ipossible Ipossible 1000 0000

- 255 -1111 1111 Ipossible Ipossible Ipossible

II- LES ADDITIONNEURS :

1- Principe Ce tableau est à la base de la conception

La table d’addition binaire est d’un additionneur. En effet une opération

d’addition donne une somme S et une

0 + 0 = 0

retenue R

0 + 1 = 1

La table de vérité d’un additionneur

1 + 0 = 1

élémentaire est la suivante.

1 + 1 = 0 On écrit « 0 » et on retient « 1 »

Exemples

1 0 0 1 0 1 1 0 1 1 1 1 0 1 1

1 1 0 1 0 1 1 0 1 1 1

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:2

2- Table de vérité d’un additionneur élémentaire ( demi additionneur ou Half adder )

Un demi additionneur est circuit qui réalise l’addition de deux nombres binaires ………….. chacun.

Table de vérité 3- Logigramme

½ ADD abSR00011011 S=

Half ADD

R=

3- Additionneur complet ( full adder)

Il permet l’addition de trois bits. En effet pour additionner deux nombres on additionne les bits de

………………………………. tout en tenant compte de la …………….. du rang précédant . La

modélisation d’un additionneur de rang « n » ou additionneur complet est le suivant

3-3 Equations simplifiées

3-1 Modélisation 3-2 Table de vérité

bn an bn an Rn Sn Rn+1 0001111001

0 0 0

Additionneur 0 0 1

complet 0 1 0

Rn+1 Full ADD Rn 0 1 1 S

1 0 0

1 0 1 0001111001

Sn 1 1 0

1 1 1

Rn+1

Sn =

Rn+1 =

an

Sn

bn

Rn+1

Rn

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:3

3-4 Exemple d’application : Addition de deux nombres à 6 bits

b5 a5 b4 a4 b3 a3 b2 a2 b1 a1 b0 a0

R5 S5 S4 S3 S2 S1 S0

Cette structure simple et rapide à mettre en œuvre cache un inconvénient majeur. En effet, la

propagation du retenu (Rn) d'une étage à la suivante va retarder l'apparition du résultat final de

l'opération d’où le nom …………………………………………………..

Comme on a vu ci haut, une simple addition sur un octet demandera ….. opérations successives sur

des chiffres binaires, ce qui est jugé long.

3-5 Additionneur à anticipation de retenues

5-1 principe:

Ainsi soit à additionner:

Fractionnons donc ces nombres de 8 bits en tranches de 2 bits,

10111011 cumulande

qu'on additionne séparément en parallèle comme une première

+ 00001101 étape.

+ cumulateur

(D) (C) (B) (A)

= = somme 10 11 10 11

+ 00 00 11 01

=

retenue

En seconde étape, on va ajouter les retenues: celle de (A) à (B), puis celle de (B) à (C) où une nouvelle

retenue est générée vers (D). on obtient:

(D) (C) (B) (A) La 3e et dernière étape consiste donc à additionner

10 00 10 00 la deuxième retenue de (C) à (D), et on trouve en

fin: 1 1 0 0 1 0 0 0

retenue 2e niveau 1

Dans ce cas, si les 4 tranches de 2 bits ont été additionnées par 4 additionneurs en parallèle, il aura

suffit de 6 temps au lieu des 8 précédents.

Autrement dit, on doit calculer tous d'abord les retenues (R1 ,R2 , R3 et R4)

R1 = f( R0 , a0 et b0 ) , R2 = f(R0 , R1, a0 , b0 , a1 et b1) ; R3 = f( R0 , R1 , R2 , a0 b0 ………) et

ainsi de suite.

Le synoptique suivant illustre le principe de fonctionnement d'un tel additionneur

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:4

A0 B0 A1 B1 A3 B3

A2 B2

R0

Calcul de Calcul de Calcul de Calcul de

R1 R2 R3 R4

Calcul de Calcul de Calcul de Calcul de

S1 S2 S3 S4 R4

S1 S2 S3 S4

Synoptique d'un additionneur 4 bits à retenues anticipées

5-2 réalisation industielle:

Parmi les circuits intégrés additionneurs on peut citer:

7480 complet 1 bit 4008 complet 4 bits

7482 complet 2 bits 40 32 complet 3 bits

7483 complet 4 bits

74283 complet 4 bits

II-6 Addition en complément à 2:

Cas de deux nombre positifs

L'addition dans se cas est immédiate 0 0 1 1 1

Soit à additionner: (+7) et (+5) ; +7 = 0 0 1 1 1 ; +5 = 0 0 1 0 1

+ 0 0 1 0 1

=

Cas d'un nombre positif et un nombre négatif plus petit:

Dans ce cas le nombre positif sera remplacé par son équivalent binaire exact; alors que le nombre

négatif doit être remplacé par son complément à 2.

Soit à réaliser l'opération + 7 + (-5) ; sur 5 bit en aura:

+ 7 = 0 0 1 1 1 ; -5 = 1 0 1 0 1 ; le comlément à 2 de (-5) est :

On voit qu'il y a dépassement (résultat sur 6 bits); mais par contre sur 5 bits le résultat est :

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:5

Cas d'un nombre positif et un nombre négatif plus grand:

Calculons (-7) + (+5) : comme précédemment, le nombre négatif doit être …………………………

-7 = 1 0 1 1 1 ; +5 = 0 0 1 0 1 ; le complément à 2 de -7 est: 1 1 0 0 0 + 1 = 1 1 0 0 1

1 1 0 0 1 Le résultat est ………………. car le bit de signe est …..

+ 0 0 1 0 1 Pour trouver la valeur réelle de l'opération on doit calculer

= ………………………. du résultat à savoir :

Cas de deux nombres négatifs:

Il faut représenter les deux nombres par leurs équivalents en complément à 2 puis faire la

somme. Le résultat va être négatif et en complément à 2, pour reconstituer la valeur absolue

exacte du résultat il faut recomplémenter à 2 le résultat.

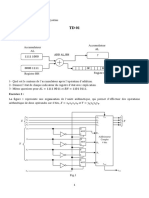

II-7 Association des additionneurs:

Soit à additionner 2 nombres à 8 bits chacun. On peut utiliser deux additionneurs à 4 bits ( p ex 7483)

A1 10 0 Σ 74 83 A1 5 0 Σ 74 283

A2 8 P 3

3 A2 P

A3 A3 14

1 9 Σ1 4

A4 3 0 A4 12 3 0 Σ1

6 Σ2 1

Σ 2 Σ Σ2 DIL 16

11 Σ3 6 13

B1

B2 7

0 15 Σ4 DIL 16 B1

2

0 10

Σ3

Vcc 16 GND 8

3 B2 Σ4

B3 4

Q Vcc 5 GND 12 B3 15

3

16 Q

B4 3 B4 11

13 14 C4 3 9

C0 C1 C0 C0 7 C4

C1 C0

B7 B6 B5 B4 B3 B2 B1 B0 A7 A6 A5 A4 A3 A2 A1 A0

13

16

4

7

11

1

3

8

10

13

16

4

7

11

1

3

8

10

74 83 74 83

14

15

2

6

9

14

15

2

6

9

S8 S0

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:6

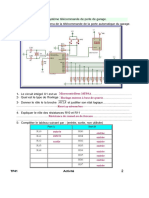

II-8 Additionneur BCD ( Décimal codé en binaire)

On a vu en troisième le code BCD dans lequel chaque chiffre du nombre décimal est codé en binaire

sur ………. En (BCD compacté) soit sur ……….. ( BCD étendu).

Ainsi les nombres décimaux: 2 5 8 = …………………….. 739 = ……………………

On remarque que un chiffre décimal est au maximum égal à ……….. soit en BCD ………… cette

règle doit être respectée. On ne peut donc pas additionner deux codes BCD dont la somme est ………..

Exepmles:

2 5 0010 0 1 0 1 7 9 0 1 11 1 0 0 1

+ 43 010 0 0 0 1 1 + 6 4 0 1 1 0 0 1 0 0

= =

On voit que le résultat de l'opération (79 + 64) est incorrect puisque les chiffres codés sur 4 bits sont:

Pour remédier à ce problème, on procède comme suit:

Chaque fois que le résultat d'un quartet est ………………… on lui ajoute ……………… pour trouver

la transcription en BCD de ce résultat

Reprenons l'exemple précédent:

7 9 0 1 1 1 1 0 0 1 5 3 0 1 0 1 0 0 1 1

+ 6 4 0 1 1 0 0 1 0 0 + 8 2 1 0 0 0 0 0 1 0

= 1 1 0 1 1 1 0 1 =

III- MUTIPLICATIONS OU PRODUITS EN BINAIRES

III-1 Principe

On procède comme en décimal:

Une multiplication par ……. Donne un résultat …….

Une multiplication par ……. entraîne la recopie du multiplicande.

Un décalage à gauche est à réaliser en passant d'un rang au rang supérieur

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:7

La table de la multiplication est la suivante:

Table de vérité

Exemples: calculer en binaire: 3910 x 510 = 19510

abSR00011011

Mutipli-

cateur

3910 = 1 0 0 1 1 1

510 = 1 0 1

S=

R=

III-2 Réalisation industrielle:

On cherche à réaliser un circuit électronique permettant de multiplier deux nombre binaire A et B de

deux bit chacun. Soit A =(a1 a0) et B= (b1 b0)

Le résultat de l'opération prend la forme ci-dessous:

Les composants nécessaires pour une réalisation

A a1 a0 pratique sont:

B b1 b0 Résultat Composants nécessaires

C0

= b0.a1 b0.a0 C1

C2

b1.a1 b1.a0

C3

D'où le logigramme du multiplicateur binaire à 2 bits.

& C0

a0

a1 &

Half C1

Adder

&

b0

b1 & Half C2

Adder

C3

Faire les avtivités 7 et 8 du manuels d'activités

IV LA SOUSTRACTION EN BINAIRE

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:8

IV – 1 principe

La table de la soustraction en binaire est la suivante où D est différence et R le report

Table de vérité D=

Sous- a b R D

tracteur 0 0 R=

0 1

1 0

1 1 Exemples: calculer en binaire: 3310 - 2310 = 1010

3310 = 1 0 0 0 0 1

2310 = 1 0 1 1 1

Reports

On peut ainsi tracer le logigramme d'un …………………………………….

Activité N° 1 TPA12

Un demi-soustracteur est un circuit logique permettent de calculer la différence entre deux nombres

binaires d'……………………….. il permet de générer une différence D et report R.

IV- 2 Soustracteur complet Activité N° 2 TPA12

comme le cas pour un additionneur, le soustracteur complet doit être capable de traiter ………………..

à savoir: le bit soustrait (an) , le bit soustracteur (bn) et le bit de report ou d'empreint(Rn). Il génère les

sorties Dn et Rn+1. Sa table de vérité est la suivante:

2- Equations simplifiées

1- Table de vérité

0001111001 Dn

an bn Rn Dn Rn+1

0 0 0

0 0 1

0 1 0

0 1 1 Rn+1

0001111001

1 0 0

1 0 1

1 1 0

1 1 1

La fonction XOR est ……………………………. C'est-à-dire ………………………………………..

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:9

bn.Rn an

00

01

11

En plus la sortie Rn+1 peut être grouper comme ci-contre. D'où

1001

Rn+1

Rn+1 = an . Rn + an . bn + bn . Rn = an . Rn + an . bn . Rn + an . bn . Rn

Le logigramme correspondant est:

IV-3 Soustraction en complément à 2:

Soit à effectuer (A – B), la marche à suivre pour réaliser cette opération est comme suit :

a/ prendre le complément à 2 de B, y compris le bit de signe

- Si B est positif, il devient négatif.

- Si B est négatif, sa complémentation à 2, en fera un nombre positif écrit en grandeur exacte.

Autrement dit, nous changeons le signe de B.

b/ Après complémentation à 2, on additionne l'ensemble (A conserve sa forme initiale). Le résultat

représente la différence recherchée. Le bit de signe de la différence, informe si la réponse est positive

ou négative et si on est en notation binaire exacte ou en notation en complément à 2.

NB : Les deux nombres doivent avoir le même nombre de bits.

V- LA DIVISION OU LE QUOTIENT BINAIRE

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:10

1/ Principe :

Le cheminement en vue de l’obtention du résultat est identique à celui de la division décimale.

La procédure pratique implique deux opérations :

la multiplication ou produit

la soustraction ou différence.

Ces opérations ont été déjà étudiées

Exemple :

Soit à diviser :

(11001000)2 = (200)10 par (101)2 = ( 5)10 (10110010)2 = (178)10 par (1101)2 = (13)10.

Remarque:

Lorsqu'un nombre représenté sur un format de bits subit:

un décalage à gauche: ………………………………………………………………

0 0 0 0 0 1 0 1 0 0 0 0 1 0 1 0 0 0 0 1 0 1 0 0

un décalage à droite: …………………………………………………………………

0 1 0 1 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 0 1 0 0

Des circuits spéciaux appelés ………………………………………. réalisent ces opérations.

VI- LES COMPARATEURS

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:11

1- Principe :

Il s’agit de définir une fonction logique permettant de comparer deux nombres binaires A et B et indiquer

en sortie si A=B , A>B ou A<B.

La comparaison doit commencer par le bit ……………………………………..

Exemple : Comparer les deux nombres décimaux A = 5783 et B = 5769

On pose A = a3 a2 a1 a0 et B = b3 b2 b1 b0 et comparons les digits de même rang.

A B Comparaison Commentaire

a3 = 5 b3 = 5

a2 = 7 b2 = 7

a1 = 8 b1 = 6

a0 = 3 b0 = 9

De la même façon en binaire on compare les bits de même rang pour pouvoir conclure en commençant

par les bits de plus fort poids.

Exemple : Comparer A = 1 0 1 1 et B = 1 0 1 0

A B Comparaison Commentaire

a3 = 1 b3 = 1

a2 = 0 b2 = 0

a1 = 1 b1 = 1

a0 = 1 b0 = 0

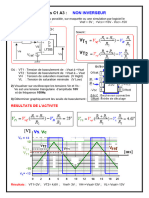

2- Comparateur de deux nombres a un bit 2-2 Table de vérité

2-1 principe :

a0 b0 S1 S2 S3

Remarque:

A = a0 S1 :(A > B)

Les trois sorties sont

S2 :(A = B)

……………….

B = b0 S3 :(A < B)

2-3 Simplification des équations

0 1 0 1 0 1

0 0 0

1 1 1

S1 S2 S3

2-4 Logigramme :

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:12

3- Comparateur de deux nombres à deux bits

3-1 Table de vérité:

a0b0 a0b0

a1 b1 a0 b0 S3 S2 S1 a1b10001111000011110 a1b10001111000011110

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0 a0b0 a0b0

1 0 1 1 a1b10001111000011110 a1b10001111000011110

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

Expression de S1 :

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:13

D’après le tableau de karnaugh correspondant à S1, on tire l’expression suivante :

S1 (A B) a 1 .a 0 .b1 .b 0 a 1 .a 0 .b1 .b 0 a 1 .a 0 .b1 .b 0 a 1 .a 0 .b1 .b 0

S1 a 1 .b1 .(a 0 .b 0 a 0 .b 0 ) a 1 .b1 .(a 0 .b 0 a 0 .b 0 )

S1 (a 1 .b1 a 1 .b1 ).(a 0 .b 0 a 0 .b 0 )

S1 (a 1 b1 ).(a 0 b 0 )

S1 (A B) (a 1 b1 ).(a 0 b 0 )

Expression de S2 :

D’après le tableau de karnaugh correspondant à S2, on tire l’expression suivante :

S2 ( A B ) a1 . b1 a0 . b0 .( a1 b1 )

Expression de S3 :

Chaque fois que (A = B) OU que (A > B), on n'aurait pas (A < B) ce qui permet d'écrire :

S3 = [NON(A = B)] ET [NON(A > B)] : S3 = S1 S2

Logigramme :

4- Comparateur de 2 nombres à 4bits:

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:14

Soit à comparer deux nombres binaires ayant chacun quatre bits :

A = a 3a 2a 1a 0

B = b 3 b 2 b 1 b 0 b3

a3 S2 = A B

MODELISATION b2

a2 comparer S2 = A B

b1

a1

b0

a0 S2 = A B

5 - Réalisation industrielle :

Industriellement le circuit intégres qui réalise cette fonction est le 7485 en technologie TTL et 4008 en

technologie CMOS.

les circuits intégrés suivants sont des comparateurs à 4 bits 4063 , 4585 7485 ,

les circuits intégrés 74683 …. 74689 sont des comparateurs à 8 bits

Exemples: circuit de comparaison de nombres à 4 bits avec le circuit 7485

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:15

de comparaison de 2 mots de 8 bits : ( 2 * 7485 )

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:16

VII- UNITE ARITHMETIQUE ET LOGIQUE (UAL)

1/ Présentation :

Le rôle de l'unité arithmétique et logique est de réaliser des opérations logiques et arithmétiques de base :

Opérations logiques bit à bit " ET, OU, NON, XOR…".

Opérations arithmétiques "addition, soustraction, complémentations à 1 ou à 2..."

Comparaisons

Décalages et rotations.

L'unité arithmétique et logique, dispose de :

Deux entrées A et B sur lesquelles on présente les données à traiter: "les opérandes".

Une sortie F donnant le résultat de l'opération effectuée.

Une entrée de Commande permettant la sélection de l'opération à effectuer.

Une sortie Etat donnant l'état de l'UAL après exécution de l'opération.

2- symbole général:

A B

Etat

Commande

3- constitution:

De part son nom, l'UAL peut être décomposée en deux grands blocs fictifs :

L'Unité Logique (UL), qui permet d'effectuer les opérations logiques

ET (AND), OU (OR), NON (NOT), OU exclusif (XOR), etc... sur deux mots de n bits placés

en entrées. Ces opérations sont effectuées bit à bit.

Exemple : Opérations Logiques sur deux mots de 4 bits

* Complémentation NOT (1 0 1 0) = ( )

* Produit logique (1 1 0 1) ET (1 0 1 1) = ( )

* Somme logique (1 0 0 1) OU (1011) = ( )

* Somme exclusive logique (1 1 0 1) ( 1 0 1 1) = ( )

L'Unité Arithmétique (UA), qui permet d'effectuer des opérations arithmétiques, telle que

l'addition et la soustraction sur 2 nombres de n bits placés en entrée.

Exemple : Opérations arithmétiques sur deux nombres de 4 bits

* Addition: (1011)+(1001) =

* Soustraction: (1011) - (1001) =

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:17

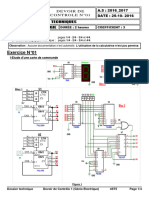

4- Principe de la réalisation d'une UAL:

Une UAL élémentaire peut combiner les fonctions de base suivante:

Opérateur Opérateur Opérateur Opérateur Additionneur Multiplexeur

NON ET OU XOR

ADD

(1) (2) (3) (4) (5) (6)

Exemples:

1- UAL 1 bits réalisants les fonctions (1) à (5).

Le multiplexeur est un …………………………… de fonction: c'est-à-dire il communique à sa sortie

l'une des fonctions présentes sur ses entrées. Pour se faire, il dispose d'une ou de plusieurs entrées de

commande (de sélection) dont les combinaisons lui permettent de sélectionner une entrée parmi

plusieurs. Comme l'UAL va réaliser ……………………, le multiplexeur aura besoins de ………………

……………. Ce qui lui permet d'avoir 4 combinaisons de commande.

S1 S0

a

Table de fonctionnement

S1S0Fonction de sortie F00011011

b

Le circuit ci-dessous illustre une réalisation réelle d'une telle UAL. Le multiplexeur étant un 74 151.

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:18

2- UAL à 1 bit utilisant les 6 fonctions du tableau ci-dessus:

S1 S0

a Table de fonctionnement

S1 S0 Fonction de sortie F

b 0 0

0 1

1 0

1 1

ADD

Cours 4ème TEC CIRCUITS ARITHMETIQUES page:19

Vous aimerez peut-être aussi

- Cahier: MathsDocument132 pagesCahier: MathsTOUFOULATI Mon enfance50% (2)

- 05 La Logique CombinatoireDocument59 pages05 La Logique CombinatoireAradPas encore d'évaluation

- 05 La Logique CombinatoireDocument59 pages05 La Logique CombinatoireAradPas encore d'évaluation

- TP2 ElectronériqueDocument10 pagesTP2 Electronériqueissam Mouissat100% (1)

- Addit 1174 PDFDocument11 pagesAddit 1174 PDFSimoBal-ghaouiPas encore d'évaluation

- Corrig TD1 2Document5 pagesCorrig TD1 2Amine Aissaoui100% (1)

- Division Décimale Et Euclidienne (6ème)Document3 pagesDivision Décimale Et Euclidienne (6ème)MATHS - VIDEOSPas encore d'évaluation

- Operations Arithmetiques BinairesDocument9 pagesOperations Arithmetiques BinairesNejib JallouliPas encore d'évaluation

- OPERATIONS ARITHMETIQUES BINAIRES Doc ElevDocument9 pagesOPERATIONS ARITHMETIQUES BINAIRES Doc ElevNejib JallouliPas encore d'évaluation

- Cours 2 4AMRI Circuits ProgrammablesDocument43 pagesCours 2 4AMRI Circuits ProgrammablesADIB HAMZAPas encore d'évaluation

- OPERATIONS ARITHMETIQUES BINAIRES Doc ProfDocument9 pagesOPERATIONS ARITHMETIQUES BINAIRES Doc ProfNejib JallouliPas encore d'évaluation

- A11 - Operations Arithmetiques BinairesDocument6 pagesA11 - Operations Arithmetiques BinairesAhmed BelhadjPas encore d'évaluation

- Addition Multiplication BinaireDocument9 pagesAddition Multiplication BinaireElmokh LassaadPas encore d'évaluation

- Chapitre 3Document15 pagesChapitre 3RABAB MASDOURPas encore d'évaluation

- TD1 MicroprocesseursDocument3 pagesTD1 MicroprocesseursYacine BoukiderPas encore d'évaluation

- 4 Etude Et Realisation D'un Circuit CombinatoireDocument15 pages4 Etude Et Realisation D'un Circuit CombinatoireReda Bou-abdallah100% (2)

- Logique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Document37 pagesLogique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Soufiane El AoufiPas encore d'évaluation

- Arithmetique BinaireDocument4 pagesArithmetique BinaireSamah AmeuriPas encore d'évaluation

- 1-Ch3-Cours EN-FSR-Amari-2020Document13 pages1-Ch3-Cours EN-FSR-Amari-2020Niels DrixPas encore d'évaluation

- Representation Des Donnees Dans La MachineDocument30 pagesRepresentation Des Donnees Dans La MachineHmida HamitiPas encore d'évaluation

- 03 - Représentation Des Entiers en MachineDocument4 pages03 - Représentation Des Entiers en MachineGoujiliPas encore d'évaluation

- 2 Codage PDFDocument7 pages2 Codage PDFlobnaPas encore d'évaluation

- CircuitscombinatoiresDocument44 pagesCircuitscombinatoiresAyoub ShaitPas encore d'évaluation

- Chapitre 1 2018Document12 pagesChapitre 1 2018OuagaPas encore d'évaluation

- Cu8ch SvsraDocument129 pagesCu8ch SvsraAngélica DEKEPas encore d'évaluation

- Presentation SuiteDocument20 pagesPresentation SuiteTalla NdiayePas encore d'évaluation

- Représentation Interne Des DonnéesDocument8 pagesReprésentation Interne Des DonnéesJCAPas encore d'évaluation

- J PortesDocument16 pagesJ PortesBOUCHEFFA HalimPas encore d'évaluation

- Cour 3Document7 pagesCour 3Samira HMPas encore d'évaluation

- Electro NumDocument25 pagesElectro NumrokiaPas encore d'évaluation

- Chapitre2 Cours (Part. 2) Circuits Combinatoires PDFDocument47 pagesChapitre2 Cours (Part. 2) Circuits Combinatoires PDFabdesslem0jarrayPas encore d'évaluation

- Chap6-Circuit ArithmetiquesDocument8 pagesChap6-Circuit ArithmetiquesAhmed Gourine100% (2)

- Cours 3 Les Opérations Arithmétiques Et LogiquesDocument14 pagesCours 3 Les Opérations Arithmétiques Et LogiquesRachida MebarkiPas encore d'évaluation

- OperationsDocument4 pagesOperationsNabila TouisiPas encore d'évaluation

- Cours Representation Entiers Au CMDocument3 pagesCours Representation Entiers Au CMnzalakandaguymydhaPas encore d'évaluation

- Chapitre 2 - Moodle - Partie1Document7 pagesChapitre 2 - Moodle - Partie1Amine OsmaniPas encore d'évaluation

- Chapitre 2 - Representation Des Nombres ReelDocument40 pagesChapitre 2 - Representation Des Nombres ReelSoufianeLinuxienPas encore d'évaluation

- TP - LCS - Séance 1Document1 pageTP - LCS - Séance 1hlm100% (2)

- Suite Chapitre 1 - Partie 2 - 021300Document17 pagesSuite Chapitre 1 - Partie 2 - 021300Hichem GuedriPas encore d'évaluation

- Chapitre 1 Systèmes de NumérationsDocument14 pagesChapitre 1 Systèmes de NumérationsFahmawi HakimPas encore d'évaluation

- Cours+ +Génie+Électrique+Addition+Et+Multiplication+Binaire+ +Bac+Technique+ (2012 2013) +Mr+AïssaDocument7 pagesCours+ +Génie+Électrique+Addition+Et+Multiplication+Binaire+ +Bac+Technique+ (2012 2013) +Mr+Aïssaanime AlaPas encore d'évaluation

- Chapitre 2 Systeme de Numérotation 4 - Nombre SignéDocument9 pagesChapitre 2 Systeme de Numérotation 4 - Nombre SignéLeila BaPas encore d'évaluation

- Arithmétique BinaireDocument35 pagesArithmétique Binaireham douaaPas encore d'évaluation

- IntroductionDocument5 pagesIntroductionAhmed BelhadjPas encore d'évaluation

- Les Circuits CombinatoiresDocument8 pagesLes Circuits CombinatoiresRachid AllaliPas encore d'évaluation

- Chapitre 03 La ReprAsentation de L InformationDocument68 pagesChapitre 03 La ReprAsentation de L InformationNeila BerkanePas encore d'évaluation

- Nombres SignesDocument2 pagesNombres SignesMohamed MohamedPas encore d'évaluation

- Série D'exercices N°1 Operations Arithmétiques - CorrectionDocument3 pagesSérie D'exercices N°1 Operations Arithmétiques - CorrectionEllios EMAILPas encore d'évaluation

- Additionneur Binaire PDFDocument4 pagesAdditionneur Binaire PDFnabil abdaoui100% (1)

- (MATHS) Chapitre 1 - NumérationDocument5 pages(MATHS) Chapitre 1 - Numérationsio-montaPas encore d'évaluation

- Cours Circuit Combinatoire PDFDocument125 pagesCours Circuit Combinatoire PDFDãdį DØ100% (1)

- Chapitre2 S1Document56 pagesChapitre2 S1LMH SaadPas encore d'évaluation

- Operation ArithmètiqueDocument5 pagesOperation ArithmètiqueAhmed BelhadjPas encore d'évaluation

- INF1500: Logique Des Systèmes NumériquesDocument48 pagesINF1500: Logique Des Systèmes Numériquesyoutube youtubePas encore d'évaluation

- 01 - Logique CombinatoireDocument34 pages01 - Logique CombinatoireouissemPas encore d'évaluation

- Chapitre 3 Les Systemes CombinatoiresDocument16 pagesChapitre 3 Les Systemes CombinatoiresOussama EljaafariPas encore d'évaluation

- Algo Cours2Document22 pagesAlgo Cours2Mohamed SelmaniPas encore d'évaluation

- Cours L'electronique Analogique Et DigitaleDocument35 pagesCours L'electronique Analogique Et DigitaleMartinezPas encore d'évaluation

- CI ConbinatoireDocument18 pagesCI ConbinatoireHayet BechedliPas encore d'évaluation

- Arithmétique BinaireDocument4 pagesArithmétique BinaireBalayira BakaryPas encore d'évaluation

- Architecture Des Ordinateur Semaine02Document24 pagesArchitecture Des Ordinateur Semaine02Martin LéonardPas encore d'évaluation

- 2-Entiers Relatifs Et RéelsDocument5 pages2-Entiers Relatifs Et Réelsenzod1604Pas encore d'évaluation

- ch2 Representation-InformationDocument7 pagesch2 Representation-InformationAMEL REBBOUCHEPas encore d'évaluation

- Doss Tech Dess Ensemble Principal2013 A3Document1 pageDoss Tech Dess Ensemble Principal2013 A3Nejib JallouliPas encore d'évaluation

- Dossier Technique Sess Principale2010Document6 pagesDossier Technique Sess Principale2010Nejib JallouliPas encore d'évaluation

- D-T Cadreuse 2018Document2 pagesD-T Cadreuse 2018Nejib JallouliPas encore d'évaluation

- DC1 DT 4ST 2016 2017Document4 pagesDC1 DT 4ST 2016 2017Nejib JallouliPas encore d'évaluation

- DC1 3st DT 2014Document3 pagesDC1 3st DT 2014Nejib JallouliPas encore d'évaluation

- Nom Et PrénomDocument4 pagesNom Et PrénomNejib JallouliPas encore d'évaluation

- TP-A42 FinDocument24 pagesTP-A42 FinNejib JallouliPas encore d'évaluation

- ElevDocument12 pagesElevNejib JallouliPas encore d'évaluation

- DC1 3st DR 2014Document5 pagesDC1 3st DR 2014Nejib JallouliPas encore d'évaluation

- TP-B11 FinDocument9 pagesTP-B11 FinNejib JallouliPas encore d'évaluation

- ds1 3st 2012Document5 pagesds1 3st 2012Nejib JallouliPas encore d'évaluation

- RappelDocument6 pagesRappelNejib JallouliPas encore d'évaluation

- Circuit ÉlecDocument82 pagesCircuit ÉlecNejib JallouliPas encore d'évaluation

- FICHE DE PREPARATION Et de DéroulementDocument3 pagesFICHE DE PREPARATION Et de DéroulementNejib JallouliPas encore d'évaluation

- CHAPITRE C1 Act C1 A3corrigéDocument2 pagesCHAPITRE C1 Act C1 A3corrigéNejib JallouliPas encore d'évaluation

- Formation MikropascalDocument69 pagesFormation MikropascalNejib JallouliPas encore d'évaluation

- ElevDocument15 pagesElevNejib JallouliPas encore d'évaluation

- ProfDocument15 pagesProfNejib JallouliPas encore d'évaluation

- Les Automates ProgrammablesDocument64 pagesLes Automates ProgrammablesNejib JallouliPas encore d'évaluation

- Exercice D'évaluationDocument5 pagesExercice D'évaluationNejib JallouliPas encore d'évaluation

- Fiche de Pre Et de DerDocument3 pagesFiche de Pre Et de DerNejib JallouliPas encore d'évaluation

- Sujet 63Document2 pagesSujet 63Nejib JallouliPas encore d'évaluation

- Moteur A Courant ContinuDocument79 pagesMoteur A Courant ContinuNejib JallouliPas encore d'évaluation

- Sujet 24Document2 pagesSujet 24Nejib JallouliPas encore d'évaluation

- Système TriphaséDocument11 pagesSystème TriphaséNejib JallouliPas encore d'évaluation

- Sujet 83Document2 pagesSujet 83Nejib JallouliPas encore d'évaluation

- Sujet 74Document2 pagesSujet 74Nejib JallouliPas encore d'évaluation

- Sujet 33Document2 pagesSujet 33Nejib JallouliPas encore d'évaluation

- Sujet 34Document3 pagesSujet 34Nejib JallouliPas encore d'évaluation

- Sujet 13Document3 pagesSujet 13Nejib JallouliPas encore d'évaluation

- Devoir Maison N 4: ExerciceDocument2 pagesDevoir Maison N 4: ExerciceMoumouni ZongoPas encore d'évaluation

- Epreuve Externe 2017Document36 pagesEpreuve Externe 2017David RouxhetPas encore d'évaluation

- Cour 123Document4 pagesCour 123Imad EddinePas encore d'évaluation

- 2exercices EncodagesDocument3 pages2exercices EncodageswikiamazPas encore d'évaluation

- Remediation Calculs BLDocument9 pagesRemediation Calculs BLEsther wanying176Pas encore d'évaluation

- Casio pb1000frDocument232 pagesCasio pb1000frhamid rabdanePas encore d'évaluation

- Des Exercices de Series Numeriques Et AlphanumeriquesDocument107 pagesDes Exercices de Series Numeriques Et AlphanumeriquesKouame parfait BrouPas encore d'évaluation

- Lista Functiilor in Engleza Corespunzatoare Celor in FrancezaDocument12 pagesLista Functiilor in Engleza Corespunzatoare Celor in FrancezaVladCristina-IonelaPas encore d'évaluation

- 4 FractionsDocument30 pages4 FractionsLuc Thierry RamarjaonaPas encore d'évaluation

- Chap 03 - Synthèse Des Systèmes CombinatoiresDocument6 pagesChap 03 - Synthèse Des Systèmes CombinatoiresBenakli IdirPas encore d'évaluation

- 1 - 2020-06-10 06 - 52 - 05 - PLAN de LEçONDocument4 pages1 - 2020-06-10 06 - 52 - 05 - PLAN de LEçONAlcide IsraëlPas encore d'évaluation

- Picbille Partie 2Document22 pagesPicbille Partie 2Jeanne DugatPas encore d'évaluation

- TP N°5 WordDocument2 pagesTP N°5 WordAmine OUKHOUYAPas encore d'évaluation

- Révision Algo Et Complexité 28 Juin 2011Document70 pagesRévision Algo Et Complexité 28 Juin 2011Med Nour Elhak JouiniPas encore d'évaluation

- DC6 3siDocument3 pagesDC6 3siMmeSameh Ben NasrPas encore d'évaluation

- Chap2 Algèbre de BooleDocument11 pagesChap2 Algèbre de BoolealbanPas encore d'évaluation

- Devoir de Maison N°1 2ndeDocument2 pagesDevoir de Maison N°1 2ndeSarahPas encore d'évaluation

- CodageDocument7 pagesCodageLaurent MondonPas encore d'évaluation

- Exercices 4emeDocument23 pagesExercices 4emediopnafissatou546Pas encore d'évaluation

- c1 Formule Taylor Th-Exo-Corr 20 21Document44 pagesc1 Formule Taylor Th-Exo-Corr 20 21Mamadou Moustapha NdiayePas encore d'évaluation

- Forum 447473 1Document2 pagesForum 447473 1qry qgqrghPas encore d'évaluation

- Corrigé EMD Du 9 Juin 2011Document4 pagesCorrigé EMD Du 9 Juin 2011yfdydudPas encore d'évaluation

- Fractions RationnellesDocument6 pagesFractions RationnellesR-winPas encore d'évaluation

- Equations de RecurrencesDocument28 pagesEquations de RecurrencesOkono WilfriedPas encore d'évaluation

- BFEM Mathématiques 2012 - SunudaaraDocument3 pagesBFEM Mathématiques 2012 - SunudaaraAhmadou Gueule SallPas encore d'évaluation

- Cha1 Crypto Prelim MathsDocument33 pagesCha1 Crypto Prelim MathsYousra ZchPas encore d'évaluation