Académique Documents

Professionnel Documents

Culture Documents

Plds PDF

Transféré par

Mohamed Ali AsriTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Plds PDF

Transféré par

Mohamed Ali AsriDroits d'auteur :

Formats disponibles

LES CIRCUITS

LOGIQUES

PROGRAMMABLES

M. Philippe LETENNEUR – Lycée Julliot de la Morandière

GRANVILLE

Les Circuits Logiques Programmables (P.L.D.)

SOMMAIRE

I. PRÉSENTATION DE LA LOGIQUE PROGRAMMÉE. ..............................................

..............................................33

II LA CLASSIFICATION DES PLDS................................

PLDS ................................................................

............................................

............3

3

II.1 Liste de toutes les familles de P.L.D. ................................................................

...............................................................................

............... 3

II.2 Résumé graphique des familles de P.L.D.................................

................................................................

........................................

........ 5

III LES PALS (PROGRAMMABLE ARRAY LOGIC) ....................................................

....................................................66

III.1 La symbolisation et la représentation.................................

représentation. ................................................................

............................................

............ 6

III.2 Les différentes structures. ................................................................

..............................................................................................

.............................. 7

III.2.1 Structure générale. ...............................................................................................................7

III.2.2 Combinatoire.........................................................................................................................8

III.2.3 Séquentielle. ..........................................................................................................................9

III.2.4 Les versatiles. .....................................................................................................................10

III.3 Les références des P.A.L. ................................................................

..............................................................................................

.............................. 12

III.4 La duplication de P.A.L. et le bit de sécurité. ...............................................................

............................................................... 13

IV LES C.P.L.D.S (COMPLEX PROGRAMMABLE LOGIC DEVICE).........................

DEVICE).........................14

14

V LES F.P.G.A.S (FIELDS PROGRAMMABLE GATE ARRAY).................................

ARRAY).................................15

15

VI LES OUTILS DE DÉVELOPPEMENTS.................................

DÉVELOPPEMENTS. ................................................................

................................16

16

VI.1 Le système de développement.................................

développement. ................................................................

.....................................................

..................... 16

VI.2 Description général de la chaîne des outils utilisés pour mettre au point des circuits

logiques programmables. ................................................................

................................................................................................

.....................................

..... 20

VI.2.1 Pour les PALs. ....................................................................................................................20

VI.2.1.1 Le programmateur...........................................................................................................20

VI.2.1.2 Schéma fonctionnel d'un outil de développement de PAL. ........................................20

VI.2.2 Pour les CPLDs et FPGAs.................................

FPGAs.................................................................

..........................................................

.......................... 21

VI.2.2.1 Schéma fonctionnel d'un outil de développement de FPGA /CPLD...........................21

VII) LEXIQUE ................................................................

................................................................................................

...........................................

...........22

22

VIII) BIBLIOGRAPHIE ................................................................

..............................................................................................

..............................23

23

IX) ILLUSTRATIONS . ................................................................

..............................................................................................

..............................23

23

S.T.S. GRANVILLE Philippe LETENNEUR page 2

Les Circuits Logiques Programmables (P.L.D.)

I. Présentation de la Logique Programmée.

Actuellement les Objets Techniques (O.T.) utilisent de plus en plus la logique

programmée (µP, Mémoires, µC, ...). Ces structures ont besoin de s'interfacer entre

elles. Elles utilisent généralement pour réaliser ces interfaces des fonctions à base

de fonctions logiques élémentaires, compteurs, registres , .... Le nombre de circuits

nécessaires pour remplir ces fonctions peut devenir très vite important.

Pour diminuer les coûts de fabrication, de développement et de maintenance,

les fabricants de circuits intégrés ont donné naissance aux Circuits Logique

Programmable ou encore P.L.D. (Programmable

Programmable Logic Device).

Device

Ces circuits sont capables pour un O.T. de réaliser plusieurs fonctions

logiques dans un seul circuit. Si ces fonctions étaient réalisées à base circuits de

logique classique, il en faudrait plusieurs circuits.

Un autre avantage, l'évolution des fonctions d'un l'O.T. s'effectue par

programmation comparée à une solution classique où il faut refaire un circuit

imprimé si on veut modifier le fonctionnement.

II La classification des P.L.D.

II.1 Liste de toutes les familles de P.L.D.

Les constructeurs de P.L.D. se livrent entre eux à une guerre commerciale et

sur les appellations, ce qui explique la difficulté à établir la classification des P.L.D.

La plus ancienne et la plus connue est certainement la famille des P.A.L. Le

nom a été donné par la société M.M.I (Fusion depuis avec A.M.D.), c'est une

appellation déposée, comme Walkman pour Sony ou Réfrigérateur pour Frigidaire.

* P.A.L. signifie Programmable Array Logic,

Logic c'est à dire réseau logique

programmable. La programmation de ces circuits s'effectue par destruction

de fusibles. Une fois programmés on ne peut plus les effacer. On distingue

deux sous familles:

- Les P.A.L. combinatoires ou P.A.L. simples. Ils sont constitués de

fonctions de logique combinatoire.

- Les P.A.L. à registres ou F.P.L.S. Field Programmable Logic

Séquencer pour séquenceur logique programmable. Ils sont constitués

de logique combinatoire et séquentielle (Registre).

S.T.S. GRANVILLE Philippe LETENNEUR page 3

Les Circuits Logiques Programmables (P.L.D.)

* Les P.A.L. effaçables: E.P.L.D.

Les E.P.L.D. Ce qui signifie Erasable Programmable Logic Device,

Device c'est à

dire circuit logique programmable et effasçable et qui sont aux P.A.L. ce que

sont les U.V.P.R.OM. aux P.R.O.M. Les E.P.L.D. peuvent être effacés par U.V.

ou électriquement. Ils sont encore appelés P.A.L. CMOS.

CMOS

* Les G.A.L.

Les G.A.L. Ce qui signifie Generic Array Logic ou encore réseau logique

générique ce qui veut dire pas grand chose mais qui sont aux P.A.L. ce que

sont les E.E.P.R.O.M aux P.R.O.M. Le nom de G.A.L. a été déposé par

LATTICE SEMICONDUCTOR. Leur fonctionnement est identique aux P.A.L.

CMOS ils sont programmables et effaçables électriquement.

CMOS,

* Les C.P.L.D.

Les C.P.L.D. Ce qui signifie Complex Programmable Logic Device. Device Ces

circuits sont composés de plusieurs P.A.L.s élémentaires (Par exemple

l’équivalent de P.A.L.s 22V10) reliés entre-eux par une zone d’interconnexion.

Grâce à cette architecture, ils permettent d’atteindre des vitesses de

fonctionnement élevées (plusieurs centaine de Mhz).

* Les L.C.A. & F.P.G.A. à anti-fusible.

- Les L.C.A. Ce qui signifie Logic Cell Array ou encore réseau de cellules

logiques. Ces circuits sont composés de blocs logiques élémentaires de 2000

à 10000 portes que l'utilisateur peut interconnecter.

- Les F.P.G.A. à anti fusibles sont identiques aux L.C.A sauf qu'ils permettent

une plus grande intégration de portes et ils ne sont pas effaçables

électriquement. Le nom anti-fusible vient de la programmation des

connexions qui s'effectue par fermeture de circuits, comparé aux fusibles où

l'on ouvre les circuits.

S.T.S. GRANVILLE Philippe LETENNEUR page 4

Les Circuits Logiques Programmables (P.L.D.)

II.2 Résumé graphique des familles de P.L.D.

P.L.D.

Circuit Logique

Programmable

P.A.L

&

F.P.L.S.

P.A.L. à

Fusibles

Bipolaires

P.A.L. CMOS

Effaçable

Electriquement

G.A.L.

Effaçable

Electriquement

P.A.L.

Effaçable aux

U.V.

C.P.L.D.

L.C.A.

F.P.G.A.

à anti fusible

S.T.S. GRANVILLE Philippe LETENNEUR page 5

Les Circuits Logiques Programmables (P.L.D.)

III Les P.A.L. (Programmable Array Logic)

L'invention des P.A.L. date d'une vingtaine d'années, ce sont les ingénieurs

de chez M.M.I qui ont eu l'idée d'utiliser la technologie des fusibles.

La programmation s’effectue par destruction de fusible (un fusible détruit

équivaut à un circuit ouvert), voir schéma ci-dessous.

I1 et I2 représentent des entrées (I:Input).

O représente une sortie (O:Output).

A partir de cette structure de base il va être possible de réaliser de

nombreuses fonctions logiques. La programmation va constituer à détruire les

fusibles pour obtenir les fonctions désirées, en sachant que lors de l'achat d'un

P.A.L. tous les fusibles sont vierges ou pas détruits.

III.1 La symbolisation et la représentation.

La représentation schématique de la précédente structure demande

beaucoup d'espace pour représenter un P.A.L. en entier. Les industriels ont adopté

une autre représentation voir ci-dessous.

a: Porte ET à 3 entrées.

b: Porte ET à 3 entrées représentation P.A.L. les croix représentent les

fusibles intacts.

c: Représentation de la structure interne d’un P.A.L..

P.A.L.

S.T.S. GRANVILLE Philippe LETENNEUR page 6

Les Circuits Logiques Programmables (P.L.D.)

Exemple: Représentation d'un Ou Exclusif.

I1 + I2 = I1 . I2 + I1 . I2

Cette équation se représente de la façon suivante:

III.2 Les différentes structures.

III.2.1 Structure générale.

Tout P.A.L. est constitué :

- D'entrées (Input): I1 à In avec 8<n<20.

- De sorties (Output) Ou d’entrées / sorties (I/O) de type Totem Pôle ou Trois Etats :

O1 à On ou IO1 à IOn (2<n<15).

On peut trouver aussi:

- Une entrée d'horloge (Clock): Clk ou Clock.

- Une entrée de validation des sorties trois états: OE (Output Enable) ou Enable.

- Une entrée de remise à zéro des registres: RESET.

D'un point de vue fonctionnel un P.A.L. est constitué d'une zone d'entrée de

fusibles ou matrice de programmation et une structure de sortie non

programmable déterminant le type de circuit voir schéma ci-dessous.

I1 IO1

Zone

de fusibles

ou Structure

matrice de de Sortie

programmation

In IOn

Clock

Reset

OE

S.T.S. GRANVILLE Philippe LETENNEUR page 7

Les Circuits Logiques Programmables (P.L.D.)

Symbolisation normalisée :

Clock

Reset

OE

I1 IO1

In IOn

Remarque: Sur un schéma comportant un P.A.L.,

P.A.L. on doit écrire les équations

qui relient les entrées aux sorties ou le nom du document contenant les équations

du P.A.L.

Dans l'exemple au paragraphe III.1, la programmation du Ou Exclusif était

facilement réalisable, ce n'est pas toujours le cas. C'est pourquoi il existe un grand

nombre de P.A.L. utilisant des structures de sorties différentes. On peut distinguer

trois types de structures de base:

- Combinatoire.

- Séquentielle.

- Versatile.

III.2.2 Combinatoire.

Il existe trois types:

- H -> (High) Porte ET suivit d'une Porte OU. Sortie active à l'état haut.

- L -> (Low) Porte ET suivit d'une Porte NON OU. Sortie active à l'état bas.

- C -> (Combinée) programmable en type H ou L.

S.T.S. GRANVILLE Philippe LETENNEUR page 8

Les Circuits Logiques Programmables (P.L.D.)

III.2.3 Séquentielle.

Il existe trois types:

- R -> (Register): Registre. Ces circuits sont composés de bascule D. Les

sorties des bascules sont de type trois états contrôlées par un signal de

validation Enable ou OE, et une horloge est commune à toutes les bascules

(clock).

- X -> (Register Or Exclusif): Ou Exclusif et Registre.

- RA -> (Register Asynchron): Registre asynchrone.

S.T.S. GRANVILLE Philippe LETENNEUR page 9

Les Circuits Logiques Programmables (P.L.D.)

Les structures de sorties sont beaucoup plus évoluées par rapport aux autres

P.A.L. elles se rapprochent des P.A.L. de type versatile.

P.A.L.,

Elles peuvent prendre quatre configurations suivant les valeurs de AP et AR.

III.2.4 Les versatiles.

Ce type de structure représente les P.A.L. les plus évoluées, car les

structures de sorties dite versatile proposent quatre configurations possibles.

suivant les valeurs de S0 et S1.

Ce qui donne:

S.T.S. GRANVILLE Philippe LETENNEUR page 10

Les Circuits Logiques Programmables (P.L.D.)

Le plus célèbre des circuits versatile est certainement le P.A.L. 22V10 de chez

AMD. Il permet d'émuler pratiquement tout les autres types de P.A.L. et dispose

d'un circuit de remise à zéro des registres à la mise sous tension du circuit.

Schéma interne d’un PAL 22V10 : ( GAL22V10 Lattice Semiconductor).

S.T.S. GRANVILLE Philippe LETENNEUR page 11

Les Circuits Logiques Programmables (P.L.D.)

III.3 Les références des P.A.L.

Les constructeurs de P.A.L. ont standardisé le marquage des P.A.L.

Chez AMD:

Chez TEXAS INSTRUMENTS:

S.T.S. GRANVILLE Philippe LETENNEUR page 12

Les Circuits Logiques Programmables (P.L.D.)

Exemples:

Un PAL 16L8 : 16 entrées maximum, 8 sorties maximum et il dispose d’une

structure de sortie active sur niveau bas.

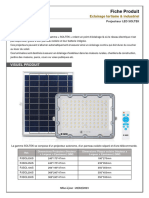

PAL Entrées Sorties Entrées / Registres Fonction

max max Sorties

Input (I) Output (O) (I/O)

10H8 10 8 AND OR

12H6 12 6 AND OR

14H4 14 4 AND OR

16H2 16 2 AND OR

10L8 10 8 AND OR INVERT

12L6 12 6 AND OR INVERT

14L4 14 4 AND OR INVERT

16L2 16 2 AND OR INVERT

16C1 16 1 AND-OR /AND OR-INVERT

16L8 10 8 6 AND OR INVERT

16R8 8 8 8 AND OR INVERT-REGISTER

16R6 8 8 2 6 AND OR INVERT-REGISTER

16R4 8 8 4 4 AND OR INVERT-REGISTER

16X4 8 8 4 4 AND OR INVERT-XOR-REGISTER

16A4 8 8 4 4 AND CARRY-OR-XOR-INVERT-REGISTER

III.4 La duplication de P.A.L. et le bit de sécurité.

Un circuit P.A.L. peut être dupliqué comme une EPROM, pour le protéger les

constructeurs ont ajouté un bit dit de sécurité. Si ce bit est programmé alors le

circuit ne peut plus être relu.

S.T.S. GRANVILLE Philippe LETENNEUR page 13

Les Circuits Logiques Programmables (P.L.D.)

IV LES C.P.L.D.s (Complex

(Complex Programmable Logic Device).

Ces circuits ont une capacité en nombre de portes et en possibilités de

configuration très supérieure à celle des PALs. Leurs architectures sont basées sur

celles des PALS. Un CPLD c’est l’équivalent de plusieurs PALs mis dans le même

circuit associé à une zone d’interconnexion. Le nombres de portes peut varier entre

100 et 100 000 portes logiques et entre 16 et 1000 bascules voir plus.

Structure générale d’un CPLD.

Macro cellules

composées de:

- une zône de portes

Bloc logiques

logique - une bascule

Zone

d’inter-

connexion

Bloc Bloc

logique logique

Exemple de CPLD le circuit Isp1016 de LATTICE :

S.T.S. GRANVILLE Philippe LETENNEUR page 14

Les Circuits Logiques Programmables (P.L.D.)

V LES F.P.G.A.s (Fields Programmable Gate Array).

les FPGAs à la différence des CPLDs sont assimilables à des

A.S.I.C. (Application

Application Specific Integrated Circuit) programmables par l’utilisateur.

La puissance de ces circuits est telle qu’ils peuvent être composés de plusieurs

milliers voire millions de portes logiques et de bascules. Les dernières générations

de FPGA intègrent même de la mémoire vive (RAM). Les deux plus grands

constructeurs de FPGA sont XILINX et ALTERA.

Ils sont composés de blocs logiques élémentaires (plusieurs milliers de portes) qui

peuvent être interconnectés.

De plus en plus les capacités des CPLDs et des FPGAs se rapprochent. Le principal

critère de choix entre les deux familles est la vitesse de fonctionnement. En effet

les CPLDs acceptent des fréquences de fonctionnement beaucoup plus élevées

que les FPGAs.

S.T.S. GRANVILLE Philippe LETENNEUR page 15

Les Circuits Logiques Programmables (P.L.D.)

VI Les outils de développements.

Ils sont composés en général de deux outils:

- Le système de développement.

- Le programmateur.

VI.1 Le système de développement.

Ces systèmes produisent une table représentant les fusibles à détruire en

fonction des équations logiques, diagramme d'états et tables de vérités écrit dans

le langage propre au système, c'est le rôle du compilateur ou synthétiseur.

La description du fonctionnement des circuits peut se faire de plusieurs

façons, soit :

- Par un schéma à base de fonctions logique élémentaires (Portes

ET,OU,NON, … bascules, compteurs, registres à décalages).

COMPTEUR

U10

U15

1 2

CLK CLK D

67 1 2

Q3 Q3

IB11 U16 3

OB11

C 1 2

Q2 Q2

U17 4

OB11

B 1 2

Q1 Q1

U18 5

OB11

A 1 2

Q0 Q0

6

OB11

COMPTEURP

U19 U21 U23

D 1 2 1

3 1 2

ROUGE1

INV 2 78

U20 OB11

A 1 NAND2

U22 U24

B 2 4 1

3 1 2

C ROUGE2

3 2 13

OB11

NAND3 NAND2

D

U25

B 1 U26 U30

3 1 U28

C 2 3 1 2 1 2

VERT1

2 76

NAND2 INV OB11

NAND2

U27 U31

1 U29

3 1 2 1 2

D VERT2

2 11

INV OB11

NAND2

U32 U37

A 1 2 1

U35

INV 2

5 1 2

B ORANGE1

3 77

OB11

C 4

U36

AND4

1 2

ORANGE2

12

OB11

U38

1

B 2

5

C 3

D 4

AND4

S.T.S. GRANVILLE Philippe LETENNEUR page 16

Les Circuits Logiques Programmables (P.L.D.)

- En utilisant un langage de description comportementale H.D.L. (H Hardware

Description Language). Les plus anciens sont PALASM,

PALASM ORCAD/PLD et le

plus connu et utilisé est sans conteste ABEL (utilisé par la plus part des

systèmes de développements). Enfin les langages dit de haut niveau, VHDL

(V

Very high speed Hardware Description Language) et VERILOG sont en

général utilisés pour des circuits complexes. Le langage VHDL est très utilisé

en Europe.

ORCAD/PLD :

|GAL16V8 in:(A15,A14,A13,A11,A10),

| io:(RAM0,RAM1,RAM2,RAM3,ROM,INTER1,INTER2,INTER3)

|

| RAM0 = (A15' & A11' & A10')'

| RAM1 = (A15' & A11' & A10)'

| RAM2 = (A15' & A11 & A10')'

| RAM3 = (A15' & A11 & A10)'

| ROM = (A15 & A14 & A13)'

| INTER1 = (A15 & A14' & A13')'

| INTER2 = (A15 & A14 & A13)'

| INTER3 = (A15 & A14 & A13')'

ABEL :

module tp1

title 'decodage d adresse'

declarations

A15,A14,A13,A11,A10 pin;

RAM0, RAM1, RAM2, RAM3, ROM, INTER1, INTER2, INTER3 pin istype 'com';

x =.X.;

adresse = [A15,A14,A13,x, A11,A10,x,x, x,x,x,x, x,x,x,x];

equations

!RAM0 = (adresse >=^h0000) & (adresse <=^h03FF);

!RAM1 = (adresse >=^h0400) & (adresse <=^h07FF);

!RAM2 = (adresse >=^h0800) & (adresse <=^h0BFF);

!RAM3 = (adresse >=^h0C00) & (adresse <=^h0FFF);

!ROM = (adresse >=^hE000) & (adresse <=^hFFFF);

!INTER1 = (adresse >=^h8000) & (adresse <=^h8001);

!INTER2 = (adresse >=^hA000) & (adresse <=^hA001);

!INTER3 = (adresse >=^hC000) & (adresse <=^hC00F);

end;

VHDL :

-- VHDL created by OrCAD Express

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.numeric_std.all;

ENTITY DECODAGE is

PORT (

A15, A14, A13, A12, A11, A10 : IN STD_LOGIC;

RAM0 : OUT STD_LOGIC;

RAM1 : OUT STD_LOGIC;

RAM2 : OUT STD_LOGIC;

RAM3 : OUT STD_LOGIC;

ROM : OUT STD_LOGIC;

INTER1 : OUT STD_LOGIC;

INTER2 : OUT STD_LOGIC;

INTER3 : OUT STD_LOGIC);

END DECODAGE;

ARCHITECTURE behavior OF DECODAGE IS

SIGNAL ADRESSE: STD_LOGIC_VECTOR(15 downto 0);

BEGIN

ADRESSE <= A15 & A14 & A13 & A12 & A11 & A10 & "----------";

ROM <= '0' when (ADRESSE >= x"E000") and (ADRESSE <= x"FFFF") else '1';

RAM0 <= '0' when (ADRESSE >= x"0000") and (ADRESSE <= x"03FF") else '1';

RAM1 <= '0' when (ADRESSE >= x"0400") and (ADRESSE <= x"07FF") else '1';

RAM2 <= '0' when (ADRESSE >= x"0800") and (ADRESSE <= x"0CFF") else '1';

RAM3 <= '0' when (ADRESSE >= x"0D00") and (ADRESSE <= x"0FFF") else '1';

INTER1 <= '0' when (ADRESSE >= x"8000") and (ADRESSE <= x"8001") else '1';

INTER2 <= '0' when (ADRESSE >= x"A000") and (ADRESSE <= x"A001") else '1';

INTER3 <= '0' when (ADRESSE >= x"C000") and (ADRESSE <= x"C00F") else '1';

END behavior;

S.T.S. GRANVILLE Philippe LETENNEUR page 17

Les Circuits Logiques Programmables (P.L.D.)

- En utilisant un schéma et des descriptions en langage de haut niveau de

type VHDL. U2

BCD_D(3:0) HEX(3:0) LED(6:0) LED_D(6:0)

hex2led

F_INPUT U3 -

U0 U1

BCD_C(3:0) HEX(3:0) LED(6:0) LED_C(6:0)

F_PATTERN F_PATTERN CLK BCD_D(3:0)

GATE BCD_C(3:0) hex2led

RESET RESET GATE GATE

-

BCD_B(3:0) U4

END_RESET

START START END_RESET RESET BCD_A(3:0) BCD_B(3:0) HEX(3:0) LED(6:0) LED_B(6:0)

CNT_BCD

CONTROL hex2led

U5

BCD_A(3:0) HEX(3:0) LED(6:0) LED_A(6:0)

Description schématique

du module de comptage hex2led

Description VHDL du

module de décodage

7 segments

BCD_D(3:0)

CLK CLK BCD_C(3:0)

RESET RESET

BCD_B(3:0)

U1 U2 U3 U4

CLK FULL CLK FULL CLK FULL CLK FULL

ENABLE Q(3:0) ENABLE Q(3:0) ENABLE Q(3:0) ENABLE Q(3:0) BCD_A(3:0)

RESET RESET RESET RESET

cnt_4b cnt_4b cnt_4b cnt_4b

library IEEE;

U0 U5 U6

use IEEE.std_logic_1164.all;

A0 A0 A0

Y Y Y

GATE A1 A1 A1 entity hex2led is

and2 and2 and2

port (

HEX: in STD_LOGIC_VECTOR (3 downto 0);

LED: out STD_LOGIC_VECTOR (6 downto 0)

);

Description VHDL du end hex2led;

module de comptage BCD

--}} End of automatically maintained section

architecture hex2led of hex2led is

library IEEE; -- segment encoding

use IEEE.std_logic_1164.all; -- 0

use IEEE.STD_LOGIC_UNSIGNED.all; -- ---

-- 5 | | 1

entity CNT_4B is -- --- <- 6

port ( -- 4 | | 2

CLK: in STD_LOGIC; -- ---

RESET: in STD_LOGIC; -- 3

ENABLE: in STD_LOGIC; begin

FULL: out STD_LOGIC; with HEX select

Q: out STD_LOGIC_VECTOR (3 downto 0) LED <= "1111001" when "0001", --1

); "0100100" when "0010", --2

end CNT_4B; "0110000" when "0011", --3

"0011001" when "0100", --4

architecture CNT_4B of CNT_4B is "0010010" when "0101", --5

signal Qint: STD_LOGIC_VECTOR(3 downto 0); "0000010" when "0110", --6

"1111000" when "0111", --7

begin "0000000" when "1000", --8

process (CLK, RESET) "0010000" when "1001", --9

begin "0001000" when "1010", --A

if RESET = '1' then "0000011" when "1011", --b

Qint <= (others => '0'); "1000110" when "1100", --C

elsif CLK='1' and CLK'event then "0100001" when "1101", --d

if ENABLE = '1' then "0000110" when "1110", --E

if Qint = 9 then "0001110" when "1111", --F

Qint <= (others => '0'); "1000000" when others; --0

else end hex2led;

Qint <= Qint + 1;

end if;

end if;

end if;

end process;

Q <= Qint;

FULL <= '1' when (Qint = 9) else '0';

end CNT_4B;

S.T.S. GRANVILLE Philippe LETENNEUR page 18

Les Circuits Logiques Programmables (P.L.D.)

Par l’utilisation de graphes d’états. (FSM : Flow States Machines)

RESET='1'

START='0'

GATE <= '0';

IDLE END_RESET <= '1';

START='0' START='1'

START='1'

GATE <= '0'; GATE <= '1';

END_CYCLE END_RESET <= '0'; OPEN_GATE END_RESET <= '0';

Quelques systèmes de développements connus :

1) Synario de LATTICE SEMI CONDUCTOR (Schéma, ABEL et VHDL)

WEB : http://www.latticesemi.com

2) Express d’ORCAD (Schémas, VHDL)

WEB : http://www.orcad.com/ pour la France WEB : http://www.alsdesign.fr/

3) ViewPLD de VIEW LOGIC (schémas, ABEL et VHDL)

WEB : http://www.viewlogic.com

4) StateCad de STATECAD (Graphes d’états).

WEB : http://www.statecad.com/

5) Active VHDL de ALDEC (Schémas, VHDL et Graphes d’états ).

WEB : http://www.aldec.com/

6) Warp de CYPRESS (VHDL et graphes d’états).

WEB : http://www.cypress.com/

7) MaxPlus d’ALTERA (Schémas, VHDL et Graphes d’états).

WEB : http://www.altera.com/

8) Foundation d’XILINX (Schémas, VHDL et Graphes d’états).

WEB : http://www.xilinx.com/

S.T.S. GRANVILLE Philippe LETENNEUR page 19

Les Circuits Logiques Programmables (P.L.D.)

VI.2 Description générale de la chaîne des outils utilisés pour mettre au point

des circuits logiques programmables.

VI.2.1 Pour les PALs.

Ces outils peuvent posséder d'un simulateur logique pour vérifier la

programmation du circuit.

Le format de la table des fusibles à détruire a été normalisé par les

constructeurs de circuits pour qu'il puisse être accepté par le programmateur de

P.A.L. c'est le format JEDEC (Format de fichier de programmation des circuits

P.A.L.,

logiques : image des fusibles à griller).

VI.2.1.1 Le programmateur.

Il permet de:

- Vérifier la virginité du circuit.

- Lire le fichier au format JEDEC.

- Programmer le circuit.

- Vérifier la programmation.

Il se présente souvent par une carte à insérer dans le PC reliée à un support

de programmation et d'un logiciel permettant le dialogue entre lui et l'utilisateur.

VI.2.1.2 Schéma fonctionnel d'un outil de développement de PAL.

Equation, table de vérité ,

Diagramme d'état

exprimé dans le langage du

Utilisateur

système de dév eloppeme nt

Circuit PAL

Compte re ndu programmé

de compilation

Directive et

compte

rendu de

Compilateur simulation

Simulateur

Système de

développeme nt

Programmateur

Fichier au format JEDEC

S.T.S. GRANVILLE Philippe LETENNEUR page 20

Les Circuits Logiques Programmables (P.L.D.)

VI.2.2 Pour les CPLDs et FPGAs.

VI.2.2.1 Schéma fonctionnel d'un outil de développement de FPGA /CPLD.

COMPTEUR

U10

U15

1 2

CLK CLK D

67 1 2

Q3 Q3

IB11 U16 3

OB11

C 1 2

Q2 Q2

U17 4

OB11

B 1 2

Q1 Q1

RESET='1'

U18 5

OB11

A 1 2

Q0

OB11

6

Q0

library IEEE; START='0'

COMPTEURP

U19 U21 U23

use IEEE.std_logic_1164.all;

D 1 2 1

A

INV

U20

2

3 1

OB11

2

78

ROUGE1

use

GATE <= '0';

1 NAND2

C

2 4 1

U22

3 1

U24

2

ROUGE2

IEEE.STD_LOGIC_UNSIGNED.all; IDLE END_RESET <= '1';

3 2 13

OB11

NAND3 NAND2

D

B 1

U25

U26 U30

entity CNT_4B is

3 1 U28

C 2

NAND2

2

3 1

INV

2 1

OB11

2

76

VERT1

port ( START='0' START='1'

NAND2

1

U27

U29

U31 CLK: in STD_LOGIC;

3 1 2 1 2

D 2

NAND2

INV OB11

11

VERT2

RESET: in STD_LOGIC;

U32 U37

A 1 2 1

U35 ENABLE: in STD_LOGIC;

START='1'

INV 2

5 1 2

ORANGE1

B 3 77

OB11

C 4

AND4

1

U36

2 FULL: out STD_LOGIC; GATE <= '0'; GATE <= '1';

OPEN_GATE END_RESET <= '0';

ORANGE2

12

END_CYCLE END_RESET <= '0';

OB11

B

1

2

U38

Q: out STD_LOGIC_VECTOR

C

D

3

4

5

(3 downto 0)

AND4 );

Entrée syntaxique

Entrée schématique langages: Diagramme d’états

- VHDL

VHDL

VHDL VHDL

Vérification des erreurs: Simulation

de schéma et de syntaxe STILMULI ou comportementale

TESTBENCH

VHDL

VITAL, VHDL

SYNTHETISEUR

Simulation après

Il convertit en fonction du ciruit STILMULI ou synthèse

SYNTHETISEURS CONNUS: cible (CPLD ou FPGA: suivant le TESTBENCH

modèle choisit) le projet en

-FPGA Expres (Synosys).

(Synosys). portes logiques et bascules de

-EXEMPLAR (Exemplar). bases.

-SYNPLICITY (Synplicity).

(Synplicity). De plus on peut lui spécifier

des contraites de technologies,

par exemple la vitesse de

fonctionnement

EDIF, XNF

Outils de placement et VITAL, VHDL, SDF

routage interne au Optimisation

circuit. Cet outil est Placement / routage Simulation temporelle

propre à chaque dans le circuit choisit STILMULI ou

fabriquant TESTBENCH

JEDEC

La programmation du circuit

peut se faire soit:

- En utilisant un CIRCUIT

programmateur. FPGA

- En téléchragement le code CPLD

JEDEC directement sur

l’objet technique (JTAG ou

ISP)

S.T.S. GRANVILLE Philippe LETENNEUR page 21

Les Circuits Logiques Programmables (P.L.D.)

VII) Lexique

ASIC (Application Specific Integrated Circuit) : Circuit non programmable

configuré lors de sa fabrication pour une application spécifique.

CPLD (Complex

(Complex Programmable Logic Device) : Désigne des PLD ayant un haut

niveau d'intégration.

EEPROM ou E2PROM (Electrical

(Electrical Erasable Programmable Read-Only

Read-Only Memory) :

Mémoire programmable à lecture seule, effaçable électriquement.

EPLD (Erasable

(Erasable Programmable Logic Device) : Circuits logiques

reprogrammables.

EPROM (Erasable

(Erasable Programmable Read-Only

Read-Only Memory) : Mémoire programmable à

lecture seule, effaçable par ultraviolets.

FPGA (Forecasting

(Forecasting Programmable Gate Array) : Réseau de portes programmables

à la demande. Technologie qui utilise des circuits encapsulés comportant des

réseaux de portes logiques non reliées : l’utilisateur réalise les interconnexions

nécessaires par programmation.

FPLS (Field Programmable Logic Sequencer) : Ancien nom donné aux PAL à

registres.

GAL (Generic

(Generic Array Logic) : Circuits logiques PAL reprogrammables à technologie

CMOS.

ISP (In System Programmable) : Circuit que l’on peut programmer (et donc effacer)

même lorsqu’il est en place sur l’application.

JEDEC : Format de fichier de programmation des circuits logiques (image des

fusibles à griller).

LSI (Large Scale Integration) : Intégration à grande échelle : circuits regroupant

quelques centaines à quelques milliers de portes logiques (CI de télécommande,

décodeur de code à barre, etc …).

MSI (Medium

(Medium Scale Integration) : Intégration à échelle moyenne : circuits

regroupant quelques dizaines de portes logiques (décodeurs, multiplexeurs,

bascules …).

PAL (Programmable Array Logic) : Circuits logiques programmables dans

lesquels seules les fonctions ET sont programmables, les fonctions OU ne le sont

pas.

PAL CMOS ou PAL EECMOS : c.f. GAL.

PLD (Programmable Logic Device) : Famille des circuits programmables qui

comprend les PAL, GAL, EPLD et FPGA.

SSI (Small Scale Integration) : Intégration à petite échelle : circuit ne regroupant

que quelques portes logiques (fonctions de base des séries 74 ou 4000).

VHDL : Langage de programmation utilisé pour programmer les PLD.

VLSI (Very

(Very Large Scale Integration) : Intégration à très grande échelle : circuits

regroupant quelques dizaines de milliers de portes logiques (microprocesseurs …).

S.T.S. GRANVILLE Philippe LETENNEUR page 22

Les Circuits Logiques Programmables (P.L.D.)

VIII) BIBLIOGRAPHIE

• Circuits logiques programmables (Christian Tavernier - DUNOD, Paris, 1996)

• Guide du technicien en électronique (C. Cimelli, R. Bourgeron - HACHETTE,

Paris, 1995)

• Electronique Radio-Plans

Radio-Plans (n° 567).

• Elektor (n° 197, novembre 1994).

• Lexique électronique (P. Roussel - NATHAN, 1996).

IX) ILLUSTRATIONS .

• Circuits logiques programmables (Christian Tavernier - DUNOD, Paris, 1996)

• Guide du technicien en électronique (C. Cimelli, R. Bourgeron - HACHETTE,

Paris, 1995)

• Document réalisés par L.P. AMPERE - 13010 MARSEILLE

S.T.S. GRANVILLE Philippe LETENNEUR page 23

Vous aimerez peut-être aussi

- Cours Math ÉDocument168 pagesCours Math ÉRoland AgasroPas encore d'évaluation

- Les Régions périphériques: Défi au développement du QuébecD'EverandLes Régions périphériques: Défi au développement du QuébecPas encore d'évaluation

- MRAP : Internet, Enjeu de La Lutte Contre Le Racisme (2009)Document154 pagesMRAP : Internet, Enjeu de La Lutte Contre Le Racisme (2009)maxoufixPas encore d'évaluation

- L' inclusion en éducation physique: Notions théoriques et applications pédagogiquesD'EverandL' inclusion en éducation physique: Notions théoriques et applications pédagogiquesPas encore d'évaluation

- Le Calcul Sismique-10!10!5005Document69 pagesLe Calcul Sismique-10!10!5005sosatlantique100% (1)

- Les Villes moyennes au Québec: Leur place dans le système socio-spatialD'EverandLes Villes moyennes au Québec: Leur place dans le système socio-spatialPas encore d'évaluation

- Stage TechnicienDocument25 pagesStage TechnicienKhaled Ben YoussefPas encore d'évaluation

- Conventions collectives et changements environnementauxD'EverandConventions collectives et changements environnementauxPas encore d'évaluation

- Lecture de Plans - EPDocument35 pagesLecture de Plans - EPAllamine Oum'sPas encore d'évaluation

- Captivate 5 HelpDocument287 pagesCaptivate 5 HelpBertrand GiraultPas encore d'évaluation

- Table Des MatiéresDocument4 pagesTable Des Matiéresyassiroutisket2Pas encore d'évaluation

- Robots financiers et I.A.: Aspects pratiques et éthiquesD'EverandRobots financiers et I.A.: Aspects pratiques et éthiquesPas encore d'évaluation

- 2513 Chantier01Document50 pages2513 Chantier01izaryu27Pas encore d'évaluation

- Ecabosseuse de Cacao - Part - OneDocument58 pagesEcabosseuse de Cacao - Part - Onewatsop100% (1)

- Cours UML 2021Document55 pagesCours UML 2021Jean didierPas encore d'évaluation

- Rapport DoloDocument46 pagesRapport Dolopatrickbruelofficiel246Pas encore d'évaluation

- Analyse Publicitaire - Anne-Sophie BarietyDocument175 pagesAnalyse Publicitaire - Anne-Sophie Barietyelric NoirtinPas encore d'évaluation

- Deviens Un Ninja Avec AngularDocument339 pagesDeviens Un Ninja Avec AngularmikarPas encore d'évaluation

- Deviens Un Ninja Avec AngularDocument329 pagesDeviens Un Ninja Avec AngularElvis Thomme100% (3)

- AbaqusDocument41 pagesAbaqusauto31000100% (1)

- Entretien Routier Finale RevuDocument44 pagesEntretien Routier Finale RevuArnold NdipatchouPas encore d'évaluation

- Pour La Sauveagrde de BéjaiaDocument58 pagesPour La Sauveagrde de BéjaiasiliaPas encore d'évaluation

- Mémoire Meister 07Document106 pagesMémoire Meister 07mohamed el amine brahimiPas encore d'évaluation

- Apprendre À Programmer Avec Visual BasicDocument139 pagesApprendre À Programmer Avec Visual BasicZidan DidiPas encore d'évaluation

- Manuel PerceuseDocument32 pagesManuel Perceusesebti abassiPas encore d'évaluation

- SimuDocument110 pagesSimuRajita EconomistePas encore d'évaluation

- LivreProteus_VisualDesigner_ArduinoDocument155 pagesLivreProteus_VisualDesigner_ArduinofabPas encore d'évaluation

- Memoire FinaleeeDocument49 pagesMemoire FinaleeeGodefroy Cheumani TcheumaniPas encore d'évaluation

- Dessein Technologie PF3Document155 pagesDessein Technologie PF3Oncle Link100% (1)

- Rapport de Stage AUTO MESKiDocument15 pagesRapport de Stage AUTO MESKiOussama AzrakPas encore d'évaluation

- Deviens Un Ninja Avec Angular2Document231 pagesDeviens Un Ninja Avec Angular2Gnaore HervePas encore d'évaluation

- Soudage Tech InstallDocument24 pagesSoudage Tech InstallwatsopPas encore d'évaluation

- Le BIM Dans L'environnement D'un BETDocument102 pagesLe BIM Dans L'environnement D'un BETMohamed El AmriPas encore d'évaluation

- Alfresco - Manuel de L'utilisateurDocument56 pagesAlfresco - Manuel de L'utilisateurAdel ChelbaPas encore d'évaluation

- (MFE ISCAE) Mise en Place Compta Analytique Cas COSUMARDocument94 pages(MFE ISCAE) Mise en Place Compta Analytique Cas COSUMARAmine GamerPas encore d'évaluation

- Formatux MaformationlinuxDocument680 pagesFormatux MaformationlinuxGilles DELMAS100% (1)

- Objets Connectés - PR Tonye 2 Septembre 2021Document422 pagesObjets Connectés - PR Tonye 2 Septembre 2021Pamela brenda BitomPas encore d'évaluation

- Deviens Un Ninja Avec Angular ExtraitDocument86 pagesDeviens Un Ninja Avec Angular Extraitmodo siméonPas encore d'évaluation

- Cours IGL 2020-2021Document44 pagesCours IGL 2020-2021ulrich djofangPas encore d'évaluation

- CoursDocument271 pagesCoursLY SENGHUOPas encore d'évaluation

- Eva BENROS, Solvabilité II Calibrage Des MCR-SCR Dans Le Contexte QIS4 SOLVENCY I & II + QIS 1.2.3.4 PDFDocument104 pagesEva BENROS, Solvabilité II Calibrage Des MCR-SCR Dans Le Contexte QIS4 SOLVENCY I & II + QIS 1.2.3.4 PDFHillel Adem BelaidiPas encore d'évaluation

- Guide Cad WorkDocument40 pagesGuide Cad WorkyouçPas encore d'évaluation

- RapportDocument8 pagesRapportYamboua Tonga Christabelle100% (1)

- Mulumba Tfe Final OkDocument94 pagesMulumba Tfe Final OkKelvin Kasongo Ngoy NsengaPas encore d'évaluation

- Projet D'integration 10 RenewDocument35 pagesProjet D'integration 10 Renewarthurngassa029Pas encore d'évaluation

- Securite Incendie Milieu ResidentielDocument122 pagesSecurite Incendie Milieu ResidentielCheikh ThiamPas encore d'évaluation

- SQLDocument65 pagesSQLenaifos3dPas encore d'évaluation

- Cahier de Calculs BCPST - CorrigésDocument97 pagesCahier de Calculs BCPST - Corrigéslarissakouame2001Pas encore d'évaluation

- Cahier de CalculsDocument189 pagesCahier de CalculsLouis MilletPas encore d'évaluation

- Cahier de l'Enseignant 2022 - 2 ASC TechnologieDocument87 pagesCahier de l'Enseignant 2022 - 2 ASC TechnologieMouad ElmekaouiPas encore d'évaluation

- Syllabus 2022 - 2023Document65 pagesSyllabus 2022 - 2023exaucemakizodila60Pas encore d'évaluation

- A31008 M2701 N121 1 7719 - 13 03 2017 - FR - FRDocument88 pagesA31008 M2701 N121 1 7719 - 13 03 2017 - FR - FRfadili.act2iPas encore d'évaluation

- Deviens Un Ninja Avec Angular Extrait PDFDocument87 pagesDeviens Un Ninja Avec Angular Extrait PDFAristote EngudiPas encore d'évaluation

- M Audio Axiom 25 Guide de L Utilisateur FR 35821 PDFDocument49 pagesM Audio Axiom 25 Guide de L Utilisateur FR 35821 PDFRitok PikoPas encore d'évaluation

- Rapport Fibre OptiqueDocument33 pagesRapport Fibre OptiqueSafoine GabtniPas encore d'évaluation

- COVADIS v16 - 2 - Dessin Assisté PDFDocument628 pagesCOVADIS v16 - 2 - Dessin Assisté PDFNacer KorichiPas encore d'évaluation

- Devoir 6Document7 pagesDevoir 6Mohamed Ali AsriPas encore d'évaluation

- Termes TechniquesDocument16 pagesTermes TechniquesMohamed Ali AsriPas encore d'évaluation

- 13729613Document14 pages13729613Mohamed Ali AsriPas encore d'évaluation

- TD 2 en Informatique: Tableaux Et PointeursDocument1 pageTD 2 en Informatique: Tableaux Et PointeursMohamed Ali AsriPas encore d'évaluation

- TD 2 en Informatique: Tableaux Et PointeursDocument1 pageTD 2 en Informatique: Tableaux Et PointeursMohamed Ali AsriPas encore d'évaluation

- Commande Des MachinesDocument35 pagesCommande Des MachinesYoussouf DjeriouePas encore d'évaluation

- Email CrakingDocument2 pagesEmail CrakingMohamed Ali AsriPas encore d'évaluation

- Traitement Du Signal - EtudiantDocument50 pagesTraitement Du Signal - Etudiantsakiina100% (1)

- TP 2 AnalysetemporelledessystemeslineairesDocument3 pagesTP 2 AnalysetemporelledessystemeslineairesMohamed Ali AsriPas encore d'évaluation

- Cours2 PDFDocument32 pagesCours2 PDFfarfarfifi3Pas encore d'évaluation

- MSi B550M PRO A520M PRO Carte Mère Manuel Utilisateur - Manuels +Document1 pageMSi B550M PRO A520M PRO Carte Mère Manuel Utilisateur - Manuels +lilouPas encore d'évaluation

- Chapitre 2 (Influence de La Température Sur La Position Du Niveau de Fermi)Document13 pagesChapitre 2 (Influence de La Température Sur La Position Du Niveau de Fermi)MEed E-tanPas encore d'évaluation

- CSC4536Document50 pagesCSC4536Guency Alven Rhocky KOMBILAPas encore d'évaluation

- ELE1409 H23 Cours 9Document43 pagesELE1409 H23 Cours 9jeefmatanga5Pas encore d'évaluation

- TP Simulation Numerique 2Document8 pagesTP Simulation Numerique 2cazesnoePas encore d'évaluation

- Accessoires Coffrets de RelayageDocument6 pagesAccessoires Coffrets de RelayageAhmed IdrissiPas encore d'évaluation

- TP02 - Amplis SpéciauxDocument3 pagesTP02 - Amplis SpéciauxOUIAME NKHILI0% (1)

- Transistors A Effet de Champ Cours 03Document13 pagesTransistors A Effet de Champ Cours 03ato ndongo fabricePas encore d'évaluation

- Commande Électronique Des Moteurs 3Document268 pagesCommande Électronique Des Moteurs 3MaGMaaa WKPas encore d'évaluation

- Alimentations À Découpage Convertisseurs À ResonnanceDocument336 pagesAlimentations À Découpage Convertisseurs À Resonnancesabinebach100% (2)

- Analog FiltreDocument13 pagesAnalog FiltreMhamdi AhlemPas encore d'évaluation

- Liste Nettoyage CuisineDocument4 pagesListe Nettoyage CuisineLaurence DEBERGHPas encore d'évaluation

- Principes de Base IrDocument40 pagesPrincipes de Base IrBellarguet Faouzi fawziPas encore d'évaluation

- CAME ZA3 NoticeDocument12 pagesCAME ZA3 NoticeNicolas BuissonPas encore d'évaluation

- Implantation FD20CDocument25 pagesImplantation FD20CJonas Denis NGAMBAPas encore d'évaluation

- FP - Ingelec - Luminaires - Led - Projecteurs Soltek - VaDocument5 pagesFP - Ingelec - Luminaires - Led - Projecteurs Soltek - VaYoussef AcherquiPas encore d'évaluation

- Fiche Technique Onduleur - SG250HXDocument2 pagesFiche Technique Onduleur - SG250HXkaltoum elmnaouarPas encore d'évaluation

- Energieplus-Lesite - Be-Détecteurs de Mouvement Et de Présenceabsence EclairageDocument11 pagesEnergieplus-Lesite - Be-Détecteurs de Mouvement Et de Présenceabsence EclairageAMINE AIT ABBOUPas encore d'évaluation

- Compte Rendu TP Archetecture Des Systèmes EmbarquésDocument19 pagesCompte Rendu TP Archetecture Des Systèmes EmbarquésKhawla KholitaPas encore d'évaluation

- Fonctions Analogiques Non LinéairesDocument14 pagesFonctions Analogiques Non LinéairesLôvë PärkërPas encore d'évaluation

- Notice Ducati 6203Document8 pagesNotice Ducati 6203Piergean JclaPas encore d'évaluation

- TH T2191 HtakhedmitDocument190 pagesTH T2191 HtakhedmitabdellahmorPas encore d'évaluation

- Binder 5Document51 pagesBinder 5Nas simPas encore d'évaluation

- Catalogue Export 2020 FR - 906130100 - BDDocument44 pagesCatalogue Export 2020 FR - 906130100 - BDam nouhaPas encore d'évaluation

- RTHF RLC SVX021D FR 0520Document60 pagesRTHF RLC SVX021D FR 0520matusiwamariaPas encore d'évaluation

- Final 2005Document7 pagesFinal 2005Abd Errezak ChahoubPas encore d'évaluation

- TP EP SimulationDocument6 pagesTP EP SimulationAhmad WhabiPas encore d'évaluation

- MV Instrument Transformers FR PDFDocument34 pagesMV Instrument Transformers FR PDFjeanPas encore d'évaluation

- Manual Mesa de Mezcla YamahaDocument37 pagesManual Mesa de Mezcla Yamahamjjuezi01Pas encore d'évaluation

- 1elec - L3-S1-2022Document46 pages1elec - L3-S1-2022zerrouki hichamPas encore d'évaluation