Académique Documents

Professionnel Documents

Culture Documents

Chapitre 1

Transféré par

eyaCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Chapitre 1

Transféré par

eyaDroits d'auteur :

Formats disponibles

CHAPITRE 1 ISET DE SOUSSE

LOGIQUE COMBINATOIRE

LOGIQUE SEQUENTIELLE

I. INTRODUCTION

Nous pouvons distinguer deux types de systèmes logiques.

- Logique combinatoire dont le niveau logique des sorties dépond uniquement du niveau

logique des entrées.

E1

Logique cablée combinatoire S = f (E1, ……, En)

En

- Logique séquentielle dont le niveau logique des sorties ne dépond plus uniquement du

niveau logique des entrées mais aussi d’impulsions donnés par une horloge.

E1

Logique cablée séquentielle S = f (E1, ……, En, temps)

En

II. LES FONCTIONS LOGIQUES COMBINATOIRES DE BASE

Fonction OUI NON ET OU NAND NOR

Equation S=a S a S = a.b S= a + b S a b S a .b

a S a S a b S a b S a b S a b S

0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1

T. vérité 1 1 1 0 0 1 0 0 1 1 0 1 1 0 1 0

1 0 0 1 0 1 1 0 1 1 0 0

1 1 1 1 1 1 1 1 0 1 1 0

Symbole

logique

KHEMIRI WAHIBA -1- 2019/2020

CHAPITRE 1 ISET DE SOUSSE

III. LES CIRCUITS SEQUENTIELS FONDAMENTAUX

IV.1. La bascule RS

La bascule RS est le circuit séquentiel le plus simple. Sa fonction consiste à mémoriser une

information fugitive. La bascule possède deux états stables et constitue ainsi une mémoire

binaire élémentaire.

Dans les systèmes automatisés la bascule peut stocker provisoirement une information binaire,

autoriser ou interdire le déroulement de certaines fonctions, ect…

IV.1.1. Principe de la bascule RS

La bascule RS dispose de deux entrées R et S et de deux sorties Q et Q

S : entrée de mémorisation ou de déclenchement ou d’activatiin ou de mise à 1.

R : entrée d’effacement ou de désactivation ou de mise à zéro.

R Qn

S Qn

IV.1.2. Table de vérité

En technologie électronique (TTL, CMOS,…) l’état de sortie n’existe que si l’élément qui

l’élabore est sous tension.L’expression de la sortie de la mémoire X dont le niveau logique 1

matérialise la commande x1 est donnée par l’équation d’un organe monostable :

X X1 X 0 X

Qn 1 S R Qn

Table de vérité simplifiée

R S Qn+1

0 0 Qn

0 1 1

1 0 0

1 1 -

KHEMIRI WAHIBA -2- 2019/2020

CHAPITRE 1 ISET DE SOUSSE

V. LES MEMOIRES

V.1. Définition

Les mémoires sont des systèmes qui une fois mis à l'état 1 ("s" pour set ) restent dans cet état

tant que l'on ne leur donne pas l'ordre de se mettre à l'état 0 ( "r" pour reset ).

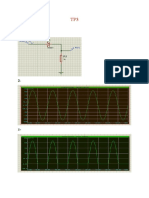

Chronogramme:

s (1) 1

0

r (0)1

0

M 1

0

étapes A B C D A

Table de vérité :

Etapes s r M

A 0 0 0

B 1 0 1

C 0 0 1

D 0 1 0

Remarque : Dans les étapes A et C, les valeurs des entrées sont les mêmes alors que la sortie M

a deux valeurs différentes. Une mémoire est donc un système séquentiel.

V.2. Les differents types de mémoires

V.2.1. Les mémoires à arrêt prioritaire.

C'est une mémoire qui se met à l'état 0 si "s" et "r" sont simultanément à l'état 1

Chronogramme :

s (1) 1

0

r ( 0 )1

0

M 1

0

étapes A B C D E D A B E B C D A

KHEMIRI WAHIBA -3- 2019/2020

CHAPITRE 1 ISET DE SOUSSE

Table de vérité :

Etapes s r M

A 0 0 0

B 1 0 1

C 0 0 1

D 0 1 0

E 1 1 0

- Mémoire à arrêt prioritaire :

s M

r

V.2.2. Les mémoires sans priorité.

C'est une mémoire qui reste dans son état si "s" et "r" sont simultanément à l'état 1.

(comme dans le cas ou s = r = 0 )

Chronogramme :

s (1) 1

0

r ( 0 )1

0

M 1

0

étapes A B C D E D A B F B C D A

Table de vérité :

Etapes s r M

A 0 0 0

B 1 0 1

C 0 0 1

D 0 1 0

E 1 1 0

F 1 1 1

KHEMIRI WAHIBA -4- 2019/2020

CHAPITRE 1 ISET DE SOUSSE

Symbole de la mémoire sans priorité à deux sorties complémentaires : Quand r et s sont

simultanément à 1, M reste dans l'état en cours.

s M

r M

V.2.3. Les mémoires à marche prioritaire

C'est une mémoire qui se met à l'état 1 si "s" et "r" sont simultanément à l'état 1.

Chronogramme :

s (1) 1

0

r ( 0 )1

0

M 1

0

étapes A B C D E D A B E B C D A

Table de vérité :

Etapes s r M

A 0 0 0

B 1 0 1

C 0 0 1

D 0 1 0

E 1 1 1

Symbole de la mémoire à marche prioritaire :

s M

r

KHEMIRI WAHIBA -5- 2019/2020

Vous aimerez peut-être aussi

- Ds Filtre de Hartley 19 Nov 18 PDFDocument4 pagesDs Filtre de Hartley 19 Nov 18 PDFYassir Sadiq Elfilali80% (5)

- Logique 120320084503 Phpapp02Document14 pagesLogique 120320084503 Phpapp02AFADPas encore d'évaluation

- PDF LogicseqDocument25 pagesPDF LogicseqYassine FalahPas encore d'évaluation

- Les Circuits SéquentielsDocument14 pagesLes Circuits SéquentielsJOHNE JKPas encore d'évaluation

- 08m - Moires (Corrig - )Document4 pages08m - Moires (Corrig - )Kamel TayahiPas encore d'évaluation

- tp3 VHDLDocument9 pagestp3 VHDLabdousewagerPas encore d'évaluation

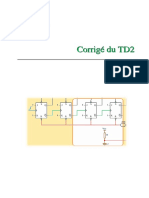

- Tp2 ElectroDocument9 pagesTp2 ElectroKarim FathiPas encore d'évaluation

- Fiche de TD Sur Les Circuit LogiqueDocument3 pagesFiche de TD Sur Les Circuit LogiqueDokoloPas encore d'évaluation

- TD4 SolutionsDocument7 pagesTD4 SolutionsSafae EL HAIRACHPas encore d'évaluation

- TD2 Num - 20 21Document2 pagesTD2 Num - 20 21Simo FidoudiPas encore d'évaluation

- CM 7 - Synthèse SynchroneDocument60 pagesCM 7 - Synthèse Synchroneyacine kessalPas encore d'évaluation

- TP ApiDocument9 pagesTP Apibenesseddik.abdessalemePas encore d'évaluation

- TP4 Elec IMENE MAJDADocument10 pagesTP4 Elec IMENE MAJDAabdenour02800Pas encore d'évaluation

- Compte Rendu - ElectroDocument29 pagesCompte Rendu - ElectroJamil KarimPas encore d'évaluation

- 2nde C Physique Seq6Document3 pages2nde C Physique Seq6SuffoPas encore d'évaluation

- Chapitre 2 4 Synthese Des CompteursDocument10 pagesChapitre 2 4 Synthese Des CompteursIddir YuderPas encore d'évaluation

- Aide 1Document12 pagesAide 1nadaPas encore d'évaluation

- Chapitre III La Logique SéquentielleDocument26 pagesChapitre III La Logique SéquentielleGaya MhbPas encore d'évaluation

- 2-Devoir de Controle N1-1AS-2021-FLBDocument2 pages2-Devoir de Controle N1-1AS-2021-FLBMed Aymen BensalemPas encore d'évaluation

- TD N°2: Algebre de Boole - Tableau de Karnaugh: I. Proprietes BinairesDocument2 pagesTD N°2: Algebre de Boole - Tableau de Karnaugh: I. Proprietes BinairesOtmane El FaihPas encore d'évaluation

- TP Du Circuits Séquentiels-1Document10 pagesTP Du Circuits Séquentiels-1abdo issaouiPas encore d'évaluation

- Représentation de L'information Et Architecture Des Machines Informatiques - Séquence 3Document7 pagesReprésentation de L'information Et Architecture Des Machines Informatiques - Séquence 3mn706412002Pas encore d'évaluation

- TP1 LogiqueDocument12 pagesTP1 LogiqueŘî Æđ100% (1)

- Serie n4 Corrigem 19 20Document13 pagesSerie n4 Corrigem 19 20asmaPas encore d'évaluation

- Merged 20200609 191118Document8 pagesMerged 20200609 191118Angeauden DidoPas encore d'évaluation

- Cours de Mécanique AppliquéeDocument6 pagesCours de Mécanique AppliquéePhilippe KANYIMBUPas encore d'évaluation

- TM Opérateurs LogiquesDocument4 pagesTM Opérateurs LogiquesJejbreakerPas encore d'évaluation

- Synthese Des Systemes Sequen Ficche CorDocument5 pagesSynthese Des Systemes Sequen Ficche CorNejib JallouliPas encore d'évaluation

- Correction 4567Document6 pagesCorrection 4567gaaloul ghaithPas encore d'évaluation

- BooleDocument6 pagesBooleredPas encore d'évaluation

- Chapitre II SLDocument10 pagesChapitre II SLYosr RannenPas encore d'évaluation

- Diagonalisation 2021Document13 pagesDiagonalisation 2021storieskalis23Pas encore d'évaluation

- Cours-NSI Premiere Circuits Et Logique BooleenneDocument6 pagesCours-NSI Premiere Circuits Et Logique Booleennemulk omarPas encore d'évaluation

- Chap4 - ANALYSE ET SYNTHESE DES - 2022Document10 pagesChap4 - ANALYSE ET SYNTHESE DES - 2022a.aitlmahfoud1492Pas encore d'évaluation

- TP 1Document4 pagesTP 1Otmane El FaihPas encore d'évaluation

- TP3 1GE CorrectionDocument4 pagesTP3 1GE CorrectionasmaPas encore d'évaluation

- TD N°5Document8 pagesTD N°5NotnowPas encore d'évaluation

- Combinatoire Et Bascules PDFDocument2 pagesCombinatoire Et Bascules PDFCHARLIE / شارليPas encore d'évaluation

- Corre Ction TD1 SuiteDocument5 pagesCorre Ction TD1 SuiteBeyaz ÇiçekPas encore d'évaluation

- Revisions Logique CombinatoireDocument20 pagesRevisions Logique CombinatoireJacques Gregoire100% (1)

- Revisions Logique CombinatoireDocument20 pagesRevisions Logique CombinatoireKamel Tayahi100% (1)

- Chapitre 1 Portes Logique Algeble BooleDocument19 pagesChapitre 1 Portes Logique Algeble BooleToniPas encore d'évaluation

- Revisions Logique CombinatoireDocument20 pagesRevisions Logique CombinatoireOthmane EL Badlaoui100% (1)

- Chapitre 2 Algebre de Boole Et Simplification2019 - 2020Document12 pagesChapitre 2 Algebre de Boole Et Simplification2019 - 2020Raya NePas encore d'évaluation

- Corrige Detaille Sm2 Td2Document11 pagesCorrige Detaille Sm2 Td2Tchonbe Albert TchonbePas encore d'évaluation

- 2 Analyse Machine EtatsDocument15 pages2 Analyse Machine EtatsMENANI ZineddinePas encore d'évaluation

- Corrigé TD2 CNDocument6 pagesCorrigé TD2 CNPapeCheikh SYLLAPas encore d'évaluation

- Corrig TD1 2Document5 pagesCorrig TD1 2Amine Aissaoui100% (1)

- TD Architecture Des Ordinateurs-2021-2022Document6 pagesTD Architecture Des Ordinateurs-2021-2022FabricePas encore d'évaluation

- TP3 Mux Et Demux 2023Document3 pagesTP3 Mux Et Demux 2023Bassmala BaraaPas encore d'évaluation

- Upload - Série D'exercices N°2-3tech-Systèmes Combinatoires-2013-2014 PDFDocument6 pagesUpload - Série D'exercices N°2-3tech-Systèmes Combinatoires-2013-2014 PDFyassine zitouniPas encore d'évaluation

- Compte RenduDocument10 pagesCompte Renduanis ben youssefPas encore d'évaluation

- DocumentDocument19 pagesDocumentmoulay abdallahPas encore d'évaluation

- Document EleveDocument13 pagesDocument EleveakremibechirPas encore d'évaluation

- Examen D'algèbre. L1S2. Licences PSI.: 1 Consignes (À Lire Absolument)Document9 pagesExamen D'algèbre. L1S2. Licences PSI.: 1 Consignes (À Lire Absolument)Nou RanPas encore d'évaluation

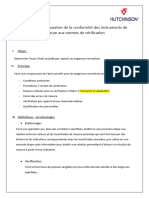

- Logigramme périodicité instrumentsDocument1 pageLogigramme périodicité instrumentseyaPas encore d'évaluation

- Fiche Periodicité A3Document5 pagesFiche Periodicité A3eyaPas encore d'évaluation

- Mise en Œuvre de La Fonction Métrologie Dans Le LaboratoireDocument11 pagesMise en Œuvre de La Fonction Métrologie Dans Le LaboratoireeyaPas encore d'évaluation

- Fiche Periodicité A3Document5 pagesFiche Periodicité A3eyaPas encore d'évaluation

- Fiche Periodicité A1Document6 pagesFiche Periodicité A1eyaPas encore d'évaluation

- Fiche Des GabaritsDocument16 pagesFiche Des GabaritseyaPas encore d'évaluation

- Procédure de détermination des intervalles de confirmation métrologique -2Document12 pagesProcédure de détermination des intervalles de confirmation métrologique -2eyaPas encore d'évaluation

- Évaluation Comparative de La Conformité Des Instruments de Mesure Aux Normes de Vérification (Récupération Automatique)Document4 pagesÉvaluation Comparative de La Conformité Des Instruments de Mesure Aux Normes de Vérification (Récupération Automatique)eyaPas encore d'évaluation

- Amdec IatfDocument34 pagesAmdec IatfeyaPas encore d'évaluation

- Chapitre 2Document9 pagesChapitre 2eyaPas encore d'évaluation

- TD 1Document2 pagesTD 1eyaPas encore d'évaluation

- Iso 13485 2016Document13 pagesIso 13485 2016eyaPas encore d'évaluation

- Mise en Œuvre de La Fonction Métrologie Dans Le LaboratoireDocument11 pagesMise en Œuvre de La Fonction Métrologie Dans Le LaboratoireeyaPas encore d'évaluation

- Classement Des InstrumentsDocument28 pagesClassement Des InstrumentseyaPas encore d'évaluation

- Check-List ISO 10012Document1 pageCheck-List ISO 10012eyaPas encore d'évaluation

- Optimisation de Vérification Des GabaritsDocument5 pagesOptimisation de Vérification Des GabaritseyaPas encore d'évaluation

- Constat de Vérification D'un Micromètre ExtérieurDocument2 pagesConstat de Vérification D'un Micromètre ExtérieureyaPas encore d'évaluation

- Chapitre1 HutchinsonDocument6 pagesChapitre1 HutchinsoneyaPas encore d'évaluation

- TP3 CorrectionDocument7 pagesTP3 CorrectioneyaPas encore d'évaluation

- Iso 7863 1984Document8 pagesIso 7863 1984eyaPas encore d'évaluation

- Rapport de Stage 02Document27 pagesRapport de Stage 02eyaPas encore d'évaluation

- Constat P.CDocument5 pagesConstat P.CeyaPas encore d'évaluation

- Calcul Répétabilité PCDocument2 pagesCalcul Répétabilité PCeyaPas encore d'évaluation

- Suite Chap2Document6 pagesSuite Chap2eyaPas encore d'évaluation

- Partie ThéoriqueDocument7 pagesPartie ThéoriqueeyaPas encore d'évaluation

- Fiche Danalyse Des RisquesDocument2 pagesFiche Danalyse Des RisqueseyaPas encore d'évaluation

- Concept GPS V2 2022Document88 pagesConcept GPS V2 2022eyaPas encore d'évaluation

- Job Interview Questionnaire1Document4 pagesJob Interview Questionnaire1eyaPas encore d'évaluation

- Travail Mini ProjetDocument3 pagesTravail Mini ProjeteyaPas encore d'évaluation

- 3 05 Annexe Exemple Complete de PADocument0 page3 05 Annexe Exemple Complete de PAhghfdtgfhdfhPas encore d'évaluation

- Exercices Maths TC International 6 1Document4 pagesExercices Maths TC International 6 1tamba vieux tolnoPas encore d'évaluation

- Chapitre - 2 CMNDocument71 pagesChapitre - 2 CMNZakariae ZâamounPas encore d'évaluation

- 4 Logique Sequentielle PDFDocument24 pages4 Logique Sequentielle PDFkhocinePas encore d'évaluation

- TD Mécanique Première PartieDocument4 pagesTD Mécanique Première Partieemmanuelmayala40Pas encore d'évaluation

- CHP 1-5 - DiaposDocument96 pagesCHP 1-5 - DiaposFabien LucienPas encore d'évaluation

- Activité P5 de Synthèse-PrévisionsDocument1 pageActivité P5 de Synthèse-PrévisionsOumaima Ben SaidPas encore d'évaluation

- Chap2-Types, Opérateurs Et ExpressionsDocument71 pagesChap2-Types, Opérateurs Et Expressionsm.azeroualPas encore d'évaluation

- Correction 22Document4 pagesCorrection 22Sofien RekikPas encore d'évaluation

- TheseDocument188 pagesTheseBilel LetaiefPas encore d'évaluation

- La Corrigé de Séries N°2 - 2022-2023 - Copie PDFDocument7 pagesLa Corrigé de Séries N°2 - 2022-2023 - Copie PDFIslam BenanibaPas encore d'évaluation

- Cours CompletDocument122 pagesCours CompletPFEPas encore d'évaluation

- C Revision Fonctions 22-23Document30 pagesC Revision Fonctions 22-23AbdelmalkPas encore d'évaluation

- Techniques de L'Ingénieur - Accéléromètres Inertiels PDFDocument8 pagesTechniques de L'Ingénieur - Accéléromètres Inertiels PDFdjouder nordinePas encore d'évaluation

- 7 - Série #1Document2 pages7 - Série #1Ghizlane KarimPas encore d'évaluation

- Mini Session PC 2022 02 02Document2 pagesMini Session PC 2022 02 02Youri NoghoPas encore d'évaluation

- Type D'argumentsDocument10 pagesType D'argumentsCharaf Adam LaasselPas encore d'évaluation

- Fascicules Dexercice de Mathématique 2ndS PDFDocument63 pagesFascicules Dexercice de Mathématique 2ndS PDFAlioune CodjoPas encore d'évaluation

- L'amortissement Du Matériel IndustrielDocument38 pagesL'amortissement Du Matériel Industrielbachir boukhalfaPas encore d'évaluation

- Assoudou: Generalites Sur Les Series Temporelles ET Ajustement TendancielDocument3 pagesAssoudou: Generalites Sur Les Series Temporelles ET Ajustement Tendancielآلا ءءPas encore d'évaluation

- CFM2007 1329Document6 pagesCFM2007 1329Saifeddine Ben SalemPas encore d'évaluation

- Serie2AN2 16-17Document2 pagesSerie2AN2 16-17Skander TmarPas encore d'évaluation

- Corrigé Point de Mire SEC 3 PDF Mathématiques Élémentaires Enseignement Des MathématiquesDocument1 pageCorrigé Point de Mire SEC 3 PDF Mathématiques Élémentaires Enseignement Des Mathématiquesloicbarbe09Pas encore d'évaluation

- 1-Cahier Cycle4 5e PDFDocument128 pages1-Cahier Cycle4 5e PDFkeybrrPas encore d'évaluation

- Cpa 1Document2 pagesCpa 1Kenneth KodjoPas encore d'évaluation

- Notions de Systemes Asservis PDFDocument80 pagesNotions de Systemes Asservis PDFSiéJustinDembelePas encore d'évaluation

- Etude de Systèmes ÉchantillonnéesDocument9 pagesEtude de Systèmes Échantillonnéessouaf.hedilPas encore d'évaluation

- Micro EconomieDocument45 pagesMicro Economiealexandre-assous-567Pas encore d'évaluation

- CHP 2Document50 pagesCHP 2azertyPas encore d'évaluation